EPI (European Processor Initiative), que visa criar processadores e aceleradores europeus de alto desempenho para servidores, sistemas HPC e veículos autônomos, concluiu com sucesso a primeira fase de desenvolvimento – CPUs codinome Rhea tornaram-se um passo mais perto da realidade. Seu lançamento está previsto para o final de 2022.

O consórcio EPI foi criado em 2018, e agora já inclui 28 empresas e organizações em 10 países da União Europeia. A EPU anunciou hoje o cumprimento das metas da primeira fase do projeto, que inclui três áreas principais de desenvolvimento: Processadores de Uso Geral (GPP), Aceleradores (EPAC) e SoC para veículos robóticos.

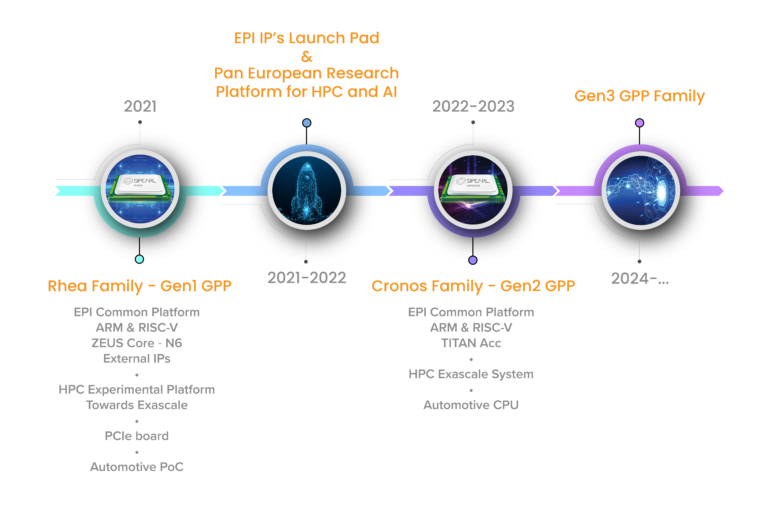

Planos da Iniciativa do Processador Europeu (Imagens: EPI)

A primeira área é liderada pelo SiPearl com o apoio da Atos. A empresa está criando um chip Rhea de 6 nm com núcleos Arm Neoverse V1. No entanto, isso é apenas parte do quadro geral – o chip receberá outros 29 blocos RISC-V diferentes, bem como uma interconexão NoC (Network-on-Chip) interna para conectar núcleos e vários subsistemas. Em geral, o chip já está operacional no nível RTL – o design completo está sendo validado em emuladores, mas já pode ser usado para criar software de sistema e aplicativo.

Rhea receberá controladores de memória compatíveis com HBM2E, para os quais o CEA preparou uma plataforma separada para validação. O Sistema de Gerenciamento de Segurança Autônomo (SMS) da ProvenRun será responsável pela proteção. A Universidade de Pisa desenvolveu um conjunto completo de blocos de criptografia IP para acelerar AES, ECC / ECDSA / ECIES / ECDH e SHA2 / SHA3. O Crypto Tile possui um armazenamento de chaves seguro, proteção contra ataques de canal lateral, suporte para criptografia pós-quântica (Cristais Kyber e Dilithium) e operação eficiente com chaves ultralongas, além de gerador de números aleatórios de hardware e interfaces AXI4 rápidas.

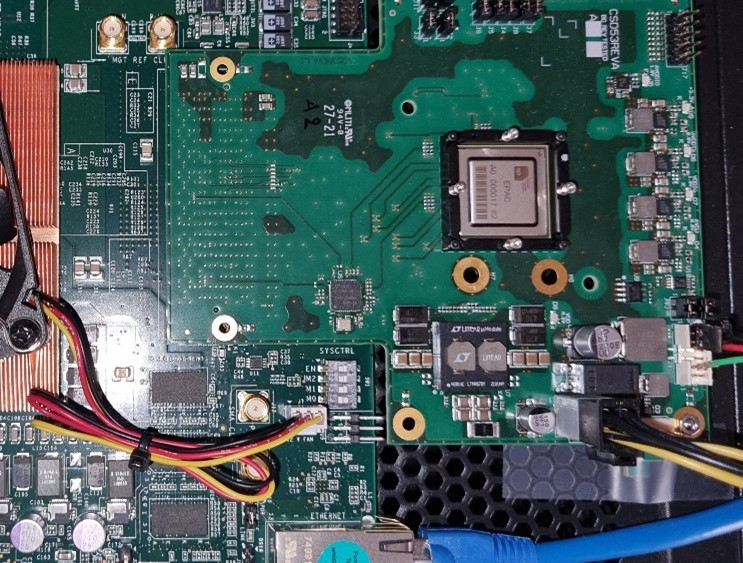

Primeiro lote de chips EPAC

Para um processador moderno, o fator de consumo de energia é muito importante, e aqui as universidades de Bolonha e Zurique deram uma grande contribuição, desenvolvendo um novo controlador de energia baseado em núcleos RISC-V. Ele usa algoritmos de aprendizado de máquina modernos para gerenciar SoCs de vários núcleos com mais eficiência. Os reguladores de tensão e a plataforma de referência para eles (baseada em FPGA até agora) foram projetados pela Atos e E4 Computer Engineering.

Protótipo de acelerador EPAC

A direção dos aceleradores é representada por chips EPAC 1.0 baseados em núcleos RISC-V e blocos IP de vários aceleradores especializados, cujas primeiras amostras foram lançadas neste outono. A placa de teste EPAC foi desenvolvida pela E4 Computer Engineering. O pré-teste mostra excelente capacidade de programação e compatibilidade. Agora estamos desenvolvendo e portando software e drivers.

Plataforma de teste para a nova plataforma de transporte autônomo europeia

Finalmente, a terceira filial do EPI, sob o patrocínio da Infineon, introduziu o conceito de uma plataforma de veículo autônomo baseada no BMW X5. É baseado em um SoC eHPC baseado em blocos de IP criados em outras áreas de trabalho do EPI. A plataforma inclui novas câmeras e sistemas de radar AI. É dada muita atenção à segurança – há conformidade com os requisitos do padrão ASIL D. A nova plataforma é modular e permite conectar chips Rhea e EPAC, aceleradores Kalray MPPA e FPGAs Menta eFPGA.

Em geral, os resultados da primeira fase do trabalho do EPI comprovam a possibilidade de cooperação entre um número tão sério de desenvolvedores. Os princípios básicos de operação foram estabelecidos e os primeiros protótipos viáveis de plataformas e blocos IP individuais foram criados. Ao mesmo tempo, todos eles foram criados pelas forças de empresas europeias e são amplamente baseados em soluções abertas, que a EPI pretende apoiar no futuro.