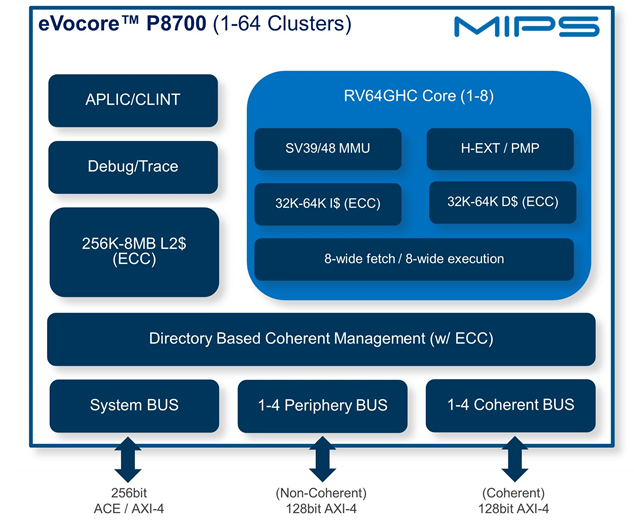

Os processadores com arquitetura MIPS ainda são usados em vários aplicativos, mas estão sendo ativamente substituídos em todos os lugares pelas arquiteturas Arm e, mais recentemente, pelo RISC-V. A própria MIPS Technologies, após inúmeros problemas, não pretende desenvolver e dar suporte às soluções MIPS (mas ainda está pronta para receber royalties pelas soluções existentes). A empresa mudou oficialmente para o RISC-V e anunciou recentemente o eVocore P8700, seu primeiro núcleo baseado nessa arquitetura.

Imagem: MIPS

O novo design fornece de 1 a 8 núcleos de computação com execução fora de ordem, unidos em complexos que variam em tamanho de 1 a 64 clusters (512 núcleos). Também é curioso que o SMT2 também seja suportado, o que não é muito típico, por exemplo, para processadores de alto desempenho baseados na arquitetura Arm. Isso na configuração máxima do cluster dá suporte para a execução simultânea de 1024 threads.

Fonte: MIPS

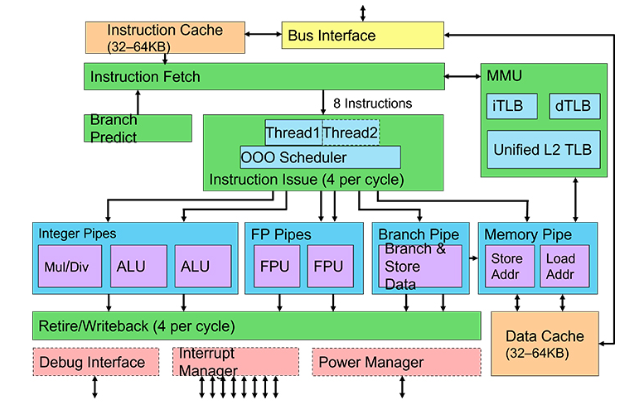

No coração do novo núcleo está um pipeline de 16 estágios e 8 instruções para atingir altas velocidades de clock. endereçamento de memória física de 48 bits é usado, ACE/AXI-4 de 256 bits é usado como um barramento do sistema; Opcionalmente, o processador baseado no P8700 pode ter barramentos AXI-4 adicionais de 128 bits para periféricos e coerência em configurações multicluster.

Dispositivo central eVocore P8700. Fonte: TechInsights

A novidade é caracterizada pela combinação de alto desempenho com eficiência energética; graças a isso, os desenvolvedores o direcionam principalmente para o mercado de veículos – para uso em sistemas de assistência ao motorista (ADAS) e em sistemas de piloto automático. Além disso, o eVocore P8700 pode ser usado como parte de processadores clássicos para servidores, sistemas de armazenamento e até mesmo sistemas HPC.

Imagem: MIPS

O novo núcleo está em conformidade com os padrões ASIL-D e contém ferramentas de diagnóstico integradas, para as quais é fornecido um barramento de monitoramento especial, que permite que o sistema se recupere rapidamente de uma falha, o que é extremamente importante para aplicações de transporte.

Processador EyeQ Ultra. Fonte: Mobileye See More

De acordo com o MIPS, o novo núcleo tem o maior desempenho single-threaded de sua classe. A Ventana Micro Systems, que também anunciou um núcleo RISC-V de desempenho para o processador Veyron V1, provavelmente pode argumentar contra essa afirmação. No entanto, o novo MIPS já foi licenciado pelo principal piloto automático e desenvolvedor do ADAS, Mobileye, para uso em chips EyeQ.

Deve-se notar também que existem outras implementações RISC-V no arsenal do MIPS, em particular o núcleo eVocore I8500, que não suporta execução fora de ordem de instruções, mas implementa SMT4, que fornece 2.048 threads em 512 -core cluster. Além disso, ambos os núcleos estão disponíveis através do programa Intel Pathfinder.