Quanto menores os transistores se tornam, mais fatores afetam seu desempenho. Como a IBM descobriu, o desempenho dos futuros transistores de porta circular e de canal nanopage variará acentuadamente dependendo da orientação dos cristais de silício dos quais são feitos.

Fonte da imagem: geração AI Kandinsky 3.0/avalanche noticias

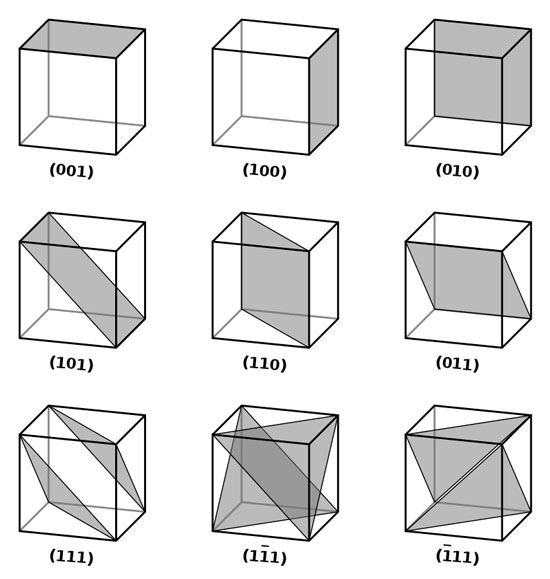

Sabe-se que uma rede cristalina é uma alternância que se repete infinitamente de combinações idênticas de átomos na estrutura de uma substância. Dependendo da escolha da direção e localização do corte que passa pelo cristal, certas combinações de átomos e ligações entre eles aparecerão na face resultante. Os cientistas descobriram há muito tempo que cada face tem seu próprio buraco e condutividade eletrônica. Contanto que os transistores fossem grandes, isso poderia ser ignorado. No entanto, à medida que avançamos para transistores de 2nm e componentes menores, a orientação dos cristais de silício já tem um impacto perceptível no seu desempenho.

Índices de Miller. Fonte da imagem: Wikipédia

Tradicionalmente, na indústria de fabricação de semicondutores, o substrato de silício era cortado no plano 001 do chamado índice de Miller. Neste plano, a condutividade eletrônica é mais alta e tem maior impacto no desempenho do chip. A condutividade do furo é significativamente menor, mas até agora isso não era crítico. No caso de criar um transistor de silício no corte 110, a condutividade do furo aumenta acentuadamente e a condutividade eletrônica diminui ligeiramente. O efeito geral é positivo e terá implicações no desempenho de futuros transistores.

Disposição dos átomos em uma célula da rede cristalina de silício

Em princípio, os transistores com portas localizadas verticalmente – FinFETs, que já são produzidos há muito tempo e se tornaram comuns, possuem canais justamente no corte 110. Outra coisa são os futuros transistores com porta circular e canais nanopage – GAA. Os canais Nanopage ficarão localizados paralelamente ao plano do corte de silício tradicional e perderão o benefício na forma de condução acelerada de furos.

A equipe de pesquisa da IBM criou uma série de variações de pares de transistores GAA em silício em ambas as orientações de corte. Os transistores tinham diferentes números de canais, diferentes seções transversais e canais de diferentes comprimentos. Em todos os casos, os transistores com orientação de silício 110 superaram seus equivalentes de silício 001. Para canais mais grossos, a diferença foi menor, mas ainda permaneceu. Além disso, os transistores de condução de elétrons (nFETs) revelaram-se um pouco mais lentos no corte 110 do que no 001. Mas o desempenho visivelmente aumentado dos pFETs em um chip com corte 110 compensou isso.

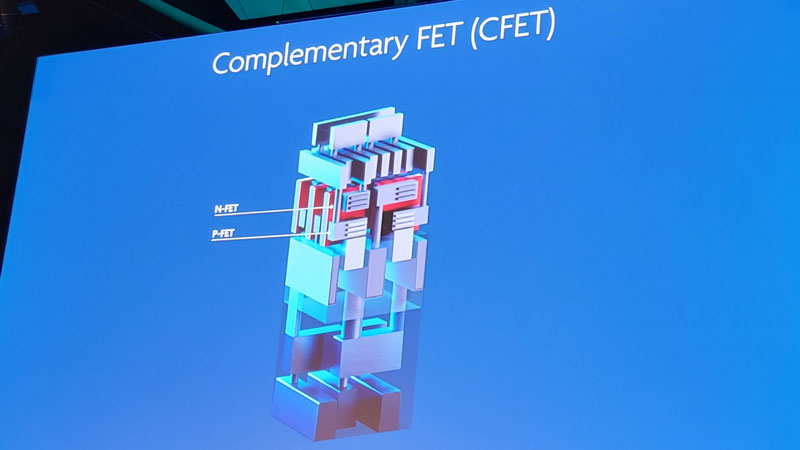

Representação de um par de transistores complementares empilhados verticalmente um sobre o outro. Fonte da imagem: Intel

A IBM também vai encontrar uma maneira de reduzir o impacto negativo da orientação alternativa na condutividade eletrônica. Além disso, os cientistas explorarão o uso de silício alinhado 110 em transistores nanoestruturados 3D chamados transistores de efeito de campo complementares (CFETs). Nesta arquitetura, os elementos nFET são geralmente colocados em cima dos pFETs para evitar o aumento do tamanho dos chips. Espera-se que esses dispositivos multiníveis estejam disponíveis dentro de 10 anos, e todos os três fabricantes de chips lógicos avançados já apresentaram protótipos de CFET no mês passado no IEDM 2023. Nesse caso, os pFETs poderiam ser feitos de silício 110 e os nFETs de silício 001.

De qualquer forma, esta não é uma solução para amanhã. É improvável que os fabricantes mudem a orientação de corte dos cristais de silício até 2030. Eles têm tecnologias em estoque que melhoram o desempenho do chip de maneiras menos exóticas.