A Samsung Electronics estabeleceu um grupo de trabalho para desenvolver novas tecnologias de embalagem de semicondutores, que irão, entre outras coisas, expandir a cooperação com grandes empresas envolvidas neste campo. O grupo, formado pela unidade de negócios Device Solutions (DS) em meados de junho, reporta-se diretamente ao CEO da Samsung, Kyung Kye-hyun, que lidera a DS.

Fonte da imagem: Samsung

A nova equipe incluiu engenheiros da equipe de Test & System Package (TSP) da DS, especialistas do Centro de Pesquisa e Desenvolvimento de Semicondutores e as equipes de memória e outros chips da Samsung. O grupo tem a tarefa de oferecer soluções de embalagem de semicondutores de ponta.

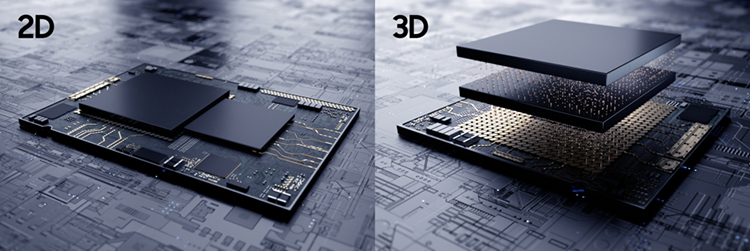

A mudança mostra a importância que Kyung Ki Hyun atribui à tecnologia avançada de embalagem de semicondutores. Atualmente, quando a miniaturização de microcircuitos está se aproximando de seus limites, as tecnologias de embalagem 3D estão ganhando popularidade, que permitem combinar microcircuitos fabricados usando diferentes processos técnicos em um único chip.

Gigantes globais de semicondutores, como Intel e TSMC, estão investindo ativamente no desenvolvimento de tecnologias avançadas de encapsulamento de chips. Em 2022, a Intel e a TSMC respondem por 32% e 27% do investimento global em tecnologia avançada de embalagem de semicondutores, respectivamente, de acordo com a empresa de pesquisa Yole Development. Em termos de investimento nesta área, a Samsung Electronics ocupa o quarto lugar depois da ASE, uma empresa de teste e embalagem de circuitos integrados de Taiwan.

A Intel usa a tecnologia de empacotamento espacial Foveros para fabricar chips. Em particular, com sua ajuda, foi fabricado o processador Lakefield, lançado em 2020, usado nos laptops da Samsung Electronics. Além disso, a TSMC já está usando o encapsulamento de chips 3D na fabricação de processadores para AMD.

A Samsung também está trabalhando ativamente nessa direção. Em 2020, uma empresa sul-coreana introduziu a tecnologia X-Cube para empacotamento 3D de chips de memória com SRAM localizada em um chip lógico ou unidade central de processamento. E Choi Si-young, presidente e chefe da divisão de chips, disse na conferência anual Hot Chips 2021 que a empresa está desenvolvendo “embalagens 3.5D” de chips.