Na abertura do Hot Chips deste ano, a palavra será dada não apenas ao chefe da AMD Lisa Su, mas também ao especialista líder em pesquisas da TSMC, Philip Wong, que falará sobre as perspectivas de dominar as normas litográficas além de 2 nm. Godfrey Cheng, chefe do departamento de marketing da TSMC, decidiu iniciar esta apresentação com uma palestra sobre como manter a chamada “Lei de Moore” nas páginas do blog corporativo. Na interpretação da TSMC, esta regra geral é assim: o número de transistores em um chip semicondutor de uma área constante dobra uma vez a cada dois anos.

De acordo com representantes da TSMC, o layout tridimensional definitivamente tem suas próprias perspectivas, mas as decisões de layout relacionadas à chamada geração 2.5D não devem ser desconsideradas. Sistemas de inteligência artificial e o preenchimento de futuros “robomobiles” – todos esses componentes exigirão a troca de informações mais rápida possível entre processadores e memória, portanto você precisa não apenas criar interfaces e tipos de memória mais rápidos, mas também aproximar os chips de memória dos processadores. Como fazer isso já foi demonstrado pela Intel, NVIDIA e AMD. Eles usam uma ponte de silício, que conecta não apenas processadores heterogêneos, mas também chips de memória, como o HBM2.

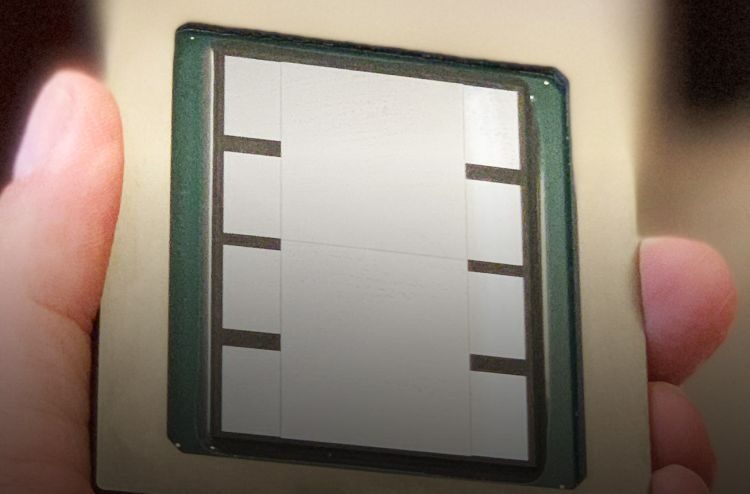

Fonte da imagem: TSMC

A TSMC demonstrou um protótipo da maior ponte de silício do mundo. Possui uma área de 2500 mm2, permitindo que você coloque dois processadores distintos com uma área de 600 mm2 cada, além de oito chips de memória, como o HBM. Se voltarmos à idéia de um layout tridimensional, a TSMC considera possível usar vários materiais para criar cristais monolíticos com blocos funcionais heterogêneos. Eles podem ser localizados um acima do outro em vários níveis, intercalados com “camadas de memória”.