Este ano, a Intel® viu uma atividade sem precedentes. Até agora, não parece ter acontecido que tivemos que analisar dois designs de processador de cliente sequencial em apenas alguns meses. Mas tudo acontece pela primeira vez, e hoje é um bom momento para se familiarizar com os processadores Alder Lake, embora a geração anterior do Rocket Lake ainda seja uma novidade recente.

Na verdade, ainda falta um pouco de tempo para o lançamento do Lago Alder. Os processadores desta família, muito provavelmente, serão anunciados em um evento especial Intel Innovation de 27 a 28 de outubro, ou seja, em um mês. No entanto, o próximo anúncio parece grandioso demais para não ser preparado com antecedência. Na verdade, desta vez, o lançamento de novos processadores significará uma mudança de plataforma e uma mudança na microarquitetura, e até mesmo, em certo sentido, uma mudança em todo o conceito de computação multithread. Por isso decidimos coletar e organizar com antecedência todas as informações disponíveis sobre o Lago Alder, para que depois de um mês possamos encontrar esses processadores totalmente armados, com todos os conhecimentos teóricos necessários.

Felizmente, a Intel já revelou alguns detalhes sobre a arquitetura e detalhes internos de Alder Lake durante as apresentações Intel Accelerated e Intel Architecture Day 2021. Graças a isso, hoje, como parte de uma parceria com a Intel, podemos falar sobre futuros processadores de consumo , com base apenas em dados verificados. em primeira mão.

⇡#Vista aérea do Lago Alder

O lançamento dos processadores Alder Lake, independentemente do seu sucesso, será um grande evento para todo o mercado de processadores. A questão não é apenas que a Intel atualizará seriamente a microarquitetura neles e adicionará suporte para tipos fundamentalmente novos de memória e interfaces externas, mas também que eles se tornarão a personificação de um conceito completamente diferente de computação multithread, que ainda é usada em processadores x86 em massa. ninguém tentou. A questão é que o Lago Alder receberá uma estrutura híbrida e será baseado em dois tipos de núcleos ao mesmo tempo – produtivo (núcleos P) e eficientes (núcleos E). Sua combinação em um único dispositivo de computação, tal como concebida pelos desenvolvedores, deve permitir alcançar flexibilidade anteriormente inatingível, tanto em termos do escopo de aplicabilidade de tais processadores,

A abordagem híbrida big.LITTLE já existe há muito tempo em processadores baseados em ARM, e a ideia da Intel para Alder Lake é um tanto semelhante a isso. A Intel prevê que grandes núcleos de desempenho devem ser colocados em tarefas de primeiro plano de alta prioridade que requerem tempos de resposta curtos, enquanto núcleos pequenos e com baixo consumo de energia podem ser envolvidos em processos de segundo plano. Além disso, todos os tipos de kernels podem ser combinados para resolver um problema, o que permitirá que você atinja o nível máximo de desempenho, pelo menos em teoria.

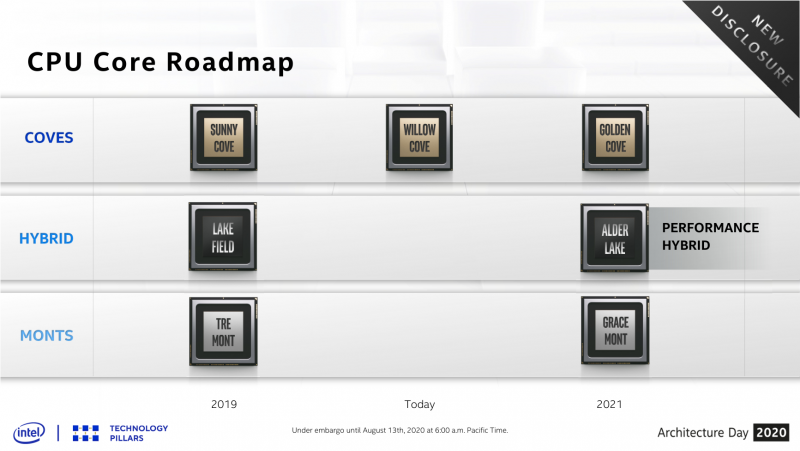

Ao mesmo tempo, ambos os tipos de núcleos em Alder Lake receberam novas microarquiteturas que ainda não encontramos. Os núcleos de desempenho são baseados na microarquitetura Golden Cove, que é um desenvolvimento posterior de Cypress Cove (de Rocket Lake) e Willow Cove (de Tiger Lake). E os núcleos eficientes têm a microarquitetura Gracemont, que cresceu a partir dos processadores Atom e é um desenvolvimento posterior da microarquitetura Tremont, que foi usada tanto em processadores Lakefield experimentais quanto nas séries mais compreensíveis Pentium (Silver) e Celeron N e J, codinome Jasper Lake e Elkhart Lake.

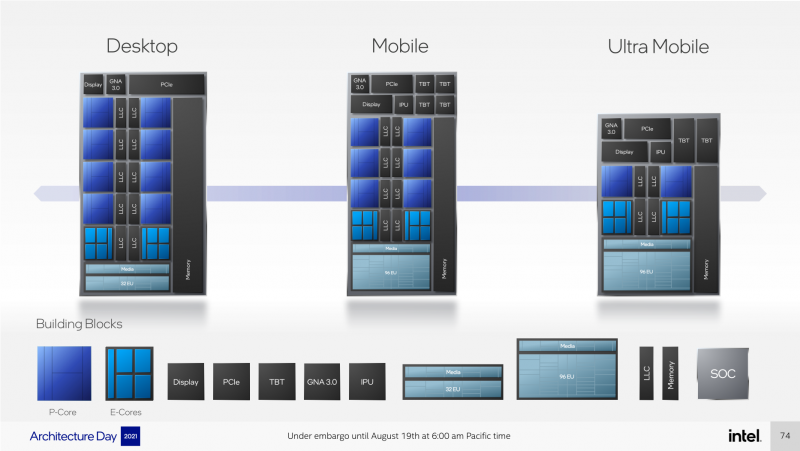

Um desafio importante que a Intel definiu para si mesma no desenvolvimento de Alder Lake foi criar não apenas dois tipos de núcleos, mas também um conjunto mais amplo de vários blocos de construção que poderiam permitir a você montar facilmente vários processadores de consumidor para diferentes segmentos de mercado e com diferentes características: desktop e móveis de alto desempenho e até ultramóveis.

Apesar da modularidade inerente ao design, a topologia em mosaico ainda não é usada nos processadores Alder Lake – um análogo dos chips na visão da Intel. A empresa adotará esse método de montagem um pouco mais tarde. Em vez disso, as várias variantes de Alder Lake são construídas em um único chip semicondutor monolítico. Mas, por conveniência, os desenvolvedores ajustaram especialmente os tamanhos dos componentes de Alder Lake uns aos outros e, por exemplo, um P-core produtivo corresponde aproximadamente em área aos quatro E-cores efetivos montados em um cluster. Proporções semelhantes são mantidas para outros elementos do processador (para o núcleo gráfico, controlador de memória, controlador PCIe, etc.) – isso é precisamente o que fornece uma variedade e flexibilidade de configurações.

O núcleo gráfico continua sendo uma parte integrante dos futuros processadores Alder Lake, como antes. A Intel forneceu duas opções gráficas: o GT1 com 32 unidades de execução para processadores desktop e o GT2 com 96 dispositivos para aplicativos móveis. As GPUs incorporadas são baseadas na arquitetura gráfica de 12ª geração, o que significa que estão na classe Xe LP e correspondem aproximadamente às capacidades do núcleo gráfico dos processadores Tiger Lake. Na variante GT2, os gráficos integrados devem ser capazes de fornecer um desempenho de jogo aceitável em 1080p (com configurações de baixa qualidade) e suportar um canal de reprodução de vídeo de 12 bits. No entanto, apenas uma versão mais simples da GPU entrará nos processadores de desktop.

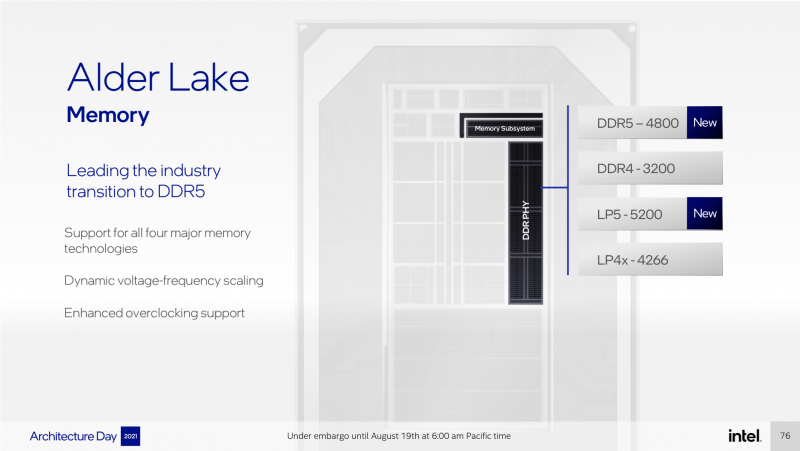

A falta de atualizações cardinais no núcleo gráfico deve ser compensada por um novo controlador de memória com suporte para quatro tipos de SDRAM de uma vez. Ele pode funcionar com as memórias DDR5-4800 e LPDDR5-5200 mais recentes e DDR4-3200 e LPDDR4X-4266 mais antigas. Naturalmente, todos os quatro tipos de memória não serão suportados simultaneamente: a escolha de uma ou outra opção ocorrerá na fase de projeto de uma plataforma específica. É lógico esperar que o suporte para SDRAM DDR5 apareça antes de tudo em desktops de alto desempenho (relativamente falando, com base nos chipsets da série Z), enquanto as soluções de médio alcance continuarão a contar com as habituais memórias DDR4 e LPDDR4X. E isso continuará enquanto o preço dos módulos DDR5 exceder significativamente o custo dos módulos DDR4.

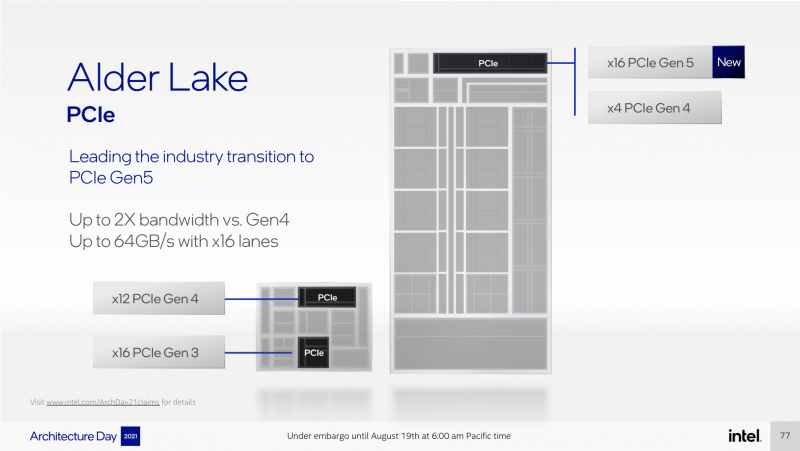

O bloco de interface PCI Express que os engenheiros da Intel projetaram para Alder Lake também contém grandes inovações. Pela primeira vez no segmento de consumidor, ele apresenta suporte a PCIe 5.0, que dobra a largura de banda mais uma vez e permite que um slot gráfico PCIe x16 forneça largura de banda de 64 GB / s. Ao mesmo tempo, para conectar drives NVMe, o controlador do processador oferece apenas a interface PCIe 4.0 x4, que, no entanto, é suficiente para qualquer SSD do mercado. Além disso, o suporte PCIe 5.0 estará presente exclusivamente nas versões desktop do Alder Lake. Os processadores atribuídos ao segmento móvel receberão um controlador PCIe diferente, no qual os recursos serão de alguma forma limitados.

Mas também há exemplos inversos: alguns blocos de construção de Alder Lake destinam-se exclusivamente a variantes de CPU móvel. Isso inclui, por exemplo, o controlador Thunderbolt 4 ou o coprocessador de imagem IPU. Eles não serão integrados às versões de desktop dos processadores.

Todos os elementos de Alder Lake, incluindo vários núcleos, gráficos e fragmentos de cache L3, controladores de memória e PCIe, bem como todos os outros blocos, como antes, são combinados em uma unidade por meio de um barramento de anel bidirecional, que nesta implementação tem uma largura de banda de até 1000 GB / com. Uma versão semelhante do barramento em anel já foi usada no Tiger Lake móvel, mas nos novos processadores a Intel prometeu otimizações adicionais para reduzir a latência.

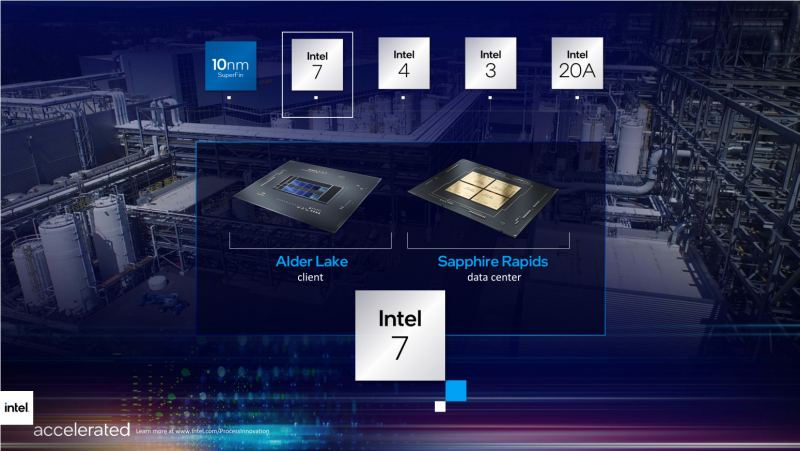

Outra grande inovação diz respeito ao processo de produção. Alder Lake será o primeiro chip Intel a ser fabricado usando a tecnologia de processo Intel 7 – até recentemente, ele foi renomeado como 10nm Enhanced SuperFin. Estamos falando aqui da segunda etapa de otimização do processo com normas de 10nm, que deve proporcionar uma melhoria no desempenho específico por watt em 10-15% em relação à versão anterior da tecnologia de processo SuperFin de 10nm. Embora a tecnologia de processo Intel 7 fosse considerada anteriormente de 10 nm, em termos de densidade de transistores em um chip ela é comparável ou superior à tecnologia de processo de 7 nm de outros fabricantes, o que deu ao fabricante o direito moral de renomear a tecnologia para Intel 7. Assim, de acordo com o WikiChip, a antiga tecnologia de processo de 10 nm da Intel acomoda 100,76 M transistores por mm2,

Usando essa tecnologia de fabricação, a Intel pretende embalar até oito núcleos produtivos e oito núcleos eficientes em cristais semicondutores Alder Lake ao mesmo tempo. Isso significa que o número máximo de núcleos em processadores futuros chegará a 16, mas essas configurações só serão oferecidas para plataformas de desktop. É bastante incomum que o processador máximo de 16 núcleos seja capaz de executar simultaneamente não 32, mas apenas 24 threads, e o volume de sua memória cache de terceiro nível será de 30 MB.

Essa estranha combinação do número de núcleos e threads se deve ao fato de que os P-cores têm suporte para a tecnologia Hyper-Threading, enquanto os E-cores não. Além disso, eles operam em diferentes frequências de clock e têm caches de diferentes tamanhos e organizações. Tudo isso significa que as características de passaporte de vários modelos de Alder Lake podem parecer surpreendentes para muitos: dependendo do número de certos núcleos, CPUs específicas receberão combinações muito incomuns de número de threads e núcleos, frequências e quantidade de memória cache.

A Intel revelou até agora três designs básicos de chips semicondutores Alder Lake visando três segmentos distintos: processadores Alder Lake-S para desktops de alto desempenho que irão alimentar a próxima geração de placas-mãe LGA1700; Processadores móveis Alder Lake-P com 12 a 35 W TDP em BGA Type3; Ultra Mobile Alder Lake-M BGA Type4 HDI 7W a 15W TDP para Ultrabooks. O dado do processador Alder Lake-S contém oito núcleos P, oito núcleos E e gráficos GT1. Alder Lake-P é limitado a seis P-núcleos, mas usa os poderosos gráficos GT2. E em Alder Lake-M, apenas dois P-cores são fornecidos, mas ainda os mesmos oito E-cores e uma GPU GT2.

Os processadores para desktop Alder Lake-S parecem ser os primeiros a chegar ao mercado. Sua linha será liderada por processadores Core i9 com fórmula nuclear 8 + 8, e também, de acordo com informações não confirmadas, pode incluir processadores Core i7 com fórmula 8 + 4, duas variantes do Core i5 com 6 + 4 ou 6 Fórmula + 0 e, possivelmente, processadores Core i3 com núcleos 4 + 0. Deve ser enfatizado separadamente que esse registro do número de núcleos como uma soma de dois termos não é fácil de usar. É errado resumir o número de núcleos P e E: a Intel não apresentará o antigo Alder Lake como ofertas de 16 núcleos, eles serão posicionados como oito núcleos avançados com núcleos adicionais com eficiência energética. Portanto, por exemplo, você não deve se surpreender com a composição da série Core i5, onde processadores com 10 e 6 núcleos serão apresentados ao mesmo tempo:

⇡#Como tudo funciona: Intel Thread Director

A rigor, Alder Lake não é o primeiro processador x86 a combinar dois tipos de núcleo diferentes. A Intel lançou anteriormente processadores Lakefield híbridos com eficiência energética, onde um núcleo Sunny Cove coexistia com quatro núcleos Tremont. No entanto, não receberam um reconhecimento notável e, embora tenham sido apresentados apenas no segundo trimestre do ano passado, já foram descontinuados. Eles devem seu triste destino em parte a problemas com seu funcionamento no Windows 10, que nem sempre distribuiu corretamente a carga entre núcleos heterogêneos, o que levou a uma diminuição no desempenho. Inicialmente, foi assumido que um sistema operacional especial Windows 10X será projetado para dispositivos baseados em Lakefield, no qual algoritmos adaptados serão colocados, no entanto, infelizmente, a Microsoft cancelou seu lançamento.

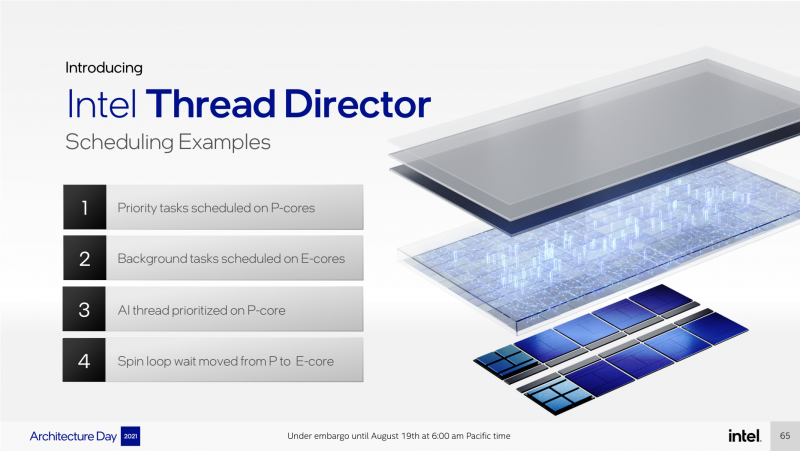

Esta história levanta preocupações de que o mesmo poderia acontecer com Alder Lake. Afinal, está claro que, para que os APUs funcionem corretamente, o planejador do sistema operacional deve distinguir entre os tipos de núcleo e despachar dinamicamente cargas exigentes para núcleos que podem oferecer alto desempenho enquanto os liberta de tarefas em segundo plano ao longo do caminho. Mas desta vez a Intel tinha tudo sob controle. Para ajudar o planejador a entender melhor a estrutura do processador e maximizar o desempenho, Alder Lake apresenta a tecnologia de hardware Intel Thread Director, que será responsável pelo balanceamento de carga em conjunto com o novo sistema operacional Windows 11.

A essência do Thread Director é enviar dados telemétricos detalhados sobre o estado atual de todos os núcleos para o agendador do SO, graças ao qual ele pode tomar decisões informadas sobre a ligação de threads a núcleos específicos. Essa tecnologia, como a Intel promete, deve contornar todas as dificuldades que possam surgir na operação prática de processadores híbridos com núcleos de diferentes tipos. E o mais importante, é completamente transparente para o software e não requer nenhuma alteração no código do programa.

A parte principal do Intel Thread Director é um microcontrolador embutido no processador, que coleta dados detalhados de baixo nível sobre cada núcleo do processador, incluindo temperatura, consumo de energia, carga e outros parâmetros, e os transfere para o programador do sistema operacional com atrasos mínimos. Além disso, o Thread Director continuamente, com discrição de nanossegundos, monitora as instruções que são executadas por cada núcleo e também analisa a carga de seus dispositivos executivos. Com base em todas essas informações, o planejador é capaz de alternar threads entre os núcleos de maneira significativa e de acordo com uma estratégia compreensível, cuja essência é garantir que as tarefas de primeiro plano e os aplicativos sensíveis à latência sejam o mais rápido possível. Por exemplo, threads que operam em instruções vetoriais recebem prioridade mais alta ao mover para núcleos de alto desempenho, enquanto threads operando em instruções escalares são mais propensos a serem enviados para núcleos com eficiência de energia. Mas, em qualquer caso, todo este sistema é dinâmico e a transferência de threads de um núcleo para outro depende de muitos fatores diferentes, incluindo os tipos de carga executada no processador a qualquer momento.

A Intel deu vários exemplos de como o Thread Director funciona em alguns casos especiais. Por exemplo, quando todos os núcleos estão livres, um processo de unidade sempre será enviado imediatamente para o P-core, mas se todos esses núcleos estiverem ocupados no início do processo, ele começará a trabalhar no E-core e moverá para o P-core somente quando o Thread Director considerar tal transferência apropriada. Em outra situação, quando o processador é carregado com um número crescente de threads de pares, eles são enviados primeiro um para cada P-core livre, depois um para cada E-core livre e, em seguida, um para os núcleos virtuais que existem devido ao Hyper -Threading technology …

Separadamente, também é estipulado que a ligação de threads aos núcleos não é constante, e eles podem se mover ativamente de um tipo de núcleo para outro no processo. Isso pode ocorrer devido a uma mudança na natureza da carga em um encadeamento computacional e em situações em que o número de encadeamentos exigentes começa a exceder o número de núcleos produtivos. Nesta situação, alguns threads serão portados para E-cores para liberar energia para a carga que precisa de mais poder de computação a qualquer momento.

Até agora, processadores e sistemas operacionais não trocavam informações a fim de otimizar a alocação de recursos de computação: o escalonador confiava apenas nos dados de prioridades de thread atribuídas a ele pelo próprio sistema operacional ou pelos desenvolvedores do programa. Agora, com a tecnologia Thread Director, o trabalho do escalonador deve se tornar um processo mais independente, delicado e dinâmico. Essa simbiose de hardware e software dá esperança de que os diferentes núcleos das APUs Alder Lake sejam usados exatamente como a Intel pretendia – para garantir o mais alto nível de desempenho.

Ao mesmo tempo, a introdução do Thread Director adiciona novas oportunidades para desenvolvedores de software. As extensões da biblioteca PowerThrottling API disponíveis para processadores Alder Lake apresentam atributos de QoS adicionais para threads de forma que os autores do programa possam opcionalmente marcar os threads gerados. Além disso, para threads que são obviamente capazes de funcionar em núcleos de baixo consumo de energia e não requerem alto poder de computação, uma marcação separada foi introduzida. Sabe-se que vários componentes do Windows 11, incluindo o navegador Edge, usarão as extensões descritas, o que mais uma vez reflete a estreita colaboração da Intel com a Microsoft na criação e suporte da arquitetura de processador híbrido.

Infelizmente, a Intel não compartilhou informações detalhadas sobre o Thread Director, então, por enquanto, temos que acreditar no fato de que, graças a esta tecnologia, a carga necessária será enviada para os núcleos necessários. No entanto, os processadores Alder Lake permitirão que você desative os E-cores se o usuário tiver dúvidas sobre a conveniência de trazê-los para o trabalho.

A Intel está se concentrando no novo sistema operacional Windows 11 com um agendador otimizado quando se trata de distribuir threads em núcleos de APU. No entanto, Alder Lake deve funcionar razoavelmente bem sem a interação próxima entre Alder Lake e o planejador implementado neste sistema operacional. A Intel aponta que no antigo sistema operacional Windows 10, os novos processadores serão capazes de funcionar muito bem. Embora o Thread Director não seja compatível com o Windows 10, este sistema operacional conta com o mecanismo Intel Hardware Guided Scheduling, que também é capaz de alternar threads levando em consideração a heterogeneidade dos núcleos, mas não com tanta precisão e com uma frequência ligeiramente inferior. No entanto, de acordo com a Intel,

⇡#Incidente com AVX-512

O fato de que os núcleos Gracemont energeticamente eficientes não têm registros de 512 bits e não suportam o conjunto de instruções AVX-512 é conhecido há muito tempo, e parece bastante natural se lembrarmos que a implementação de operações vetoriais requer tanto um orçamento de transistor significativo e consumo de energia significativo. … Mas uma pergunta natural surge imediatamente sobre como, neste caso, o trabalho com essas instruções nos processadores Alder Lake como um todo será construído? A resposta a essa pergunta acabou sendo muito simples – de forma alguma. Embora nos núcleos produtivos de Willow Cove como parte de Alder Lake, registradores e atuadores com dimensão de 512 bits estejam embutidos na microarquitetura, a execução de instruções AVX-512 neles é bloqueada no nível de hardware para não causar colisões desnecessárias ao despachar threads que trabalham com tais comandos.

E isso significa que, com o advento dos processadores Alder Lake, as extensões do conjunto de instruções suportadas pelas CPUs do consumidor foram revertidas. Apesar do suporte para AVX-512 ter sido implementado em ambos os processadores móveis Tiger Lake e processadores de desktop Rocket Lake, ele não estará disponível novamente na nova geração de processadores.

Como compensação, a Intel adicionou suporte para um subconjunto de instruções VNNI para Alder Lake para resolver problemas relacionados a redes neurais. E essas instruções, por incrível que pareça, podem ser executadas em núcleos de alto desempenho e com eficiência energética. No entanto, essas não são as mesmas instruções VNNI que antes eram consideradas parte do conjunto AVX-512 e operavam com registradores de 512 bits. Como esses registros estão bloqueados em Alder Lake, as instruções VNNI neles operam em registros de 256 bits e, por assim dizer, existem em um subconjunto de instruções AVX2. Em outras palavras, o conjunto de instruções AVX2-VNNI, que é implementado em Alder Lake, difere um pouco do conjunto AVX-512 VNNI apresentado anteriormente e requer suporte especial do software. Por isso, conte com

Microarquitetura de núcleos e desktop Alder Lake-S

⇡#Kernels de desempenho em detalhes

A parte mais importante dos processadores Alder Lake são os novos P-cores Golden Cove. Eles não apenas ocupam a parte mais significativa da área em um cristal semicondutor, mas também carregam a maior parte da responsabilidade pelo desempenho do processador, uma vez que assumem a execução de tarefas de primeiro plano que consomem muitos recursos. Portanto, não é surpreendente que os desenvolvedores da microarquitetura Golden Cove foram incumbidos não apenas de criar o núcleo x86 mais rápido de todos os existentes, mas de alcançar uma superioridade clara em desempenho específico sobre seus predecessores. No entanto, não havia vitória a qualquer custo: processadores baseados em núcleos Golden Cove deveriam ser capazes de funcionar em uma ampla gama de dispositivos, de laptops a servidores, o que significa que além do alto desempenho, a escalabilidade também é de suma importância. Por exemplo, no caso dos processadores de consumo Alder Lake de nosso interesse, a otimização da microarquitetura tanto para cargas single-threaded quanto para aplicativos multi-threaded com uso intensivo de recursos para trabalhar com conteúdo digital desempenha um papel importante.

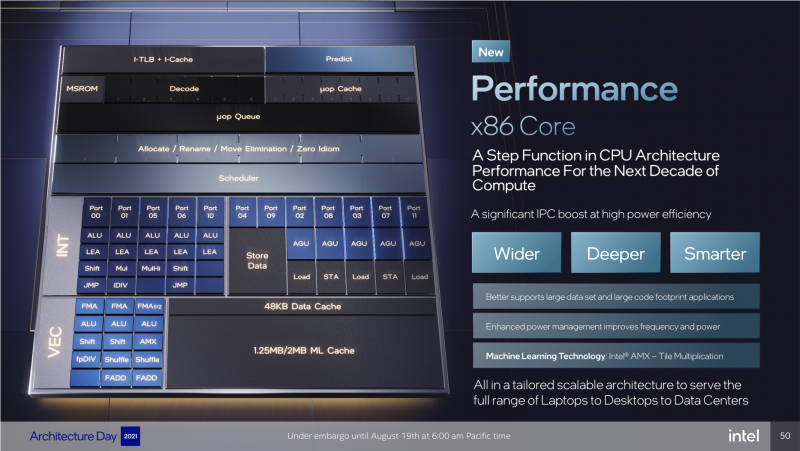

A Intel confiou no núcleo do Skylake por um longo tempo e embarcou em uma grande revisão de sua microarquitetura de mais sucesso e vida relativamente recente. Mas, começando com a microarquitetura Sunny Cove lançada em 2019, a empresa começou a realizar várias melhorias com um ritmo anormalmente vigoroso. Ela imediatamente formulou o princípio de “mais amplo, mais profundo, mais inteligente” e, de acordo com ele, começou a remodelar de forma consistente o antigo núcleo do Skylake. A microarquitetura Golden Cove, portanto, já é a segunda iteração de melhorias. E nele vemos novamente buffers de reordenamento mais profundos, mais registros físicos, uma janela de busca de instrução mais ampla e um número maior de portas de execução. Anexada a essa lista está a previsão aprimorada de ramificação, que reduz o tempo de inatividade do agente devido à previsão incorreta de ramificação.

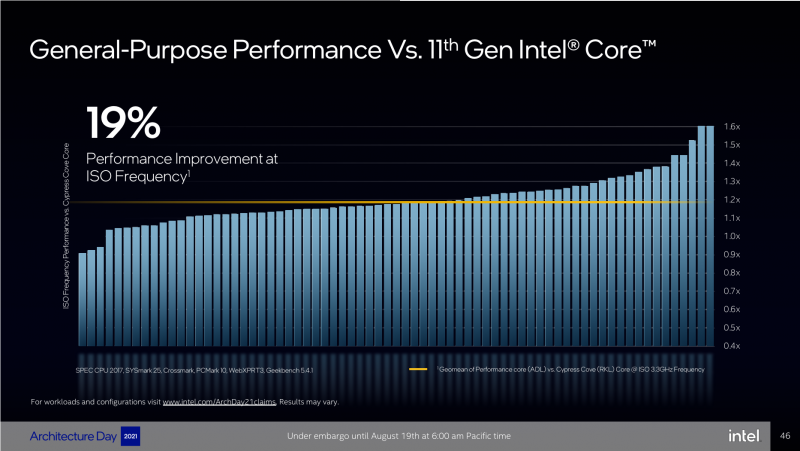

A própria Intel avalia muito a eficácia das mudanças feitas na microarquitetura. De acordo com a empresa, o desempenho específico médio do núcleo Golden Cove (na mesma frequência) é 19% superior ao do núcleo Cypress Cove usado nos processadores Rocket Lake. Ao mesmo tempo, em algumas tarefas, o crescimento dentro de uma mudança de geração pode ser muito maior e chegar a 60%. E tudo isso parece muito promissor, porque graças à nova tecnologia de produção Intel 7, os processadores Alder Lake não devem ficar atrás de seus predecessores em termos de velocidade de clock.

Além disso, o aumento de desempenho específico em cada nova versão da microarquitetura em 19% tornou-se uma espécie de padrão para a Intel. O mesmo passo foi dado com a transição do Skylake para o Cypress Cove, o que significa que o IPC (desempenho específico por clock) do núcleo do Golden Cove é maior do que o do Skylake, em cerca de 40-45%. Como resultado, pode-se esperar que Golden Cove supere as arquiteturas rivais, especialmente o Zen 3.

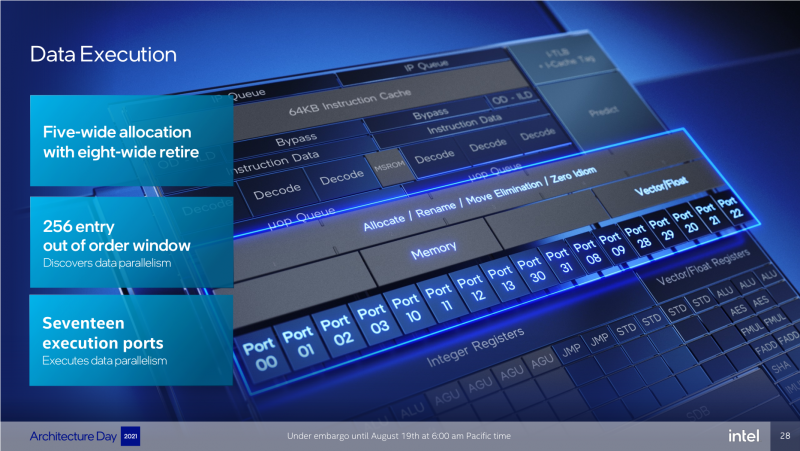

Mudanças perceptíveis na microarquitetura Golden Cove começam a ser vistas logo na entrada do pipeline de execução. Em primeiro lugar, vale destacar o aumento do número de decodificadores – de 4 para 6, o que possibilita ao kernel decodificar 6 instruções por clock. Para que os decodificadores não fiquem ociosos, o tamanho da amostra de código em Golden Cove aumentou de 16 para 32 bytes. Além disso, a Intel trabalhou para melhorar a eficiência do cache micro-op, que armazena instruções já decodificadas. Em comparação com Cypress Cove, seu volume aumentou de 2,25 para 4.000 registros e a taxa de transferência aumentou para 8 micro-ops por relógio em vez de 6. Tudo isso permite saturar os estágios subsequentes do pipeline de execução após a decodificação – o despachante e o agendador – com visivelmente mais alta intensidade.

Para melhorar a capacidade de trabalhar com código complexo, a Intel dobrou o número de registros de página de 4K no iTLB e também melhorou a previsão de ramos, aumentando o tamanho máximo do buffer de destino de ramos de 5 para 12 mil registros. Além disso, esse buffer recebeu inteligência adicional – um algoritmo baseado em aprendizado de máquina que pode ajustar sua capacidade à carga atual para otimizar o desempenho e o consumo de energia.

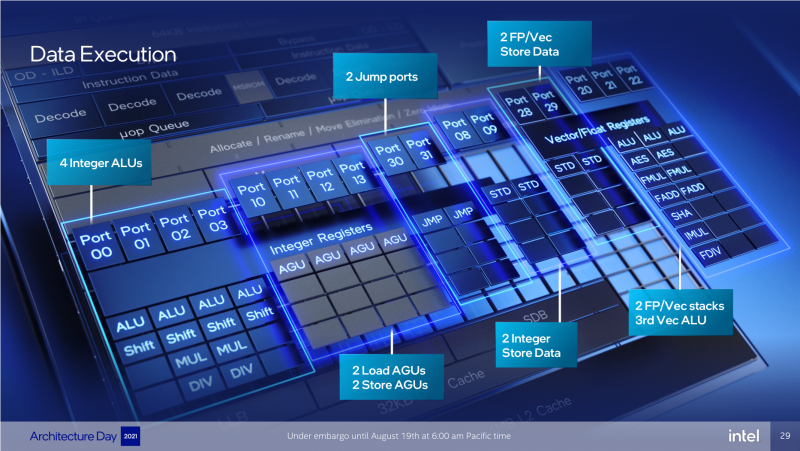

O despachante, envolvido em receber e colocar micro-operações, bem como renomear registros, recebeu uma largura maior – agora inclui 6, em vez de 5, como antes, blocos iguais. O mecanismo de execução fora de ordem tornou-se mais eficiente aumentando o buffer correspondente de 352 para 512 entradas. E, no total, tudo isso acabou sendo o suficiente para carregar um número maior de dispositivos executivos com trabalho, que são agrupados no Golden Cove em 12 portas (contra 10 portas para Cypress Cove). Além disso, a Intel mencionou outro novo mecanismo, graças ao qual algumas instruções podem ser executadas mesmo na fase de renomeação de registradores, o que deve, adicionalmente, descarregar o domínio de execução.

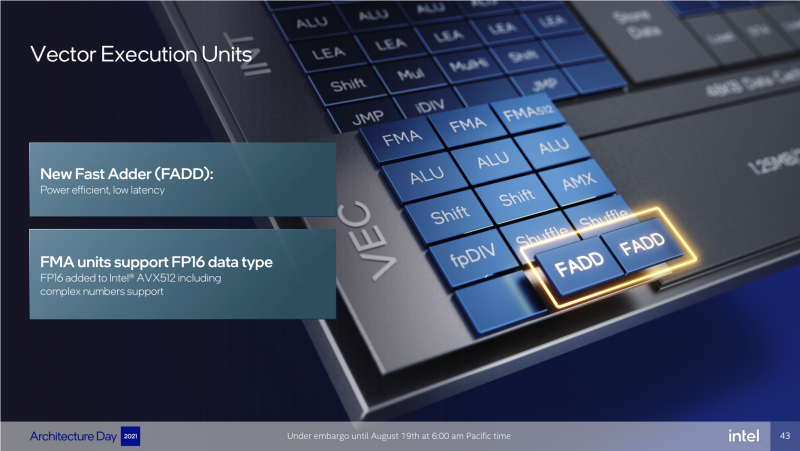

Uma das portas executivas adicionadas ao Golden Cove é dedicada ao trabalho com as equipes ALU e LEA. Assim, o novo kernel tem cinco dispositivos inteiros de uma vez, capazes de executar uma instrução por ciclo de clock.

Além disso, dois dispositivos adicionais para adição rápida de vetores (FADD) apareceram aqui separadamente.

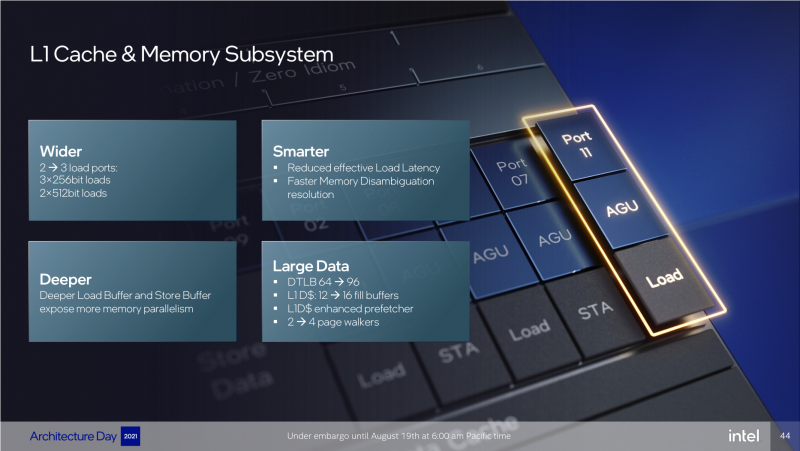

As melhorias também afetaram o cache L1D, que recebeu três portas de download em vez das duas disponíveis anteriormente, bem como buffers de carregamento e descarregamento mais espaçosos. Ao longo do caminho, a Intel aumentou a capacidade L1 TLB em 50%. As alterações no algoritmo L1D também afetaram a pré-busca de dados, que agora usa quatro analisadores em vez de dois, o que deve ter um efeito ao trabalhar em um ambiente multithread. Ao mesmo tempo, a quantidade de cache L1D no núcleo Golden Cove permanecerá no nível de 48 KB – como em Sunny Cove.

Já para o cache L2, em Alder Lake, cada P-core contará com um cache L2 de 1,25 MB com baixa latência e possibilidade de expansão para até 2 MB no futuro. Como no caso do L1D, a Intel promete uma pré-busca de dados aprimorada para ele, com base na identificação de padrões de solicitações de memória.

Resumindo tudo o que foi dito acima, podemos afirmar que, em comparação com a geração anterior da microarquitetura, o decodificador no núcleo Golden Cove expandiu em 50%, o estágio de preparação das microoperações em 25%, e a saída buffer de ordem em 45%. Além disso, é tudo temperado com melhorias significativas no mecanismo de previsão de branch. Como essas melhorias aparecem em termos numéricos, você pode ver na tabela abaixo.

Resta acrescentar que outro elemento curioso apareceu nos núcleos Golden Cove – um microcontrolador adicional e completamente independente para gerenciamento de energia, que fornece coleta de telemetria com resolução de microssegundos, o que melhora a precisão de todo o monitoramento em várias ordens de magnitude em comparação com o esquema antigo. A maior precisão permite que a CPU gerencie o consumo de energia e o desempenho com menor latência, o que, em última análise, aumenta as frequências médias do núcleo sob carga, sem sacrificar o consumo de energia e a dissipação de calor, diz a Intel. O microcontrolador embutido para gerenciamento de energia no Golden Cove é usado pela primeira vez – não existiam tais soluções em núcleos da Intel antes. E foi útil em Alder Lake – o mesmo microcontrolador está ativamente envolvido na tecnologia Thread Director.

⇡#Núcleos de eficiência energética em detalhes

Os núcleos energeticamente eficientes em Alder Lake atuam como um acompanhamento para os núcleos Golden Cove. Eles não executam partes solo, mas junto com eles os núcleos P, figurativamente falando, devem soar mais convincentes. Os E-cores são baseados na microarquitetura Gracemont e representam um desenvolvimento posterior dos processadores Atom, embora tenham se distanciado bastante deles. No entanto, o conceito permanece o mesmo: compactação e eficiência estão em primeiro lugar. Mas, ao mesmo tempo, de acordo com a Intel, os desenvolvedores conseguiram projetar os núcleos Gracemont de tal forma que em termos de desempenho específico por watt, eles são visivelmente superiores ao Skylake, ocupando quatro vezes menos espaço na matriz do que os núcleos P , e, além disso, são altamente eficientes em termos energéticos.

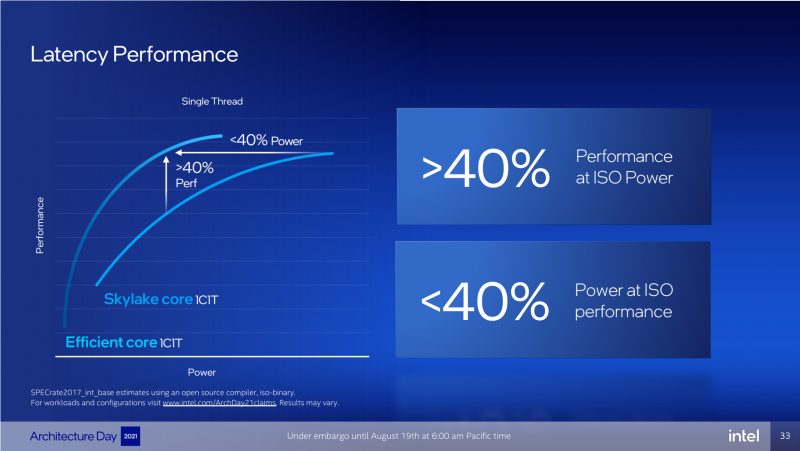

De acordo com dados da própria Intel obtidos com uma carga inteira de thread único, no caso de equalização do consumo de energia, Gracemont é 40% mais produtivo que Skylake, e em caso de igualdade de desempenho, consome 40% menos.

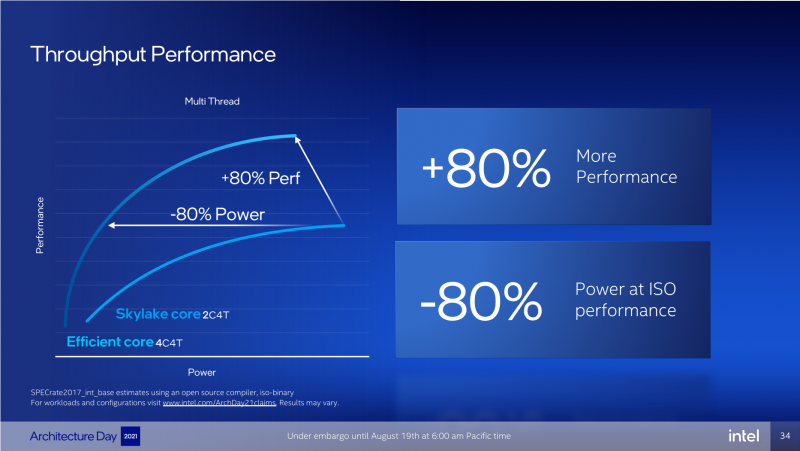

Outro indicador citado pelos desenvolvedores diz respeito ao desempenho de quatro threads: dois núcleos Skylake com suporte a Hyper-Threading são superados por quatro núcleos Gracemont em desempenho por cerca de 80% com consumo igual, e com a mesma velocidade consomem 80% mais energia.

No entanto, essas comparações não significam que os E-cores dos processadores Alder Lake são melhores do que o Skylake em todos os aspectos. Na verdade, as comparações da Intel fazem várias suposições. Em primeiro lugar, o desempenho dos núcleos é comparado apenas com uma carga inteira simples, para a qual, obviamente, os núcleos Gracemont são otimizados. Em segundo lugar, no caso de um teste de quatro threads, núcleos Skylake únicos se opõem a pares de núcleos Gracemont, que o Hyper-Threading não suporta. Mas, no entanto, a força óbvia da Gracemont é que seu desempenho ainda pode ser comparado ao Skylake, apesar do fato de serem várias vezes menores em área.

Isso é conseguido devido ao processamento profundo das antigas microarquiteturas com eficiência energética da Intel. Nas últimas duas gerações, Tremont e Gracemont, a parte de entrada do pipeline de execução mudou radicalmente e se tornou mais profunda e ampla, além do número de portas de execução ter aumentado significativamente. Além disso, a Gracemont até adicionou registros e unidades de execução de 256 bits para implementar os conjuntos de instruções AVX2 e AVX2-VNNI. Ou seja, os E-cores foram muito longe de seus predecessores com a microarquitetura Goldmont: não apenas o desempenho aumentou fundamentalmente, mas também as capacidades dos E-cores foram puxadas para os irmãos “grandes”.

Um decodificador duplo de seis entradas, que é capaz de decodificar dois fluxos a uma taxa de três instruções x86 por clock, apareceu no núcleo Tremont. Funcionou bem lá, e a Intel também o transferiu para a Gracemont. Mas na nova geração de microarquitetura, ele é complementado por um cache de instrução L1I de 64 KB mais espaçoso, que é ainda maior do que o cache L1I do produtivo núcleo Golden Cove. O aumento no tamanho do cache ocorreu simultaneamente com o aumento para 5000 entradas do buffer de destino de ramificação, que funciona de forma mais eficiente quando os destinos de ramificação estão no cache – isso levou a um aumento no desempenho da previsão de ramificação. Além disso, mais um mecanismo funciona com base no cache L1I – “decodificação sob demanda”, que substitui parcialmente o cache micro-operacional ausente em Gracemont e preserva parcialmente o histórico da decodificação anterior.

Além disso, a microarquitetura Gracemont fornece um bloco de colocação de instrução de cinco vias e um bloco de reordenação de instrução de oito portas, que funcionam com um buffer de reordenação de instrução que cresceu para 256 entradas. E então existem 17 portas de execução no pipeline – um domínio de execução verdadeiramente gigantesco em largura. E embora todas as portas neste caso sejam visivelmente mais simples do que em núcleos “grandes”, nas instruções de número inteiro este array pode de fato fornecer um valor IPC mais alto do que oito portas no núcleo Skylake. No entanto, você precisa entender que, apesar de sua largura, não mais do que cinco micro-ops por relógio podem ser carregados no domínio de execução da Gracemont ao mesmo tempo, e isso é o que limita o ritmo de execução do código do programa.

Existem quatro dispositivos inteiros de propósito geral independentes no domínio de execução Gracemont, e dois deles podem realizar operações de multiplicação e divisão. Além disso, o kernel possui os recursos necessários para realizar dois saltos por ciclo de clock. Para trabalhar com instruções vetoriais e números de ponto flutuante, Gracemont possui três portas, duas das quais são capazes de lidar com operações de multiplicação e divisão. Em geral, o projeto do domínio de execução de um núcleo com eficiência energética envolve o uso de um grande número de portas de execução altamente especializadas, enquanto o conceito é diferente em núcleos produtivos. Existem menos portas, mas são mais versáteis e focadas em operações mais heterogêneas.

Ao trabalhar com memória cache, o kernel Gracemont pode iniciar duas operações de carregamento e duas operações de descarregamento de dados por ciclo, no entanto, ao contrário dos núcleos P, essas operações são de 128 bits. O volume do cache L1D também é menor – apenas 32 KB. A organização do cache L2 também é diferente. Seu volume chega a 2 MB, mas é dividido em quatro núcleos localizados lado a lado e combinados em um único cluster. O cache L2 é conectado a cada um dos núcleos neste esquema por seu próprio canal de 512 bits. Um despachante especial é fornecido na microarquitetura para a operação conjunta de núcleos com cache L2, e o algoritmo de sua operação é configurado para distribuir uniformemente os recursos entre os núcleos, e não para garantir baixa latência para alguns threads separados. E isso reflete que o design dos E-cores é principalmente afiado para cargas multi-threaded.

A microarquitetura Gracemont assume que tais núcleos são montados em clusters quad-core que ocupam aproximadamente a mesma quantidade de espaço no cristal semicondutor Alder Lake que um núcleo produtivo Golden Cove. Isso torna possível adicionar um grande número de computadores relativamente simples aos processadores modernos, que, além disso, têm uma eficiência energética muito boa. Para maximizar essa ideia, a Intel reduziu a tensão de alimentação para os clusters E-core e, portanto, os núcleos Gracemont em Alder Lake irão operar em uma frequência relativamente baixa. No entanto, presume-se que, se necessário, seu desempenho pode ser dimensionado em uma ampla faixa – eles devem tolerar bem os aumentos de tensão e responder a eles com um aumento no limite superior da frequência permitida.

⇡#Processadores de desktop Alder Lake-S e plataforma LGA1700

Faltam apenas algumas semanas para a família de processadores Alder Lake-S, voltada para desktops de alto desempenho, chegar ao mercado, e você pode imaginar como será a linha correspondente agora. A estratégia da Intel para trazer Alder Lake-S ao mercado envolve o lançamento da plataforma e dos processadores para os entusiastas primeiro, enquanto modificações mais massivas e acessíveis aparecerão mais tarde. Isso significa que os processadores para desktop das séries Core i9, Core i7 e Core i5, bem como o único chipset carro-chefe Z690, chegarão primeiro ao mercado.

Para uso na primeira fase dos processadores de desktop, a Intel preparou um cristal semicondutor com 8 núcleos Golden Cove, dois clusters Gracemont quad-core e gráficos GT1 com 32 unidades de execução. Mas todo esse arsenal será usado exclusivamente nos processadores da série Core i9. Os representantes da série inferior receberão um número menor de núcleos, e a diferença entre o Core i9 e o Core i7 será determinada pelo número de E-cores, e na série Core i5, tanto os P-cores quanto os E-núcleos serão parcialmente desativado.

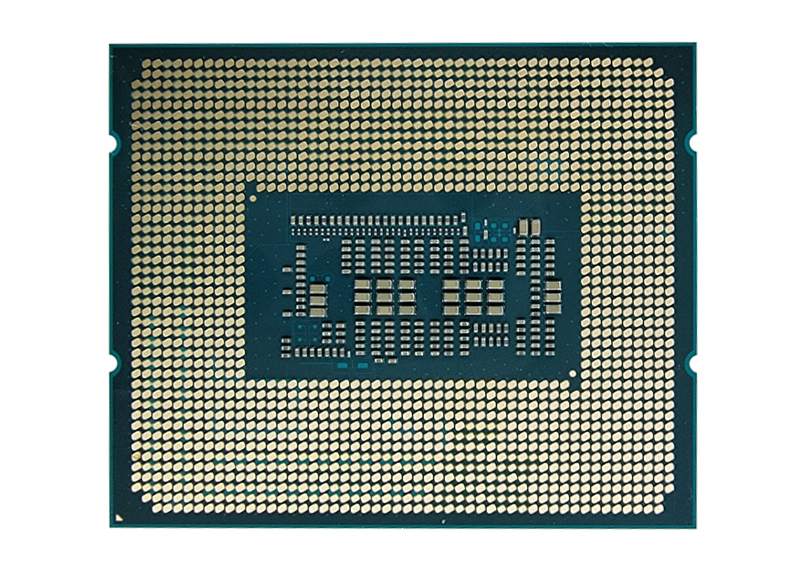

Amostras de Alder Lake-S. Fonte: Expreview.com

As velocidades de clock dos núcleos P em Alder Lake-S, presumivelmente, estarão no nível usual para processadores Intel: no modo turbo, eles serão capazes de subir cerca de 4,9-5,3 GHz com uma carga de thread único e 4,5-5,0 GHz – com multithread. Quanto aos E-cores, as frequências-alvo para eles são esperadas na faixa de 3,4-3,9 GHz. O pacote térmico dos novos processadores dificilmente surpreenderá ninguém: 125 W para modelos com multiplicadores desbloqueados e 65 W para os normais.

Mas aumentará visivelmente na quantidade de cache L3. Nos processadores de geração Rocket Lake e Comet Lake, cada núcleo tinha um bloco de cache L3 de 2 MB. Em Alder Lake, o volume de tais blocos adjacentes aos núcleos P aumentou para 3 MB. Os clusters quad-core de E-cores também são equipados com blocos de 3 MB, de modo que a quantidade máxima de cache L3 em modelos mais antigos de Alder Lake chegará a 30 MB. Ao mesmo tempo, o cache em si não é inclusivo, ou seja, o conteúdo da memória cache superior não é duplicado nele.

Separadamente, deve-se dizer sobre os preços. Em geral, a Intel não planeja alterar de forma perceptível sua política de preços. E isso significa que a série Core i9 terá um preço sugerido de cerca de $ 500- $ 600, os processadores Core i7 podem ser comprados por $ 350- $ 450 e o Core i5 será vendido por $ 200- $ 300. Em outras palavras, a empresa não acredita que a introdução de uma arquitetura híbrida e a adição de E-cores mereçam qualquer marcação perceptível.

As características estimadas dos primeiros representantes da série são apresentadas na tabela, mas deve-se ter em mente que esses dados são não oficiais e preliminares.

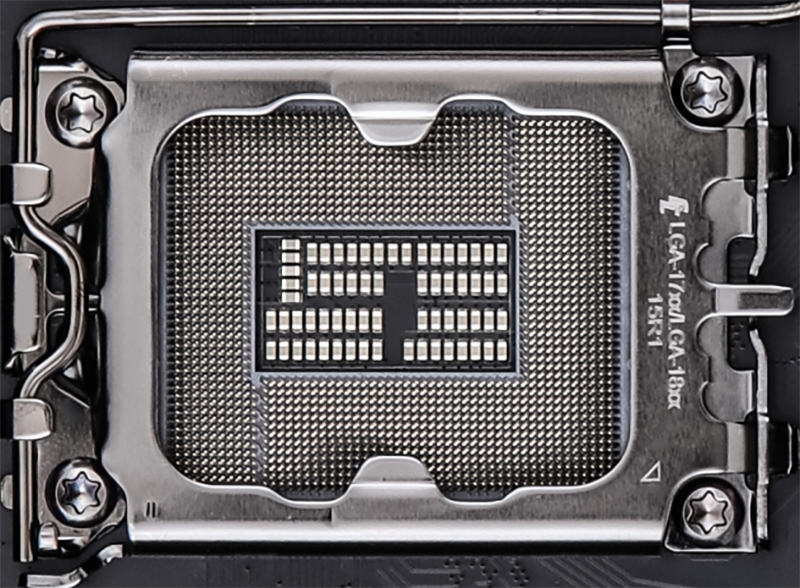

Os processadores desktop da família Alder Lake-S são projetados para uso em placas-mãe com o novo soquete LGA1700, que difere do atual LGA1200 não apenas no aumento do número de contatos, mas também em uma forma retangular em vez de quadrada e dimensões geométricas ligeiramente aumentadas . As mudanças devem-se principalmente ao surgimento de suporte para novos tipos de memória e à interface PCIe 5.0 e, em segundo lugar, devido ao esquema de alimentação mais complicado, uma vez que P-cores e E-cores operam em tensões diferentes.

Soquete do processador LGA1700. Fonte: bilibili.com

Além disso, a altura do processador muda junto com o soquete do processador – Alder Lake-S vai subir cerca de um milímetro a menos acima da placa-mãe do que seus predecessores. Isso exigirá o uso de sistemas de resfriamento com outras montagens para dissipação de calor e, portanto, os orifícios de montagem nas placas LGA1700 serão localizados de uma maneira ligeiramente diferente – um quadrado de 78 × 78 mm em vez de 75 × 75 mm. Portanto, a maioria dos coolers de computador antigos não funcionará com Alder Lake-S, pelo menos sem substituir o hardware.

Como o controlador de memória Alder Lake-S suporta SDRAM DDR4 e DDR5, as placas-mãe desses processadores serão lançadas com slots DIMM para uma ou outra memória. A princípio, as placas com suporte para SDRAM DDR5 obviamente serão representadas apenas por modelos caros, uma vez que tais módulos, após seu surgimento no mercado, custarão significativamente mais que o DDR4. No entanto, os entusiastas ainda podem preferir placas DDR5 DIMM, já que a nova memória é capaz de fornecer o dobro da largura de banda.

Amostra de Alder Lake-S. Fonte: pcinq.com

Para plataformas de desktop baseadas em Alder Lake-S, a Intel está preparando uma nova família de chipsets da série 600. Ele implementará oportunidades significativamente maiores para conectar dispositivos externos. Assim, o mais antigo dos futuros chipsets, o Z690, que chegará ao mercado primeiro, poderá até oferecer suas próprias pistas PCIe 4.0.

Além das 16 pistas PCIe 5.0 (para a placa de vídeo) e 4 pistas PCIe 4.0 (para o armazenamento), pelas quais o processador é responsável, 12 pistas do chipset PCIe 4.0 serão adicionadas aos sistemas baseados no Z690, que acabarão permitem a instalação de até quatro dos mais modernos drives NVMe. Além disso, o Z690 também possui suporte para 16 pistas PCIe 3.0, ou seja, no total, o chipset possui 28 pistas PCIe, e toda a plataforma possui 48 pistas. Outra mudança importante, diretamente relacionada ao advento do PCIe 4.0 no chipset, é a transferência da conexão entre o processador e o chipset para a interface DMI 4.0 x8 com o dobro da largura de banda. Isso fornecerá largura de banda suficiente para todo o conjunto de pistas do chipset PCIe.

Lógica do sistema definida Intel Z690. Fonte: pcinq.com

Entre outras melhorias, o Z690 também pode ser notado um aumento no número de portas 20-Gigabit USB 3.2 Gen 2 × 2 e o surgimento (até agora apenas em teoria) de suporte para módulos Wi-Fi 7 via interface CNVi.

⇡#Conclusões

É difícil imaginar que nível de desempenho os processadores Alder Lake-S oferecerão no final das contas. Não houve vazamento de informações sobre esta pontuação, o que realmente poderia ser confiável, até o momento, e as estimativas de desempenho específico de microarquiteturas feitas pelo próprio fabricante não fornecem orientações específicas.

Só podemos dizer com confiança sobre uma coisa: Alder Lake-S será definitivamente (e significativamente) mais rápido do que seus antecessores. Os núcleos produtivos da Golden Cove são os responsáveis por isso, e certamente não irão falhar, pois contêm todo um conjunto de melhorias que aumentam diretamente a produtividade. O número de tais núcleos não será menor do que em Rocket Lake, e as frequências de clock também não diminuirão. No entanto, não se esqueça de que os núcleos Gracemont com eficiência energética, que também parecem muito bons, são adjacentes aos núcleos Golden Cove em processadores futuros, mas é bastante difícil prever como a arquitetura híbrida se comportará na realidade. A Intel afirma que os sistemas operacionais modernos são capazes de lidar com diferentes tipos de núcleos, mas, na verdade, tudo isso precisa de uma verificação completa.

Além disso, DDR5 SDRAM também pode fazer ajustes no desempenho da plataforma. Mudar para tipos de memória mais novos com larguras de banda maiores geralmente se traduz em aumentos dramáticos na latência, e mudar de DDR4 para DDR5 é exatamente isso. Portanto, por enquanto, nos absteremos de quaisquer previsões e aguardaremos o final de outubro, quando a Intel divulgará detalhes adicionais sobre a promissora família de CPUs.

A principal conclusão que precisa ser feita hoje é qualitativa: a Intel saiu de uma longa hibernação e lançou o processo de intensificação das inovações. O progresso feito no segmento de desktop é impressionante. A família de chips Rocket Lake, que usava o núcleo Cypress Cove, chegou ao mercado há apenas seis meses, mas hoje já estamos falando sobre seus sucessores – os núcleos Golden Cove e os fundamentalmente novos processadores Alder Lake-S.

Além disso, agora a empresa não vai mais parar. Já no final do próximo ano, ela planeja apresentar a próxima grande atualização para a plataforma do consumidor junto com os processadores Meteor Lake, onde o número de inovações definitivamente não será menor do que em Alder Lake. Nele, a Intel começará a usar uma topologia de bloco (multi-chip), cristais semicondutores lançados com a tecnologia Intel 4 e novas iterações de microarquiteturas de processador. Portanto, artigos como este dedicado a novos designs de processadores agora aparecerão em nosso site com muito mais frequência.