A TSMC, na conferência European Technology Symposium 2024, compartilhou novos detalhes sobre o progresso do desenvolvimento de chips básicos para memória de alto desempenho HBM4. Um dos principais recursos da nova tecnologia de memória será a transição de uma interface de 1024 bits para uma interface de 2048 bits. No entanto, perceber isso exigirá tecnologias de empacotamento mais avançadas do que as usadas atualmente para produzir e integrar memória HBM.

Fonte da imagem: TSMC

Como parte de sua apresentação, a TSMC compartilhou novos detalhes sobre os chips que formarão a base das pilhas de memória HBM4. A empresa vai utilizar dois de seus processos técnicos ao mesmo tempo para produzir chips básicos – N12FFC+ (12 nm) e N5 (5 nm). Cada um tem seus próprios méritos, mas ambos servirão ao mesmo propósito – integrar memória HBM de quarta geração de alta velocidade em futuros processadores de IA e HPC.

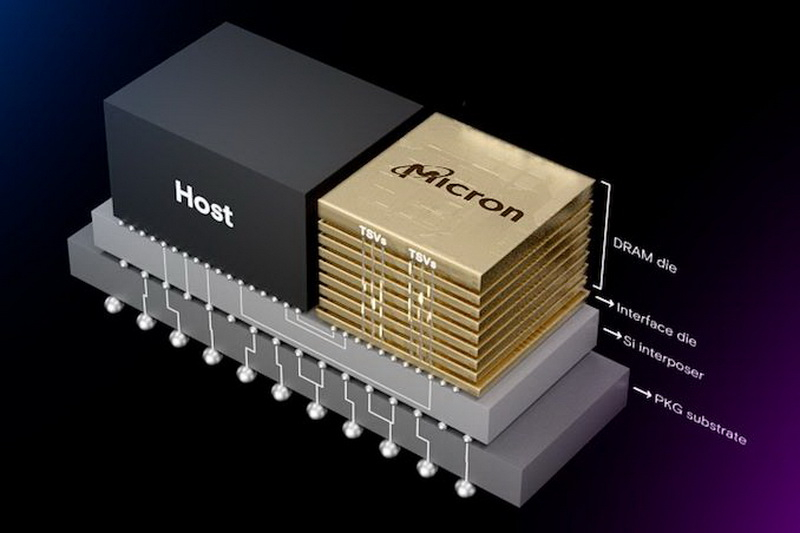

«Estamos colaborando com os principais parceiros de desenvolvimento de memória HBM (Micron, Samsung, SK Hynix) em nós de ponta para integrar totalmente a pilha HBM4. Uma matriz base baseada no processo N12FFC+ econômico proporcionará ganhos de desempenho ao HBM4, enquanto uma matriz base baseada em N5 permitirá que mais componentes lógicos sejam colocados no chip e menor consumo de energia de memória”, observa a empresa.

O chip de memória HBM4 básico, fabricado com a tecnologia TSMC N12FFC+ (12nm FinFet Compact Plus), será usado para instalar pilhas de memória HBM4 em um adaptador de silício próximo ao SoC. A TSMC observa que o N12FFC+ permite criar pilhas de memória em configurações 12-Hi (doze camadas, 48 GB) e 16-Hi (dezesseis camadas, 64 GB) com uma taxa de transferência de cada pilha de mais de 2 TB/s.

As matrizes básicas HBM4 no processo N12FFC+ serão usadas para produzir produtos system-in-package (SiP) usando as avançadas tecnologias de embalagem CoWoS-L ou CoWoS-R da TSMC. De acordo com a TSMC, o HBM4 pode atualmente atingir taxas de dados de até 6 GT/s a 14 mA.

«Também estamos otimizando nossas tecnologias de embalagem CoWoS-L e CoWoS-R para HBM4. Eles envolvem o uso de mais de oito camadas de interconexão para garantir que as mais de 2.000 conexões dentro do HBM4 sejam roteadas com integridade de sinal adequada”, disse TSMC.

A TSMC está trabalhando com os parceiros EDA Cadence, Synopsys e Ansys para garantir a integridade do sinal, precisão térmica e redução da interferência eletromagnética (EMI) no novo silício base HBM4.

Como alternativa mais avançada, a TSMC poderá oferecer aos seus clientes a tecnologia de processo N5 para produção de bases para pilhas de memória HBM4. Este nó permitirá colocar ainda mais componentes lógicos na pilha HBM4, reduzir o consumo de energia da memória e aumentar ainda mais seu desempenho. Mas talvez a vantagem mais importante do N5 seja que ele permite passos de interconexão muito finos no HBM4, da ordem de 6 a 9 mícrons. Por sua vez, isso permitirá que os chips de memória HBM4 sejam integrados diretamente nos chips lógicos. Isso deve aumentar o desempenho e a largura de banda da memória, o que será útil na produção de chips de IA.