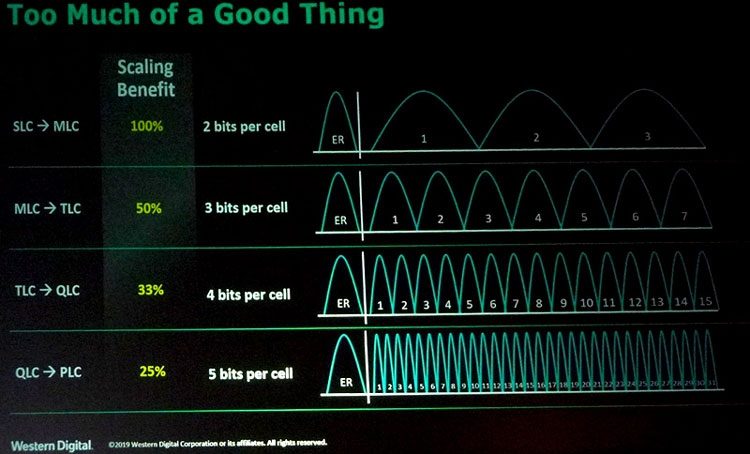

Na reunião atual de desenvolvimento de memória flash, os desenvolvedores e fabricantes não apenas se gabaram de adicionar camadas ao 3D NAND, mas também demonstraram outras possibilidades para aumentar a capacidade dos chips. Agrada. A indústria tem um backlog e irá implementá-lo sistematicamente.

O próximo passo é gravar 5 bits em cada célula (PC Watch)

A dupla da Toshiba e da Western Digital se apresentou especialmente bem. No outro dia, dissemos que esses parceiros comerciais NAND-flash propuseram aumentar a capacidade de memória flash em 25%, mudando para uma célula com cinco bits de gravação (NAND PLC). Outra proposta foi uma aplicação ainda mais interessante para um aumento de 100% na capacidade de flash arrays sem aumentar a área de cristais e o número de camadas. Os custos de produção não aumentarão ou se tornarão um pouco mais, e a capacidade aumentará duas vezes. Qual é o segredo?

Divida e ganhe (PC Watch)

A resposta é simples. Para duplicar a capacidade do chip, é necessário dividir cada linha do dicionário em duas e, consequentemente, dividir fisicamente cada célula da memória nos canais 3D NAND verticais. É possível dividir em dois uma célula com uma porta flutuante (FG) ou uma célula com uma armadilha de carga (armadilha de carga, CT). A empresa já está realizando experimentos com estruturas semelhantes e esperando o desenvolvimento bem-sucedido da tecnologia até o nível de produção comercial.

Uma diminuição no volume físico da célula reduzirá, de forma previsível, o espaço para elétrons (carga) em cada um deles, o que reduzirá a confiabilidade e a resistência ao desgaste. Mas isso pode ser compensado por complicar o controlador (correção de erro) ou devido a uma tecnologia de processo maior. Em geral, as empresas não são as primeiras a resolver tais problemas. Mas vamos prestar atenção a um aspecto que a Toshiba escolheu para permanecer em silêncio – esta é uma questão de afiliação ao desenvolvimento.

Comparação de 3D NAND com obturadores GAA (redondos) e Macronix SGVC (metades)

A tecnologia de separação física de células verticais em duas com duas linhas de vocabulário e portões separados foi ativamente desenvolvida, mas nunca foi trazida à produção comercial pela empresa taiwanesa Macronix. Pode-se imaginar que o desenvolvimento do Macronix é baseado no legado da empresa alemã Qimonda (Infineon). Em qualquer caso, a Macronix em uma ação judicial forçou a Toshiba a pagar US $ 40 milhões por violação de patente. Trata-se apenas de tecnologia sobre a organização separada de células em pilhas verticais. A propósito, como a Macronix avançou bastante em sua pesquisa, o surgimento dessa tecnologia no mercado pode ocorrer em um futuro previsível, e não depois de muitos anos.

.