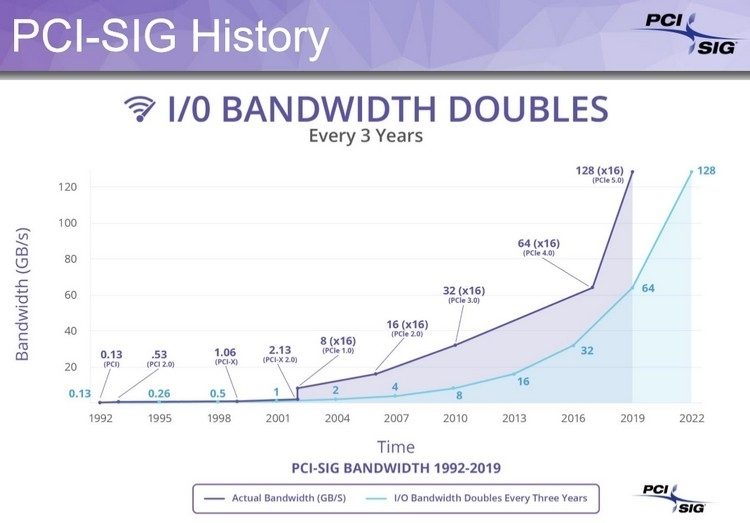

Como você sabe, o curador do PCI Express, o grupo inter-industrial PCI-SIG, está com pressa para acompanhar o cronograma de introdução de uma nova versão do barramento PCI Express usando as especificações da versão 5.0. A versão final das especificações do PCIe 5.0 foi aprovada nesta primavera e, já no novo ano, os dispositivos com suporte para o barramento atualizado devem aparecer no mercado. Lembre-se de que, em comparação com o PCIe 4.0, a velocidade de transferência na linha PCIe 5.0 dobrará para 32 gigatransações por segundo (32 GT / s).

Especificações são especificações, mas para a implementação prática da nova interface, são necessários silício e blocos de trabalho para o licenciamento de desenvolvedores de controladores de terceiros. Uma dessas soluções ontem e hoje em uma conferência em Taipei foi apresentada pela Astera Labs, Synopsys e Intel. Argumenta-se que esta é a primeira solução abrangente que está completamente pronta para implementação na produção e licenciamento.

A plataforma mostrada em Taiwan usa um chip Intel experiente, um controlador Synopsys DesignWare e uma camada física da empresa para o PCIe 5.0, que pode ser adquirido sob licença, além dos retimers do Astera Labs. Retimers são chips que restauram a integridade dos pulsos de clock na presença de interferência ou no caso de um sinal fraco.

Como você entende, com um aumento na taxa de transmissão de dados em uma linha, a integridade do sinal tende a zero à medida que as linhas de comunicação se alongam. Por exemplo, de acordo com as especificações da linha PCIe 4.0, o alcance da transmissão sem o uso de conectores na linha é de apenas 30 cm. Para a linha PCIe 5.0, essa distância será ainda menor e, mesmo a essa distância, os temporizadores devem ser incluídos no circuito do controlador. O Astera Labs conseguiu desenvolver esses retimers que podem funcionar tanto na interface do PCIe 4.0 quanto como parte da interface do PCIe 5.0, demonstrada na conferência.

.