O TSMC é o maior fabricante do mundo com quase 500 clientes. A empresa pode servir quase qualquer cliente com praticamente quaisquer demandas. Ao mesmo tempo, deve estar à frente de todos os concorrentes tanto em termos de possibilidades quanto de tecnologias. Os volumes de produção TSMC são improváveis de desafiar nos próximos anos. Em relação ao desenvolvimento de normas avançadas N2, N3 e N4, a empresa também vai tudo de acordo com o plano.

No início deste ano, o TSMC aumentou significativamente seu orçamento de despesas de capital para 2021 a 5-28 bilhões, e agora aumentou ainda mais de cerca de 0 bilhões dentro de seu plano de três anos para gastar 00 bilhões em desenvolvimento de produção, pesquisa e desenvolvimento .

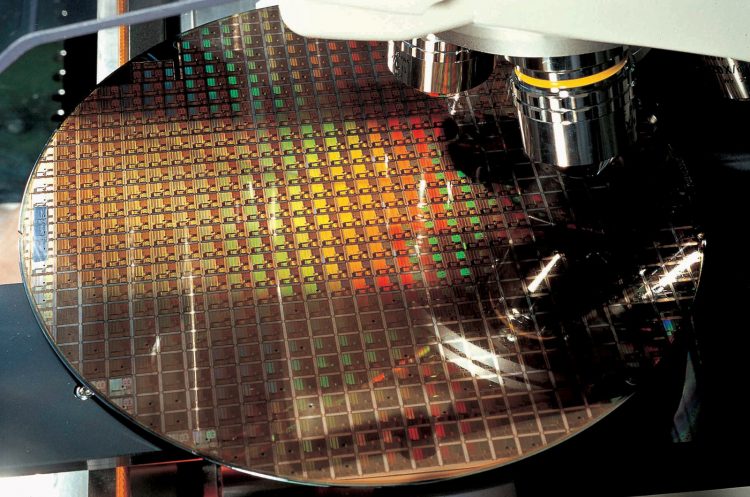

Cerca de 80% do orçamento TSMC 0 bilhões deste ano serão gastos em expansão de capacidade para tecnologias avançadas como 3-nm, 4/5-nm e 6/7-nm. Os analistas da China renascentistas títulos acreditam que a maior parte do dinheiro alocado para normas avançadas será usada para expandir a capacidade de N5 a 110-120 milha de silício por mês (WSPM) até o final do ano.

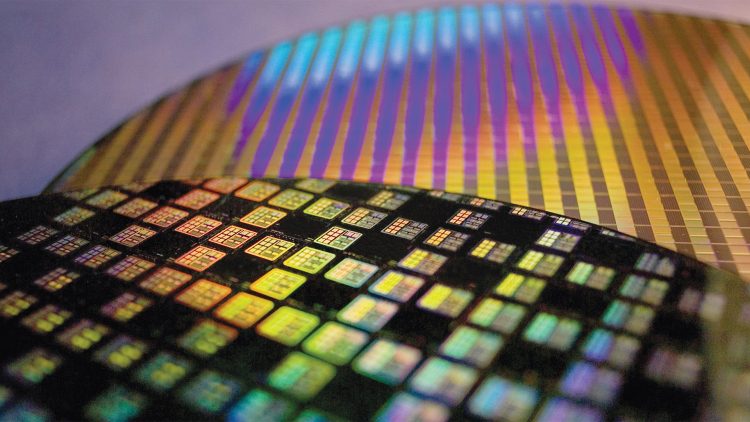

O TSMC foi a primeira empresa que iniciou os chips de produção em larga escala (HVM) usando a tecnologia N5 (5 Nm) em meados de 2020. Originalmente, esses serviços usados apenas duas empresas – Apple e Huawei Hisilicon. Entregas para este último param em 14 de setembro, que deixou a Apple todos os poderes avançados. Até o momento, mais e mais clientes estão prontos para começar a digitar chips nos padrões N5, portanto, a implementação desse processo aumenta. O TSMC diz que o uso das tecnologias da família N5 (incluindo N5, N5P e N4) planeja mais clientes do que apenas alguns meses atrás.

O fabricante prevê que, de acordo com os resultados de 2021, o N5 lhe trará cerca de 20% de todos os rendimentos da produção de placas de silício. O TSMC observa mais interesse em clientes em relação aos padrões de 5 nm e 3 nm do que em relação a 7-NM em uma fase semelhante. A empresa espera que a demanda por N5 só cresça no futuro próximo devido a smartphones e soluções de alto desempenho.

O interesse pelo TSMC N5 não é surpreendente: analistas da China Renaissance estimaram que o processo técnico pode oferecer cerca de 170 milhões de transistores por milímetro quadrado (MTP / MM2) – estes são os regulamentos mais de alta qualidade hoje. Para comparação: a Samsung 5LPE pode propor uma densidade de cerca de 125-130 MTP / MM2 e as normas Intel de 10 nm são de cerca de 100 mm / mm2.

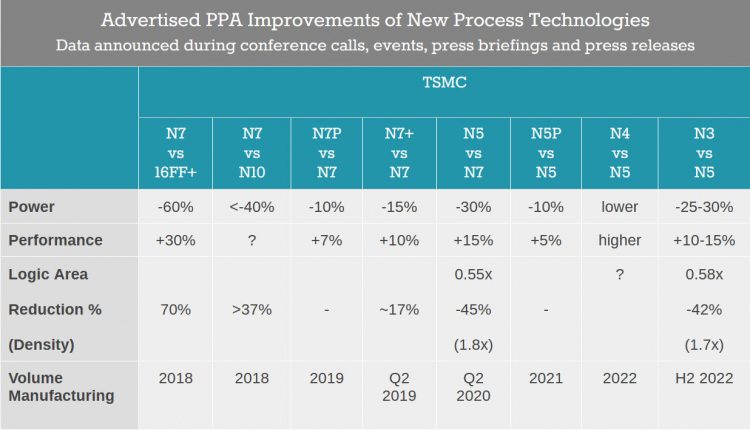

Nas próximas semanas, o TSMC vai começar a produzir chips usando uma versão melhorada de sua tecnologia de 5 nm chamada N5P, que promete um aumento na frequência a 5% ou redução do consumo de energia para 10% (com a mesma complexidade do cristal) . A tecnologia não requer investimentos significativos em recursos de engenharia ou tempo de ciclo de design mais longo, portanto, qualquer cliente TSMC, que já tem n5 chips, pode imprimi-los usando o N5P.

A família Technology TSMC N5 também inclui o processo técnico N4 (4 Nm) – com sua ajuda, os primeiros chips começarão a ser impressos no final deste ano, e a produção em massa é esperada em 2022. Esta tecnologia é projetada para fornecer vantagens adicionais em relação ao consumo de energia, desempenho e densidade em comparação com o N5, mas manter os mesmos princípios de design, infraestrutura de design, programas de modelagem de especiarias. Enquanto isso, desde que em N4, o uso de ferramentas de litografia na faixa ultravioleta extrema (EUV) é ainda mais expandindo, reduzirá o número de camadas de mascaramento, etapas de produção e, conseqüentemente, riscos e custos.

Em 2022, o maior fabricante de contratos do mundo lança seu processo de produção inteiramente novo – N3 (3 NM), que continuará a usar os transistores FineFet. Em comparação com o atual processo técnico N5, promete o crescimento do desempenho em 10-15% (na mesma potência e complexidade) ou redução do consumo de energia em 25-30% (na mesma frequência e complexidade). As novas normas também aumentarão a densidade da colocação de transistores em 1,1-1,7 vezes, dependendo das estruturas (1.1x – para analógico, 1,2x – para SRAM, 1,7x – para lógica).

O N3 também aumentará o número de camadas EUV, mas continua a usar litografia em uma gama ultravioleta profunda (DV). Além disso, uma vez que a tecnologia continuará a usar os transistores Finfet, não exigirá uma nova geração de ferramentas de automação de design eletrônico (EDA), reciclada a partir do zero e desenvolvendo chips completamente novos, o que pode ser uma vantagem competitiva em comparação com os nonoragens 3GAE no transistor Gaafet / Mbcfet Samsung. A produção arriscada é agendada para 2021 e massiva no segundo semestre de 2022.

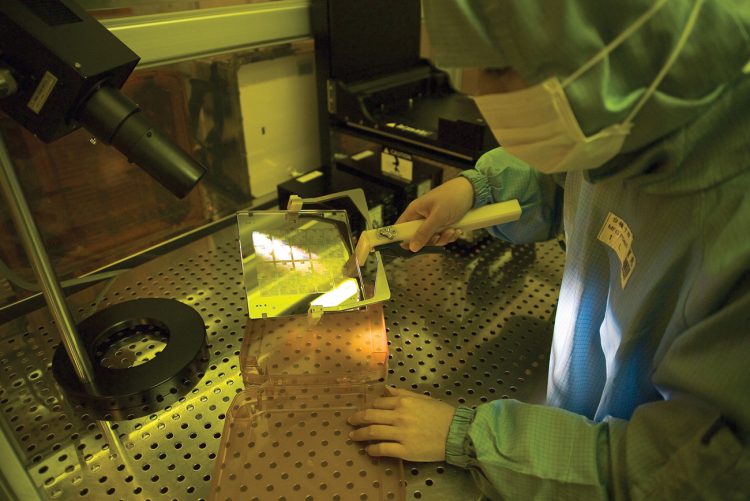

A estrutura dos transistores GaAfers (portão-em volta do FET) permanece nos planos de desenvolvimento do TSMC. Espera-se que a empresa usará um novo tipo de transistores no seguinte processo técnico importante N3 (presumivelmente, N2, 2 Nm). Vale ressaltar que o TSMC expande as possibilidades de pesquisa e desenvolvimento na Fab 12 Enterprise, onde o trabalho está atualmente em andamento no N3, N2 e processo técnico mais avançado.