As principais empresas de tecnologia, incluindo AMD, Arm, Google, Intel, Meta, Microsoft, Qualcomm, Samsung e TSMC, anunciaram a formação de um consórcio para desenvolver e implementar em conjunto um padrão de interconexão de chiplet aberto, Universal Chiplet Interconnect Express (UCIe). O resultado deste trabalho foi a primeira versão da especificação UCIe 1.0.

O objetivo do padrão é simplificar a possibilidade de criar microcircuitos multi-chip usando chips semicondutores de diferentes fabricantes. A especificação UCIe 1.0 padroniza as conexões entre chips nos níveis físico e lógico e define, entre outras coisas, aspectos de sua implementação como protocolo elétrico, modelo de software, procedimento de teste de compatibilidade, etc. O protocolo UCIe 1.0 é baseado nos padrões da indústria PCI Express e Compute Express Link.

Assim, os principais desenvolvedores e fabricantes de semicondutores se uniram para formar um único ecossistema para a criação de chips complexos, que, como esperado, no futuro, terão principalmente um design multi-chip. Seguir a especificação UCIe 1.0 permitirá o design livre de soluções combinadas compostas por chiplets de diferentes desenvolvedores, produzidos em diferentes fábricas de semicondutores usando diferentes processos técnicos.

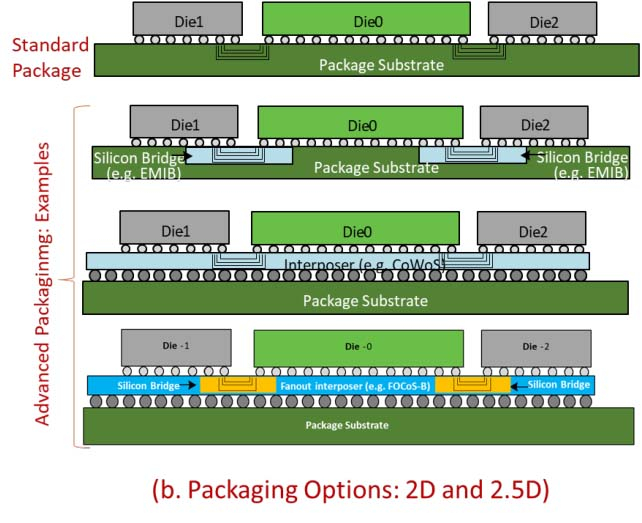

A especificação UСIe 1.0 leva em consideração a existência de vários pacotes de chiplet – tanto 2D padrão quanto 2.5D mais avançado (usando chips de conexão em ponte). É óbvio que no futuro a especificação se expandirá para chipsets 3D completos.

O uso de protocolos comuns PCIe e CXL no nível lógico permite aos desenvolvedores obter conexões flexíveis e compatíveis com alta largura de banda e baixa latência, que, em termos de velocidade, também são adequadas para trabalhar com memória e blocos de E/S. Além disso, a especificação UCIe pressupõe a capacidade de conectar dispositivos fora dos chips, o que permite organizar comunicações elétricas e ópticas com componentes externos.

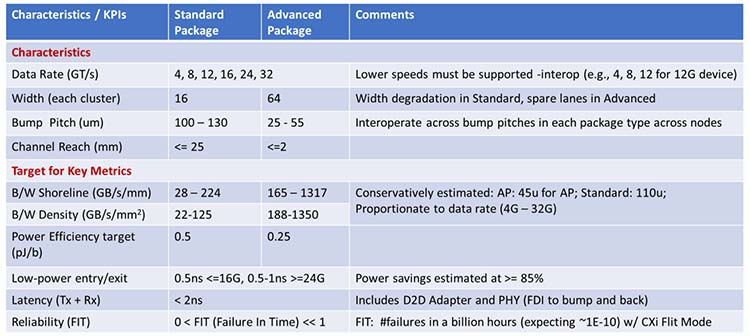

A especificação UCIe 1.0 define a taxa de transferência de dados entre chips (de 4 a 32 bilhões de transações por segundo), latência (menos de 2 ns), largura do barramento (de 16 a 64 bits dependendo do pacote), densidade de contato (distância entre contatos de 25 a 130 µm) e o comprimento dos condutores de conexão (até 25 mm). Naturalmente, os chipsets 2.5D têm indicadores de desempenho mais altos, mas exigem condutores mais curtos. Em geral, os chipsets 2D são limitados a 125 GB/s por mm2, enquanto os chipsets 2.5D podem ter conexões de até 1350 GB/s por mm2 de área de matriz.

Vale lembrar que a Intel já havia proposto um padrão aberto para conexão de chiplets – Advanced Interconnect Bus (AIB) – ele ainda é usado em conjunto com a tecnologia EMIB. Mas não é compatível com UCIe 1.0. Em vez disso, o consórcio decidiu usar mais opções PCIe e CXL produzidas em massa, portanto, posteriormente, a Intel mudará sua implementação de conexões entre chips – a empresa confirmou que está pronta para isso.

O consórcio UCIe também está aberto a outras empresas que atualmente não fazem parte dele. Assim, a Nvidia, que não está entre os fundadores da UСIe, poderá ingressar no consórcio posteriormente.