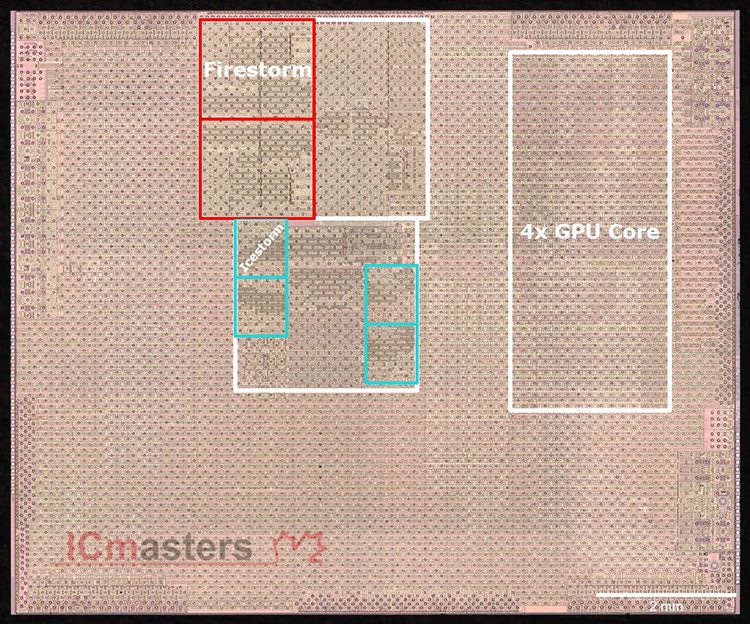

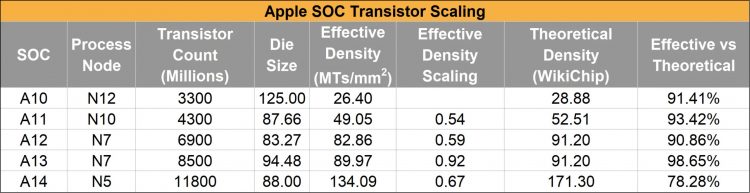

ICmasters espiou embaixo da embalagem do processador Apple A14 Bionic. O tamanho da matriz agora é conhecido e é de 88 mm2. Apesar de ter uns impressionantes 11,8 bilhões de transistores no chip, o tamanho da matriz é incrivelmente pequeno graças ao processo de 5 nm da TSMC. Mas nem tudo é tão simples.

Os sistemas de chip único da Apple atingiram mais de 90% da densidade teórica do processo no passado. Eles mostraram essa geração bem menor: a densidade real dos transistores em A14 é de 78% em relação à teórica. Apesar da TSMC reivindicar um corte de matriz de 1,8x para o N5 de 5 nm em comparação com o N7, a Apple alcançou apenas 1,49x a geração anterior nesta métrica.

E isso não é uma falha da TSMC ou da Apple. Ambas as empresas são líderes reconhecidas na fabricação e desenvolvimento de chips semicondutores, respectivamente. O problema com a incapacidade de converter a densidade teórica em densidade efetiva é devido à parada lenta da escala SRAM. SRAM é amplamente utilizado em processadores, tanto para registradores quanto para cache. Geoffrey Yeap, da TSMC, afirma que esse sistema SoC móvel típico hoje é 60% lógico, 30% SRAM e 10% analógico I / O.

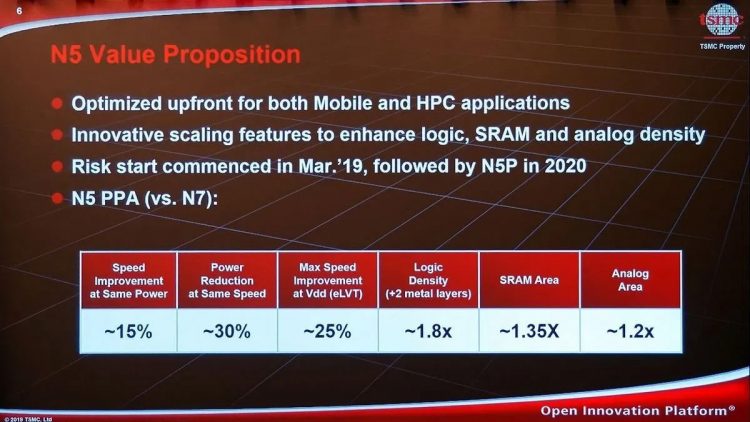

O fluxo de trabalho do TSMC N5 difere dos regulamentos anteriores, mostrando sinais de desaceleração do dimensionamento SRAM. Se a lógica pode ser condensada 1,8 vezes, então para SRAM esse número foi apenas 1,35 vezes. E mesmo esse valor está superestimado: no final será ainda menor quando outros esquemas auxiliares forem levados em consideração. A SemiAnalysis acredita que essa tendência continuará com as novas regulamentações de semicondutores.

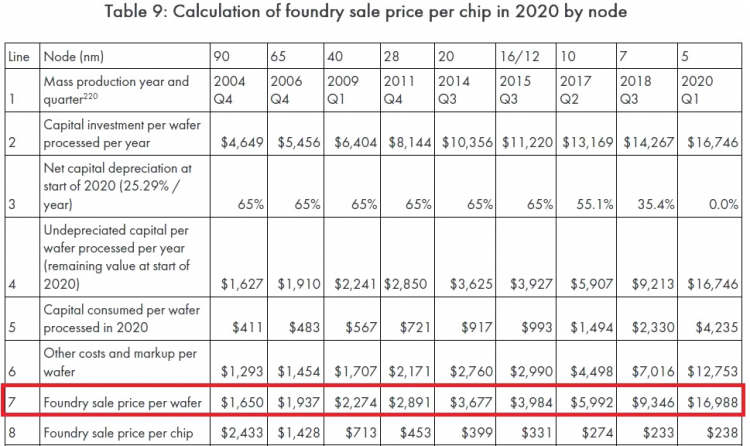

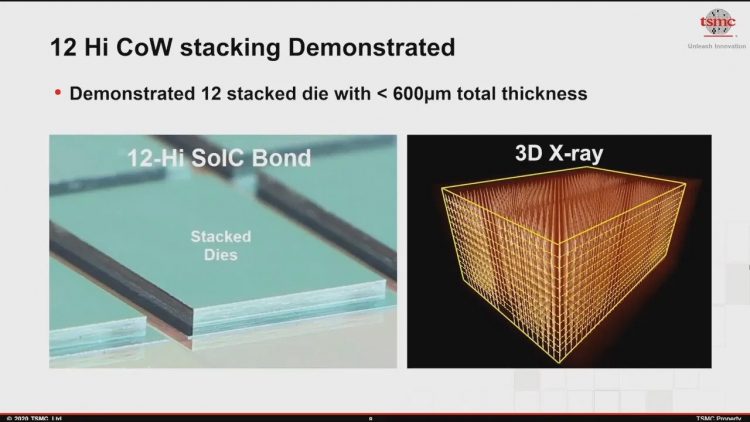

TSMC e Samsung já demonstraram camadas 3D SRAM para resolver o problema de densidade, mas esta tecnologia é uma solução mais cara. A escala de custos diminui drasticamente. Considerando que o preço dos wafers de silício TSMC N5 já é de cerca de 7 mil por um, é claro que o custo dos transistores não caiu. Mesmo se a escala de SRAM continuasse, o custo do transistor ainda permaneceria o mesmo de N7 para N5.