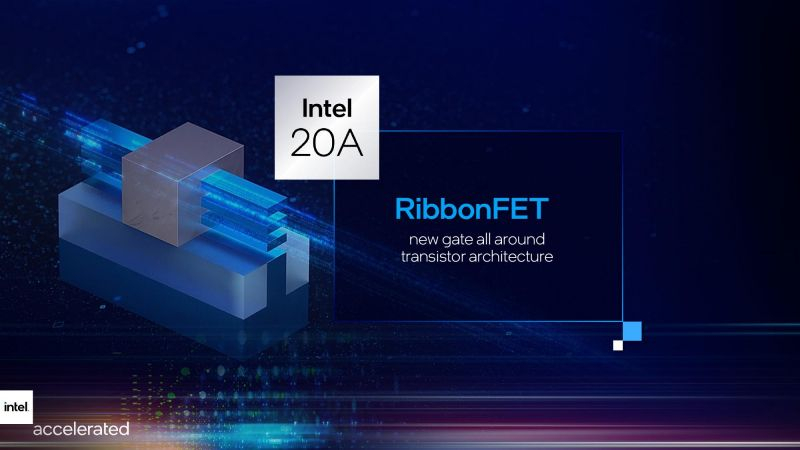

No último ano e meio, a Intel tem dito literalmente em cada esquina que pretende recuperar sua liderança tecnológica no campo da litografia até 2025. A essa altura, ela dominará o processo Intel 18A e, um ano antes, como parte da tecnologia 20A, começará a usar transistores com estrutura RibbonFET e circuito PowerVIA com fonte de alimentação na parte traseira do chip. Com base nos novos comentários dos representantes da TSMC, o concorrente taiwanês da Intel oferecerá a seus clientes as inovações mais recentes não antes de 2026.

Fonte da imagem: Intel

Na última conferência de relatórios trimestrais, o CEO da TSMC, CC Wei, disse que o processo N2 está sendo dominado pela empresa em total conformidade com o cronograma e será introduzido na produção em massa em 2025. A TSMC, no âmbito da tecnologia N2, usará uma nova estrutura de transistores com as chamadas nanofolhas (com porta circular) – a Intel, por outro lado, espera apresentar sua variedade chamada RibbonFET, com uma boa combinação de circunstâncias, já em 2024. Segundo o responsável pela TSMC, a tecnologia nanosheet vai oferecer aos clientes da empresa dentro das normas N2 a melhor combinação de desempenho e consumo de energia do mercado, bem como a maior densidade de transistores. Isso permitirá que a TSMC fortaleça sua liderança tecnológica quando o processo N2 entrar no mercado, de acordo com a empresa.

No entanto, deve-se observar que a Intel apresentará sua estrutura RibbonFET como parte da tecnologia de processo 20A no próximo ano – pelo menos no nível do protótipo. Desse ponto de vista, dada a menção dos representantes da TSMC sobre a introdução de nanofolhas em 2025, a fabricante de chips americana pode reivindicar a liderança em termos de introdução de tal inovação.

O CEO da TSMC lembrou de passagem que, como parte da família de tecnologia de processo N2, a empresa vai introduzir um circuito de energia na parte de trás do chip. Segundo ele, essa inovação será mais procurada no segmento de computação de alto desempenho. Ele aumentará a velocidade de comutação dos transistores em 10–12% e aumentará a densidade dos transistores em 10–15% em comparação com o caso base N2. Tecnicamente, a TSMC oferecerá esse esquema de alimentação de chip no segundo semestre de 2025, mas estará disponível para os consumidores em produção em massa apenas em 2026. Isso significa que também aqui a TSMC ficará atrás da Intel, aliás, por um ano e meio ou dois de uma vez, se não houver atrasos imprevistos nos planos desta última.

O chefe da TSMC acrescentou que a empresa está vendo um grande interesse dos clientes na família N2 de processos técnicos, tanto de desenvolvedores de chips de alto desempenho quanto do segmento de smartphones. Durante uma conversa com analistas em um evento de reportagem, os representantes da TSMC foram forçados a admitir que, à medida que a empresa muda seus processos técnicos, é capaz de aumentar a velocidade dos transistores em uma quantidade cada vez menor. No âmbito dos processos técnicos N2, também não será possível obter um aumento perceptível no desempenho pelos padrões anteriores, mas os clientes têm se concentrado cada vez mais em melhorar a eficiência energética, então a empresa decidiu prestar a devida atenção a essa otimização ao dominar essa tecnologia litográfica. No segmento de data center, de acordo com o chefe da TSMC, isso é muito apreciado.