O fabricante contratado de produtos semicondutores TSMC, que controla mais da metade do mercado de serviços relacionados, no Simpósio de Tecnologia anual, revelou detalhes não apenas sobre a tecnologia 3nm, mas também sobre novos desenvolvimentos.

Fonte da imagem: AnandTech

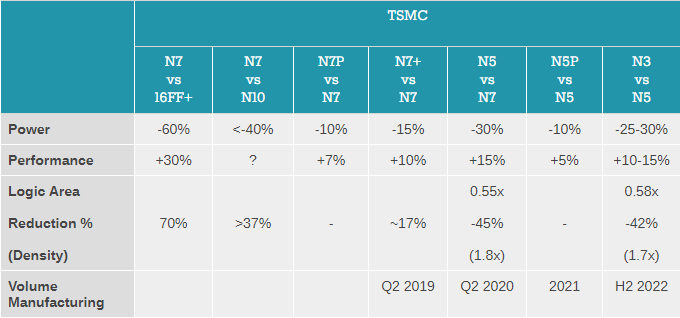

Em primeiro lugar, a empresa considerou necessário anunciar mais uma vez que não se prevêem atrasos no desenvolvimento da tecnologia 3nm. A produção piloto de chips de 3nm será lançada no próximo ano, e a empresa alcançará a fase de produção em massa no segundo semestre de 2022. Antes disso, o processo técnico de 5 nm também passará por várias etapas em seu desenvolvimento.

Fonte da imagem: AnandTech

Produtos de 5nm de primeira geração já estão sendo produzidos. Eles fornecem um aumento de 15% na velocidade do transistor em comparação com produtos de 7 nm, ou podem reduzir o consumo de energia em 30%, mantendo o mesmo desempenho. Ao mesmo tempo, a densidade de colocação dos transistores aumentou 1,8 vezes em comparação com o processo técnico de 7 nm.

A segunda geração do processo N5P de 5 nm chegará à produção em massa no próximo ano. Isso aumentará a velocidade dos transistores em 5% ou reduzirá o consumo de energia em dez por cento. O chamado processo técnico de 4 nm (N4) também foi preparado a partir do TSMC, que se tornará uma alternativa mais barata ao de 3 nm. A produção piloto de produtos de 4 nm começará no quarto trimestre do próximo ano, a produção em massa apenas em 2022.

O desenvolvimento da tecnologia de processo de 5 nm em termos de densidade de defeitos está agora um quarto adiantado em relação ao cronograma inerente à tecnologia de 7 nm. Se falamos da tecnologia de processo 3nm realizada pela TSMC, a empresa vai contar com as estruturas FinFET já comprovadas, ao contrário da Samsung, que está experimentando os chamados transistores GAA (gate-all-around, “completamente cercado por gates”).

A tecnologia de processo de 3 nm aumentará a velocidade dos transistores em 10-15% em relação a 5 nm ou reduzirá o consumo de energia em 25-30% com o mesmo desempenho. A densidade dos transistores deve aumentar 1,7 vezes. As células de memória SRAM na transição para uma tecnologia de processo de 3 nm aumentarão a densidade dos elementos em 20%, os componentes analógicos podem ser limitados a um aumento na densidade em 1,1 vezes.

A TSMC vai conquistar a era “após 3 nm” com a ajuda de materiais alternativos, não apenas o silício. Nanotubos e nanofios de carbono devem ser usados nesta área. A TSMC vem se desenvolvendo nessa direção desde 2019, mas o conservadorismo em relação à tecnologia de processo de 3 nm sugere que a empresa apresentará apenas as soluções mais comprovadas e confiáveis na produção em massa.