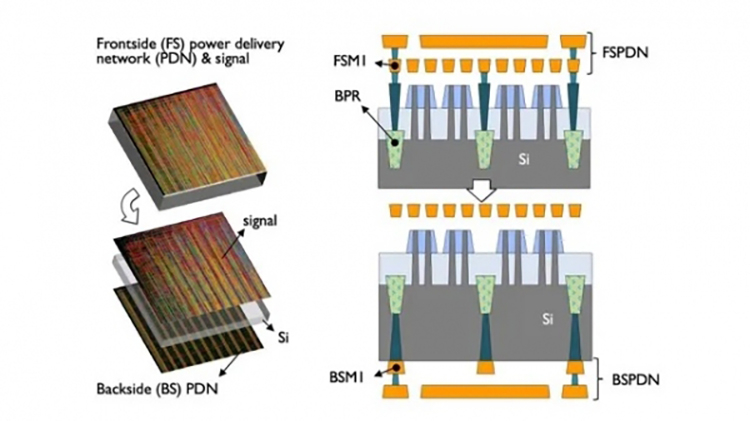

A Samsung planeja usar uma tecnologia chamada Back Side Power Delivery Network (BSPDN) em seu processo de fabricação para seus chips de 2 nm. Esta tecnologia foi apresentada na semana passada pelo pesquisador Park Byung-jae na conferência SEDEX 2022 organizada pela Samsung.

Fonte da imagem: IMEC

Tecnicamente, o BSPDN não muda a forma como os transistores são colocados em um chip, mas é uma evolução do design do chiplet usado pela Samsung, Intel e TSMC, e é uma evolução de tecnologias como FinFET, GAA e MBCFET.

O BSPDN permite criar sistemas complexos em um chip (SoC), que podem incluir vários chips de diferentes empresas, fabricados usando diferentes processos tecnológicos.

Outra vantagem da tecnologia BSPDN é a capacidade de criar os chamados 3D-SoCs – chipsets nos quais os elementos lógicos são combinados com a memória. A tecnologia BSPDN também permite que você coloque uma camada condutora sob o silício e use a camada superior (FSPDN) para sinais de controle e energia.

De acordo com cálculos preliminares, os chips feitos com a nova tecnologia BSPDN terão desempenho 44% maior e consumirão 30% menos energia do que os atuais chips GAA de 3nm da Samsung.