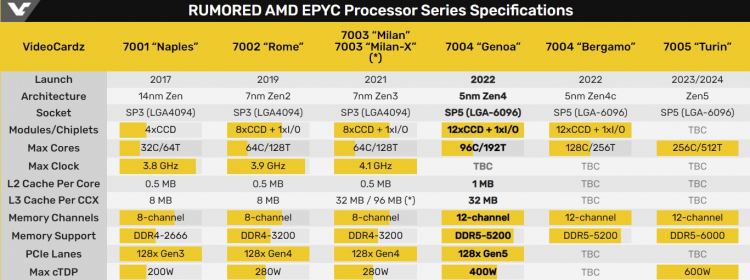

Um vazamento recente do banco de dados de teste sintético do Geekbench indica que os processadores de servidor Zen 4 da AMD receberão 1 MB de cache L2 por núcleo. Isso é confirmado por testes de uma amostra de engenharia de um dos processadores da série EPYC Genoa. Como os processadores de desktop AMD Ryzen são compostos dos mesmos chiplets que os chips de servidor EPYC, é provável que ter o dobro do cache L2 também seja verdade para os modelos Zen 4 Ryzen 7000.

Fonte da imagem: VideoCardz

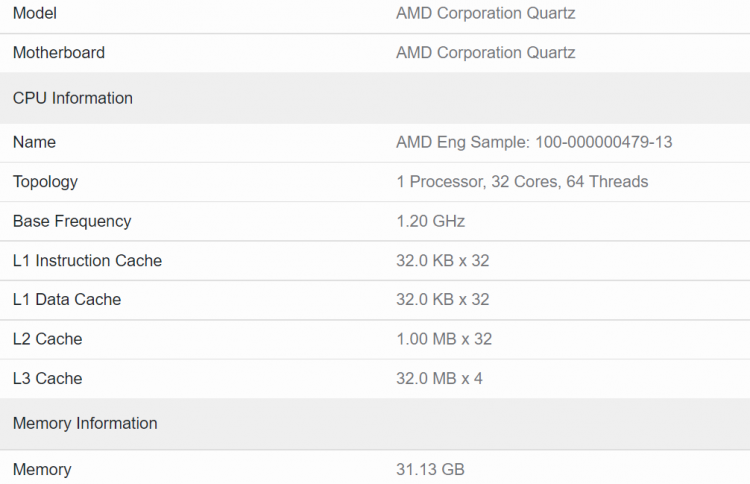

O chip da série Genoa acima com número OPN 100-000000479-13 possui 32 núcleos físicos integrados com suporte para 64 threads virtuais e opera com uma frequência base de 1,2 GHz. Considerando que esta é uma amostra de engenharia muito inicial, é seguro supor que a versão de mercado do processador terá uma frequência muito maior.

De acordo com o Geekbench, o chip testado tem um megabyte de cache L2 por núcleo, que é o dobro dos processadores EPYC das séries Nápoles, Roma e Milão. Ao mesmo tempo, a quantidade de cache L3 no novo chip não mudou em comparação com a mesma série de processadores Milan e é de 32 MB por chiplet (bloco CCX com oito núcleos). Mas como os processadores da série Genoa poderão oferecer até 96 núcleos físicos, a quantidade total de cache L3 será maior do que seus antecessores em qualquer caso. A única exceção serão os novos chips EPYC Milan-X com tecnologia 3D V-Cache, que triplica a quantidade de memória cache.

Recorde-se que os processadores EPYC 7004 (Genoa) serão fabricados segundo a tecnologia de processo de 5nm. Eles serão os primeiros processadores de servidor AMD a suportar RAM DDR5, bem como PCIe 5.0. Segundo a AMD, esses chips devem começar a ser vendidos este ano. Parceiros da empresa já estão recebendo amostras para testes.