Não é segredo que o desenvolvimento de novas tecnologias litográficas exige custos cada vez mais sérios dos fabricantes. Por esse motivo, o número de empresas dispostas a oferecer tecnologia de processo 7nm e outras mais finas está diminuindo. Cálculos aproximados mostram que agora a produção de um wafer de silício com produtos de 5nm custa à TSMC quase o dobro do que wafers com componentes de 7nm.

Fonte da imagem: TSMC

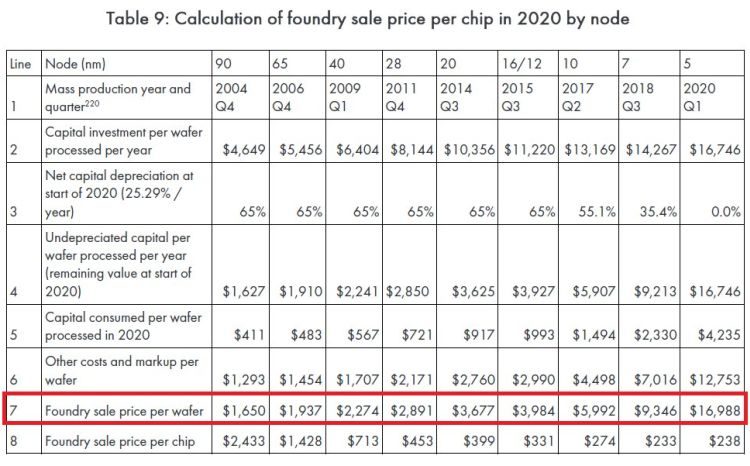

Um conhecido blogueiro da indústria de semicondutores com o pseudônimo Retired Engineer compartilhou os dados relevantes, para quem a atenção do público aos resultados dos cálculos foi uma surpresa. O autor dos cálculos partiu do pressuposto de que a TSMC é obrigada a produzir um processador gráfico NVIDIA P100 convencional com 90,7 bilhões de transistores de acordo com diferentes padrões litográficos, que, no âmbito da tecnologia de 5 nm, ocupa uma área de matriz de 610 mm2. Foi levado em consideração o tamanho padrão do wafer de silício – 300 mm, que é o mesmo para todos os processos técnicos.

Fonte da imagem: Twitter, engenheiro aposentado

De acordo com os resultados do cálculo, o preço de venda de um wafer de silício com chips de 5 nm não deve ser inferior a 6.988 para simplesmente recuperar todos os custos. Para efeito de comparação, um wafer de silício com chips de 7 nm agora pode ser vendido pela TSMC por 346. A diferença significativa no custo é explicada por vários fatores. Primeiro, a TSMC apenas começou a dominar a tecnologia de processo de 5 nm. Os equipamentos adquiridos e ferramentas especializadas ainda estão distribuindo parte dos custos fixos para um pequeno volume de produção, portanto o custo unitário por wafer de silício é bastante alto.

Em segundo lugar, a tecnologia de processo de 5 nm implica um uso mais ativo da litografia por radiação ultravioleta ultravioleta (EUV). Scanners litográficos para EUV ainda são um prazer caro, não há muitos deles comprados e, dentro da estrutura da tecnologia de 5 nm, a TSMC pode usar litografia EUV em 14 camadas de um chip semicondutor. Os custos iniciais são altos e, portanto, a produção de produtos de 5 nm ainda é um prazer caro.

Os dados fornecidos na tabela não pretendem ser confiáveis, uma vez que a própria TSMC nunca compartilhará tais informações, mas o autor dos cálculos garante que ele aderiu aos valores exatos sempre que possível. Curiosamente, mesmo levando em consideração os altos custos dentro da estrutura da tecnologia de 5 nm, o chip P100 convencional deve ser produzido apenas a um preço mais alto do que usar a tecnologia mais desenvolvida de 7 nm. Ao longo do caminho, melhorias no potencial de frequência e no consumo de energia podem ser alcançadas, de forma que nem tudo é determinado apenas pelas finanças. Se um chip com esses parâmetros tivesse que ser produzido usando tecnologia de 16 nm ou 12 nm, teria custado mais, 31 por cópia contra 38 quando usando tecnologia de 5 nm. Bem, à medida que o volume de produção de 5 nm aumenta, seu custo também diminui.