Juntamente com as extensões de arquitetura APX, a Intel apresentou hoje o novo conjunto de instruções AVX10 (Advanced Instruction Extensions 10). É um desenvolvimento adicional do AVX-512 e será suportado em promissores processadores híbridos não apenas por alto desempenho, mas também por núcleos energeticamente eficientes.

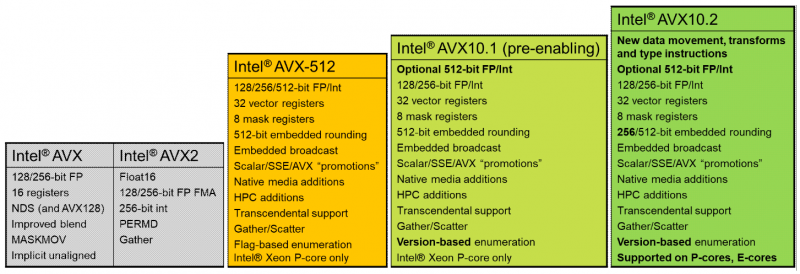

O principal objetivo da introdução do AVX10 é trazer instruções vetoriais que podem ser executadas por diferentes tipos de núcleos Intel sob um único padrão. O atual conjunto de instruções vetoriais AVX-512 permite que você trabalhe com operandos de 512 bits, mas é suportado por P-cores extremamente grandes. E-cores pequenos têm apenas registradores de 256 bits, então o AVX-512 não funcionará neles. Isso leva ao fato de que em processadores híbridos como Alder Lake ou Raptor Lake, o suporte AVX-512 deve ser desativado.

O kit AVX10 deve resolver esse problema, porém de forma um tanto peculiar. Registros com largura de 512 bits não aparecerão nos E-cores, mas permitirão executar as mesmas instruções vetoriais do AVX-512 definidas pelos núcleos P e E, mas em relação a registros de dimensões diferentes: no primeiro caso – 512 e no segundo – 256 bits. A Intel vai resolver o problema de compatibilidade dos resultados das operações adicionando o sinalizador de dimensão AVX512VL ao AVX10 e instruções especiais de 256 bits com arredondamento integrado.

A Intel afirma que todos os programas habilitados para AVX-512 existentes manterão o mesmo nível de desempenho quando executados em núcleos que suportam registros de 512 bits e instruções AVX10. No entanto, a recompilação para AVX10 de programas usando o conjunto AVX2 fornecerá um aumento de desempenho devido ao uso de instruções mais eficientes e 16 registradores adicionais. Além disso, o desempenho geral dos programas que usam AVX10, quando executados em processadores híbridos, será maior devido ao fato de que parte da carga pode ser redirecionada para E-cores.

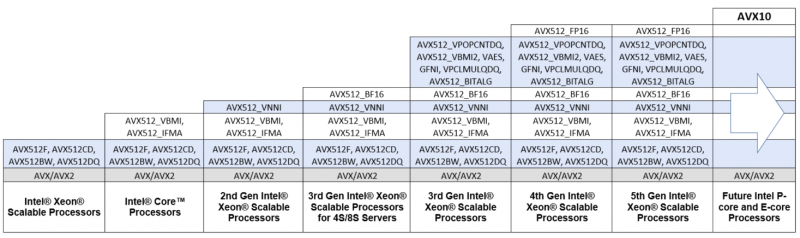

A primeira versão do AVX10, designada AVX10.1 na documentação da Intel, aparecerá nos processadores de servidor Granite Bay em 2024. No entanto, o trabalho com registros de 256 bits ainda não será implementado neles e a compatibilidade com AVX10 será fornecida apenas no nível P-core. Em outras palavras, estamos falando apenas do primeiro estágio de transição para a introdução de um novo conjunto. Uma implementação completa do AVX10 na forma de uma versão do AVX10.2, que funciona com registradores de 512 bits e 256 bits, está agendada para uma data posterior.

Com a transição para AVX10, o desenvolvimento adicional do AVX-512 é congelado e todas as chamadas para instruções 512 em processadores promissores ocorrerão por meio do AVX10. Quanto a outro conjunto de instruções promovido pela Intel, AMX (Advanced Matrix Extensions), ele permanecerá relevante mesmo após a transição para AVX10.