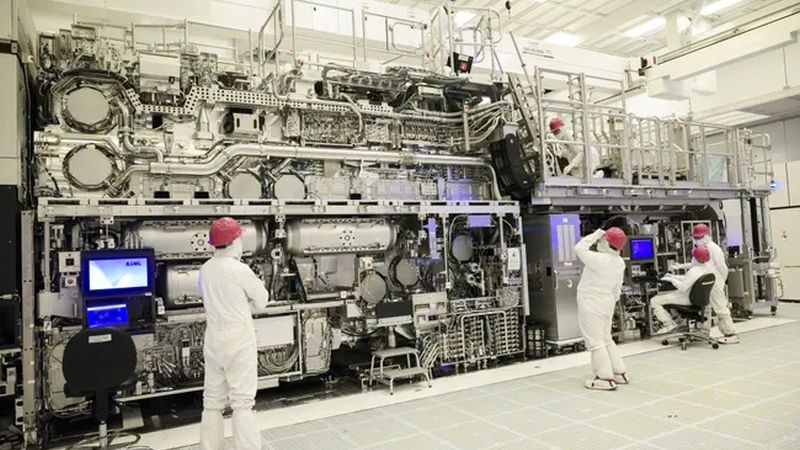

A empresa holandesa ASML realizou recentemente um teste de impressão em um wafer de silício usando seu scanner de litografia de alta abertura numérica (High-NA), e um experimento semelhante será repetido em breve pela Intel, que concluiu a instalação do primeiro Twinscan EXE:5000 sistema em seu centro de pesquisa em Oregon

Fonte da imagem: Intel

Lembramos que a ASML começou a enviar este avançado scanner litográfico desmontado para os EUA em dezembro, e só agora a Intel recebeu todos os componentes necessários e concluiu a instalação do equipamento. A configuração levará mais algum tempo, após o qual a Intel também poderá testar linhas condutoras de impressão na superfície do wafer de silício. Espera-se que a nova classe de equipamentos permita a impressão de elementos 1,7 vezes mais compactos em um wafer de silício, e a densidade de impressão por passagem alcançada aumente 2,9 vezes em comparação aos scanners EUV convencionais. Lembremos que o ASML, em sua cópia de um sistema semelhante, foi capaz de imprimir linhas com densidade de posicionamento de 10 nm. A combinação de uma fonte de luz de 13,5 nm e óptica de alta abertura numérica permite teoricamente que a Intel crie recursos tão pequenos quanto 8 nm.

O novo scanner Twinscan EXE:5000 será usado pela Intel para experimentos usando a tecnologia de processo Intel 18A, mas não será usado na produção em massa até a transição para a tecnologia de processo Intel 14A em 2026 ou mais tarde, e para processar apenas algumas camadas de chips, pois isso é determinado pela viabilidade econômica. A Intel planeja usar equipamentos ASML com alta abertura numérica na produção de chips para pelo menos três gerações de processos tecnológicos.

Um scanner Twinscan EXE:5000 é capaz de processar 185 wafers de silício por hora e, no futuro, a Intel espera receber um scanner Twinscan EXE:5200B da ASML, que pode processar mais de 200 wafers de silício por hora. O desempenho de tais equipamentos na prática, como explica Tom’s Hardware, será limitado pela área de projeção reduzida fornecida por um scanner de alto NA. Isto limita simultaneamente o tamanho do chip de cristal que pode ser obtido em uma passagem. A Intel vai compensar isso em software devido à capacidade de “colar” a projeção de um cristal de duas partes, e o ASML aumenta simultaneamente a velocidade de movimento das plataformas nas quais os wafers de silício e o equipamento de projeção são montados, respectivamente.

Em qualquer caso, a um custo de cerca de 400 milhões de dólares cada, o equipamento de litografia com alto NA não pode ser produzido em massa, embora a ASML já tenha encomendas de 10 ou 20 desses sistemas, e recentemente tenha começado a enviar um deles para um segundo cliente, que pode acabou por ser o belga Imec. A Intel acredita que a introdução da chamada tecnologia High-NA EUV se justifica dada a necessidade de desenvolver estruturas de transistores mais avançadas. Entre eles estão chips com alimentação pelo verso do wafer de silício, transistores CFET empilháveis verticalmente e estruturas “automontadas” em nível molecular. A Intel vai dedicar o próximo ano à preparação de equipamentos EUV de alto NA para produção em massa de chips usando a tecnologia Intel 14A. Como parte da tecnologia Intel 18A, será utilizado apenas em condições de laboratório, mas não na linha de produção principal.