De acordo com fontes taiwanesas, a TSMC iniciou uma produção piloto de chips de 3 nm. O lançamento em massa de soluções para pedidos da Apple, AMD, Qualcomm e outros está planejado em cerca de um ano – no quarto trimestre de 2022. E tudo ficaria bem, mas o problema do atraso dos processos técnicos para empacotar soluções multichip complexas veio à tona e, sem isso, o progresso real será atrasado.

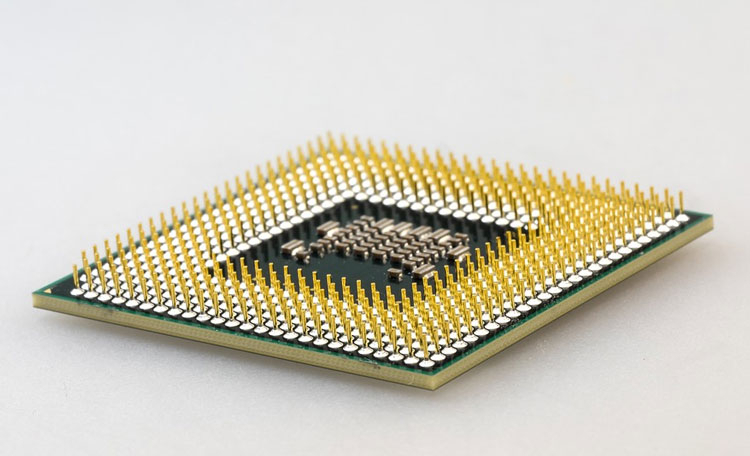

Fonte da imagem: Pixabay

Não é segredo que o futuro das soluções de semicondutores mais avançadas reside na criação de estruturas heterogêneas em massa. Os cristais em um chip composto serão dispostos horizontal e verticalmente. Neste caso, o número de conexões interchip aumentará continuamente e isso afetará o diâmetro ou a área dos contatos. O passo do contato terá que ser reduzido ou os cavacos começarão a aumentar rapidamente de tamanho. Mas, como a TSMC admitiu, a empresa está tendo dificuldade em dimensionar interconexões abaixo de 2 mícrons.

Acontece que a TSMC lida com sucesso com a produção de cristais usando os processos tecnológicos mais avançados, mas empacotar vários cristais em um bloco comum (caixa) usando intermediários e substratos começa a ficar para trás. De acordo com os objetivos da empresa, a cada nova geração de chips, o pitch de contato deve ser reduzido em 70%. No que se refere ao processo técnico de 3 nm, esta condição, a julgar pelas declarações, não é atendida. Qual é a ameaça? No mínimo, a produção ficará mais cara até que a TSMC ou seus subcontratados de embalagem de chips superem os obstáculos.