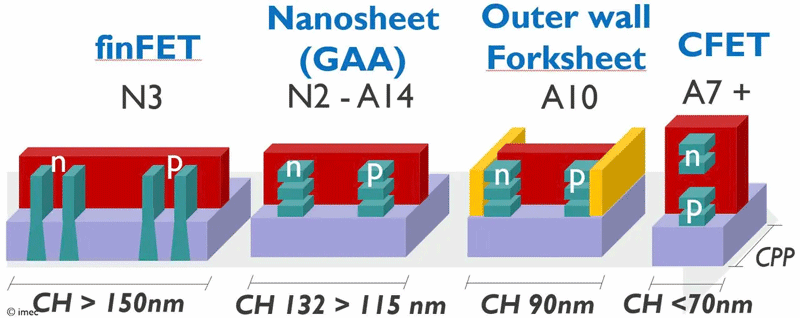

Há cerca de seis anos, o centro belga Imec apresentou uma arquitetura de transistor completamente nova – CFET (FET complementar). O objetivo era auxiliar na produção de transistores com padrões de produção inferiores a 2 nm. A peculiaridade da arquitetura eram os canais nanopage separados (forksheet). Mas a tecnologia se mostrou difícil de fabricar, então o Imec criou uma versão intermediária modificada da futura arquitetura, apresentada recentemente.

Fonte da imagem: Imec

A essência da arquitetura forksheet é separar os transistores dos tipos n e p com uma partição dielétrica com uma porta circular comum (GAA). A partição ou parede é projetada para minimizar a influência dos transistores vizinhos uns sobre os outros. Nesse caso, um par de transistores com condutividade diferente pode ser fabricado em uma área menor do chip, o que, como resultado, levará a uma redução significativa na área do cristal – até 20%. Além disso, o Imec propôs dispor os transistores uns sobre os outros para implementar a arquitetura CFET, o que reduziria ainda mais a área do chip. No entanto, trabalhos subsequentes com transistores com páginas separadas mostraram que a ideia com uma partição dielétrica é extremamente difícil de implementar em produção.

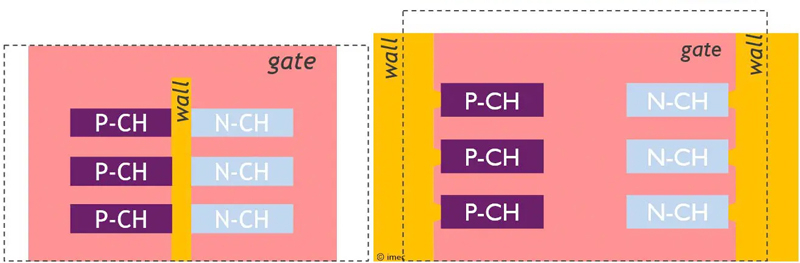

A partição dielétrica mais fina, com espessura de 8 a 10 nm, teve que ser fabricada primeiro, antes de todas as manipulações com o cristal e a gravação dos transistores. Nem todo material suporta tal “tortura”, que levaria a um alto nível de defeitos. Então, a Imec encontrou uma solução brilhante: as partições deveriam ser externas. Elas não separavam mais transistores de polaridade diferente uns dos outros, mas, de certa forma, isolavam pares de transistores de pares vizinhos. Na verdade, isso era o isolamento de transistores com a mesma condutividade.

Opções de partição dielétrica interna e externa

Com essa tecnologia de processo, as divisórias estavam entre as últimas a serem fabricadas no cristal. Essa solução permitiu o uso de materiais conhecidos. Devido às paredes mais espessas, a área de posicionamento dos pares de transistores poderia sofrer um pouco, mas todos os outros benefícios, como aumento da velocidade de operação (correntes) e redução de vazamentos, foram preservados. Uma transição mais fina entre as nanopáginas e a parede externa permitiu que a porta cobrisse uma área maior da borda de cada canal das nanopáginas, o que melhorou significativamente o controle sobre as correntes nos canais dos transistores.

Por fim, a fabricação final das paredes externas ao redor dos canais do transistor aumentou o estresse mecânico nas nanofolhas (nos canais do transistor). O termo “silício deformado” é familiar para qualquer pessoa que esteja no ramo de fabricação de chips há pelo menos um quarto de século. Sob tais condições, a condutividade dos elétrons e lacunas no semicondutor aumenta, o que leva a um aumento no desempenho geral dos chips.

Os desenvolvedores admitem que, ao aumentar a espessura das divisórias isolantes externas dos transistores de forquilha para 15 nm, a área total do chip pode ser um pouco maior do que no caso do uso de divisórias internas, mas este é um sacrifício pequeno e necessário. A modelagem CAD de células SRAM e geradores usando transistores com nanopáginas separadas e divisórias externas mostrou que, em células de memória estáticas, o novo esquema para a tecnologia de processo A10 (10 angstroms) permitiu reduzir a área em 22% em comparação com as nanofolhas A14 sem isolamento devido ao empacotamento mais denso de dispositivos semelhantes e à redução do passo da porta.

No projeto do oscilador de carga total, o novo layout iguala ou supera o desempenho dos osciladores A14 e 2 nm. Em vazio, a corrente de alimentação é reduzida em aproximadamente 33% (redução de vazamento).

A experiência com transistores com nanofolhas separadas será importante para o desenvolvimento de CFETs, visto que muitas das etapas do processo, materiais e conceitos de projeto se sobrepõem. Nos transistores de folha de garfo, os dispositivos tipo p e tipo n são dispostos lado a lado. Em contraste, os CFETs de próxima geração disporão dois tipos diferentes de transistores verticalmente, embora as tecnologias subjacentes permaneçam as mesmas. Mas essa é uma história de meados da década de 1930 à qual retornaremos muitas vezes no futuro.