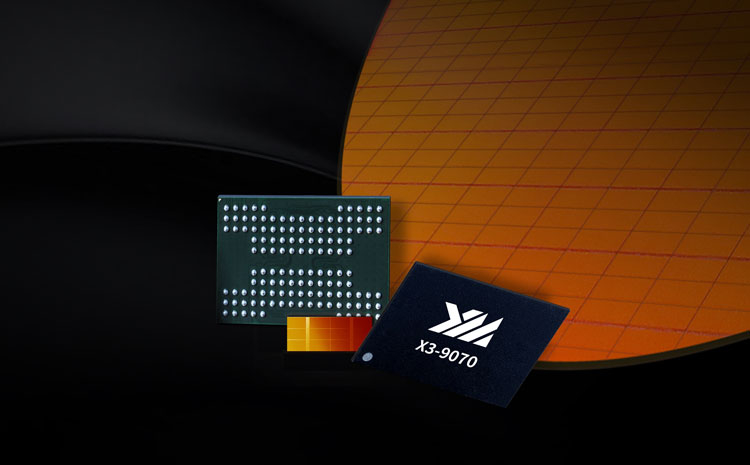

Hoje, no Flash Memory Summit (FMS) 2022, a YMTC da China apresentou a memória flash X3-9070 3D NAND baseada na inovadora arquitetura Xtacking 3.0. Os novos chips 3D NAND chineses poderão fornecer maior velocidade e eficiência.

Fonte da imagem: YMTC

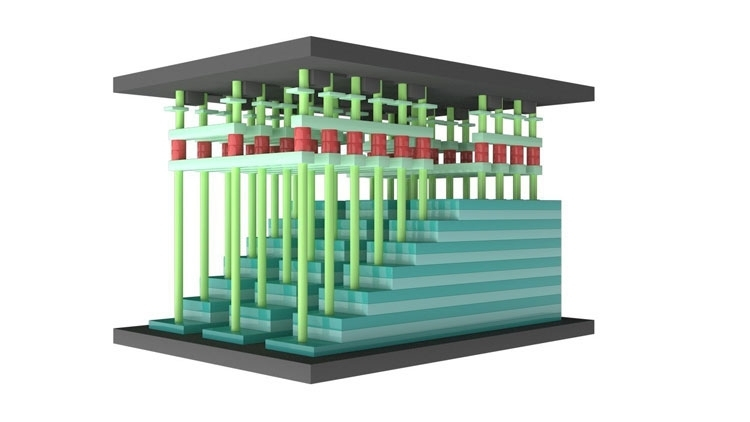

A arquitetura Xtacking foi introduzida em 2018 e desde então evoluiu para a terceira geração. Ele assume que uma matriz de células de memória 3D NAND está localizada em um chip separado e os circuitos de energia e controle são colocados no outro. Arrays e controladores podem ser produzidos usando diferentes processos técnicos, já que o primeiro e o segundo são feitos em diferentes pastilhas de silício. Subsequentemente, o chip de controle é combinado com matrizes de células de memória e a saída é um chip de memória NAND 3D completo.

A produção separada de células e controladores permite economizar espaço no plano de cristais de memória (produzir mais células a partir de cada placa), além de atualizar células ou controladores sem estar vinculado à produção de um e de outro. No momento, o segundo cenário está sendo implementado, quando a YMTC se prepara para lançar um NAND 3D mais produtivo sem alterar a tecnologia para a produção de arrays de memória.

Como estamos falando de melhorar a lógica e a potência, o desenvolvedor não dedicou uma única linha para atingir este ou aquele recorde na produção de múltiplas camadas NAND 3D, como fizeram, por exemplo, Micron e SK hynix, que anunciaram o lançamento de 232 – e 238-, respectivamente, memória NAND 3D em camadas. Em vez disso, a YMTC informou que o desempenho dos novos chips habilitados para Xtacking 3.0 atinge velocidades de E/S de até 2400 MT/s por pino. Ele também afirma ser compatível com a interface ONFI 5.0 e alcançar um desempenho 50% melhor do que a geração anterior de produtos.

Um exemplo de combinação de um controlador Xtacking (matriz superior) e um array de memória (matriz inferior). Fonte da imagem: YMTC

Além disso, o X3-9070 é o produto flash de maior densidade da história do YMTC, oferecendo 1 Tbps de capacidade de armazenamento em um monobloco ultracompacto. O novo controlador agora suporta organização de células flash de 6 planos, enquanto a organização de 4 planos era suportada anteriormente. O suporte para 6 regiões de células para processamento independente permite expandir operações paralelas e aumentar o desempenho da memória. Em particular, a produtividade promete crescer até 50% enquanto reduz o consumo em até 25%.

Além disso, a empresa não especifica quando a nova arquitetura aparecerá em seus produtos.