O Semiconductor Products Standards Committee (JEDEC) lançou a especificação DDR5 (JESD79) em 2020, definindo parâmetros de módulo até velocidades DDR5-6400. O comitê introduziu agora uma especificação atualizada, JESD79-JC5, que especifica módulos até DDR5-8800, aumenta a largura de banda de memória de pico em 37,5% e adiciona alguns novos recursos de segurança projetados para combater ataques RowHammer.

Fonte da imagem: unsplash.com

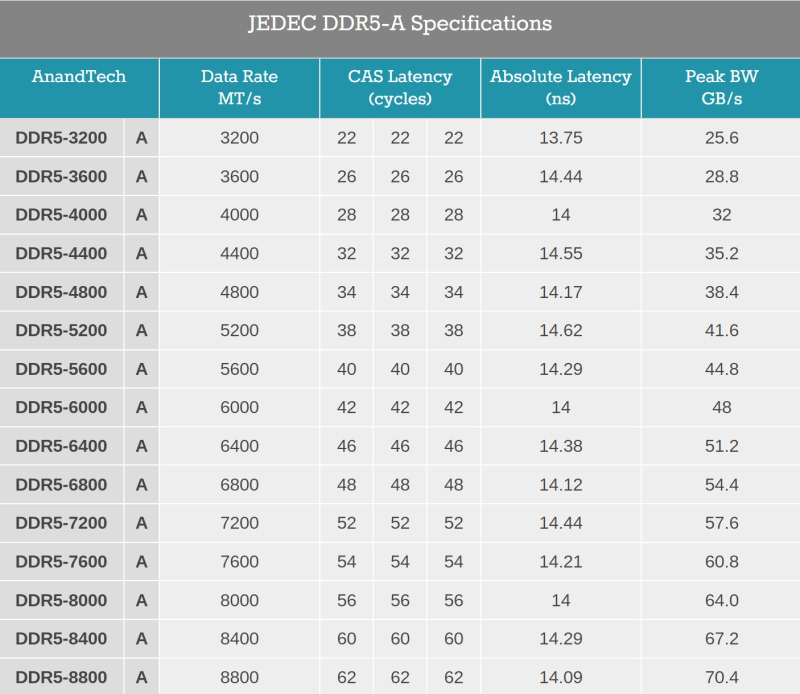

O lançamento da nova especificação significa que todos os membros do comitê JESD79, que define as especificações para DDR5, incluindo fabricantes de chips de memória e desenvolvedores de controladores de memória, confirmam que DDR5-8800 é uma extensão viável para a especificação DDR5, tanto em termos de desempenho e custo. Juntos, um novo recurso, Self-Refresh Exit Clock Sync, foi adicionado ao padrão para otimizar o treinamento da memória. A tabela de especificações oficiais JEDEC para módulos DDR5 é apresentada abaixo.

Fonte da imagem: anandtech.com

A especificação atualizada faz várias alterações destinadas a combater explorações do tipo RowHammer. Durante tal ataque, certas células de memória ficam tão sobrecarregadas com solicitações que as correntes de fuga causadas por essas operações alteram as cargas em células próximas fisicamente localizadas, o que possibilita o acesso a áreas protegidas da memória sem acessá-las diretamente. Usando a vulnerabilidade RowHammer, você pode, por exemplo, roubar chaves RSA de 2.048 bits de uma área protegida.

O recurso Per-Row Activation Counting (PRAC) permite que o DDR5 controle a frequência com que acessa a mesma linha. Quando um determinado limite é excedido, as células nas linhas adjacentes são sobrescritas caso um bit não esteja corrompido em uma das células. Vale ressaltar que o comunicado de imprensa da JEDEC nunca usa o nome RowHammer, embora esta vulnerabilidade seja claramente discutida.

Os especialistas acreditam que o recurso PRAC é baseado na recente patente da Intel, “Perfect RowHammer Tracking with Multiple Count Steps” (US20220121398A1), que descreve um mecanismo semelhante chamado PRHT (Perfect Row Hammer Tracking). A Intel indica que esse método causa uma penalidade no desempenho porque aumenta o tempo geral de atualização da linha.

A especificação DDR5 atualizada também remove o requisito de suporte a Partial Array Self Refresh (PASR) devido a possíveis problemas de segurança. O recurso PASR visa principalmente melhorar a eficiência energética da memória para dispositivos móveis e, como uma tecnologia relacionada à atualização, facilita potencialmente os ataques RowHammer. Mas à medida que os dispositivos móveis utilizam cada vez mais tecnologias LPDDR otimizadas e de baixo consumo de energia, a remoção do suporte PASR não parece ser um grande problema para os consumidores.