O empilhamento de células de RAM poderia aumentar significativamente a densidade de armazenamento de dados e resolver a escassez de RAM. A memória HBM foi o primeiro passo nessa direção, mas provou ser cara e não universalmente aceita. Um avanço significativo só seria possível se a DRAM seguisse o caminho da produção de memória flash 3D NAND. Embora isso ainda não tenha acontecido, o primeiro protótipo de tal solução já foi implementado em silício e atraiu a atenção de investidores de renome.

Fonte da imagem: NEO Semiconductor

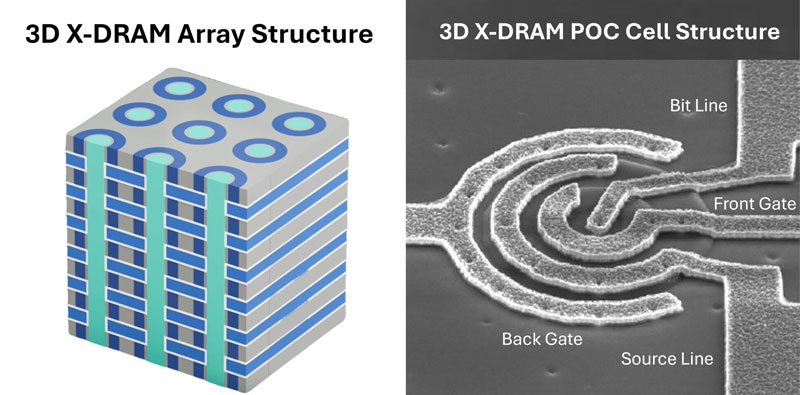

A NEO Semiconductor, uma jovem empresa americana, anunciou a criação de um protótipo de 3D X-DRAM como parte de uma prova de conceito. Há um ano, a empresa buscou, sem sucesso, apoio de fabricantes de memória, mas hoje está repleta de investidores e clientes. A administração da empresa afirma que negociações intensivas estão em andamento com vários fabricantes líderes de memória, o que acelerará o desenvolvimento de RAM empilhada.

Um marco significativo para a NEO Semiconductor foi a aquisição de Stan Shih, um investidor lendário na indústria eletrônica. Ele tem 81 anos, fundou a Acer e liderou a TSMC por quase 20 anos. Também foi significativa a colaboração com instituições de ensino superior de Taiwan, a Universidade Nacional Yangming Chiao Tung (NYCU) e sua subsidiária, a Escola de Inovação Indústria-Academia (IAIS). O protótipo também foi fabricado em Taiwan, no Instituto Nacional de Pesquisa Aplicada – Instituto de Pesquisa de Semicondutores de Taiwan (NIAR-TSRI).

Os testes e a caracterização da amostra provavelmente também foram realizados no NIAR-TSRI. A empresa relata que a latência de leitura/gravação foi inferior a 10 ns, o tempo de atualização a 85 °C foi superior a 1 segundo (15 vezes melhor que o padrão JEDEC de 64 ms) e a tolerância ao desgaste atingiu 10¹⁴. A imunidade a ruídos também foi alta.“Fico satisfeito que a estreita parceria entre a indústria e a academia nos tenha permitido validar a viabilidade do conceito de DRAM 3D da NEO em um ambiente real de fabricação de silício”, disse Jack Sun, pesquisador sênior.Vice-presidente da Universidade de Nova York e reitor do Instituto de Pesquisa Aplicada em Ciência e Tecnologia, e ex-diretor de tecnologia da TSMC. “Esta prova de conceito bem-sucedida não apenas demonstra o potencial de arquiteturas de memória inovadoras, mas também valida a viabilidade de implementar tecnologias de memória avançadas usando processos comprovados.”

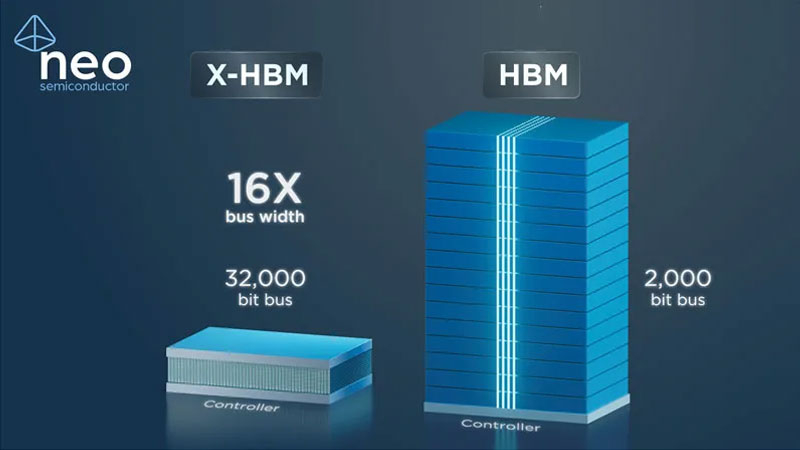

Segundo os desenvolvedores da NEO Semiconductor, o layout DRAM empilhado e o barramento de dados extremamente amplo — aproximadamente 32.000 bits — permitirão a criação de RAM com uma densidade de gravação de 512 Gbit por chip e uma largura de banda 16 vezes maior que a da memória HBM atual. O desenvolvimento do padrão HBM não prevê nada semelhante antes de meados deste século, enquanto a NEO Semiconductor está pronta para lançar uma RAM com essas características em um futuro próximo.