A arquitetura RISC-V é bastante jovem e geralmente é associada a chips econômicos em placas como o Raspberry Pi. No entanto, tecnicamente, também permite criar processadores poderosos que podem competir com as melhores soluções baseadas nas arquiteturas Arm e x86. Na cúpula RISC-V, a Ventana Micro Systems anunciou toda uma família de processadores de alto desempenho, o primeiro dos quais foi o chip Veyron V1, que, segundo os desenvolvedores, poderá competir em desempenho de thread único com o mais recente CPUs de ponta.

O Veyron V1 deve ser o processador mais rápido com arquitetura RISC-V. Fonte: Twitter@risc_v

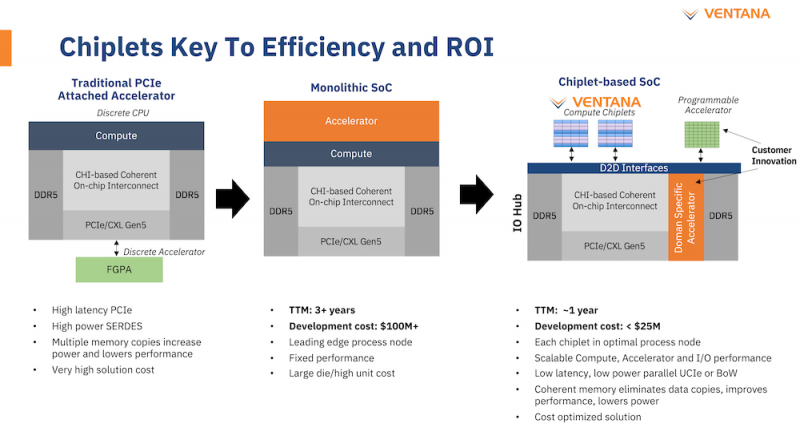

A novidade é voltada para o mercado de hiperescaladores e, graças ao design do chiplet, o novo processador foi originalmente desenvolvido como personalizável para as tarefas do cliente. O Veyron V1 será oferecido na forma de uma espécie de kit-construtor, que inclui um ou mais chiplets de computação Veyron, um hub de E/S e uma interconexão que permite conectar todos os componentes juntos. Isso, de acordo com os desenvolvedores, deve acelerar e reduzir seriamente o custo de introdução de uma nova plataforma de processador, reduzindo os custos de desenvolvimento de chips em 75% e o tempo de criação para não mais que dois anos.

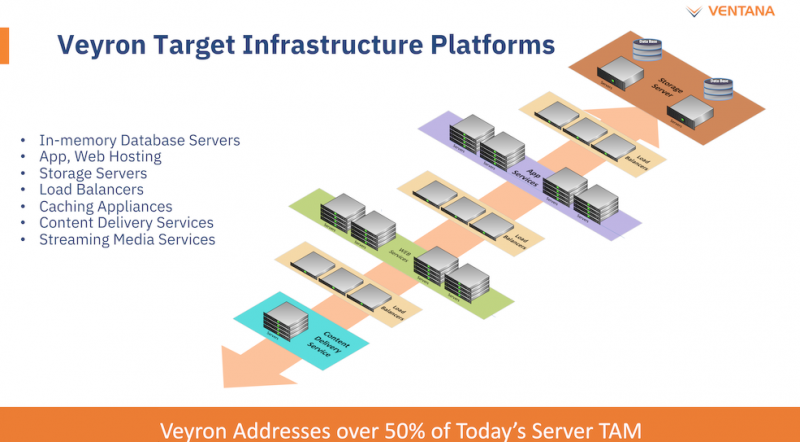

A plataforma Veyron V1 é versátil e abrange uma ampla gama de aplicações. Fonte aqui e abaixo: StorageReview

O chiplet de computação Veyron V1 usa núcleos RISC-V avançados de 64 bits e possui 2 MB de cache L2, bem como um controlador de memória multithread. As configurações de chiplet estão disponíveis com 6, 8, 12 ou 16 núcleos a cerca de 3 GHz, o que é comparável às soluções do Google e da AWS. O processador pode ser usado não apenas no data center, mas também em vários sistemas embarcados, estações base 5G ou até estações de trabalho de clientes.

A arquitetura do chip acelerará o ciclo de desenvolvimento e implementação, além de simplificar a tarefa de conectar aceleradores personalizados

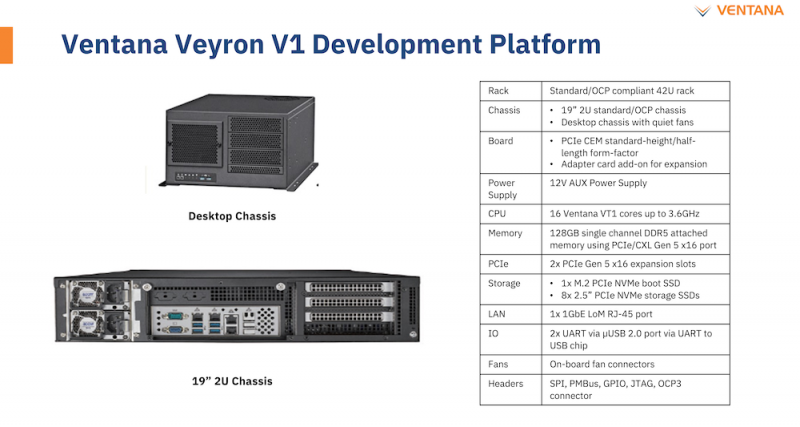

O projeto arquitetônico do Veyron V1 usa um pipeline agressivo de oito estágios fora de ordem. O chip é capaz de operar em até 3,6 GHz usando a tecnologia de processo de 5 nm da TSMC. O hub de E/S pode ser feito usando processos mais baratos de 12 nm ou mesmo de 16 nm. Uma interconexão D2D especial de baixa latência foi desenvolvida para conectar os componentes do processador.

Plataforma de desenvolvimento Veyron V1 e especificações

Cada chiplet inclui até 16 núcleos e o processador pode ser dimensionado para até 192 núcleos em 12 chiplets. O cache L3 compartilhado total é de 48 MB. É declarado um alto nível de proteção da arquitetura contra ataques por canais de terceiros. Os desenvolvedores afirmam baixo consumo de energia sem precedentes: 128 núcleos V1 cabem em 280 W; O AMD EPYC 7763 consome a mesma quantidade com metade do número de núcleos.

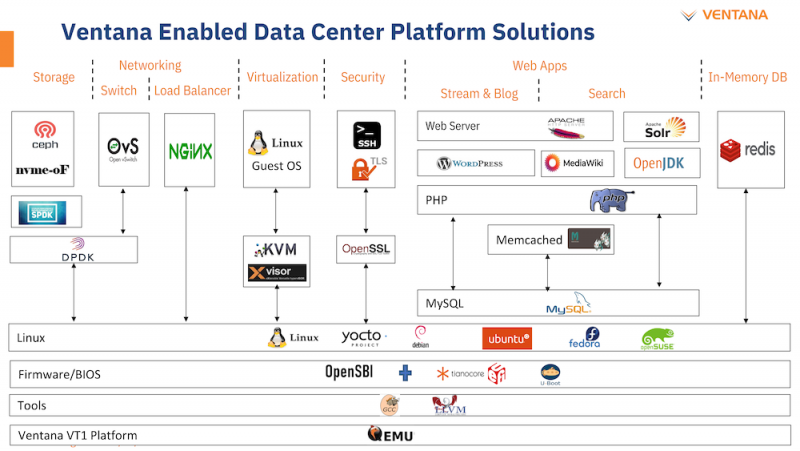

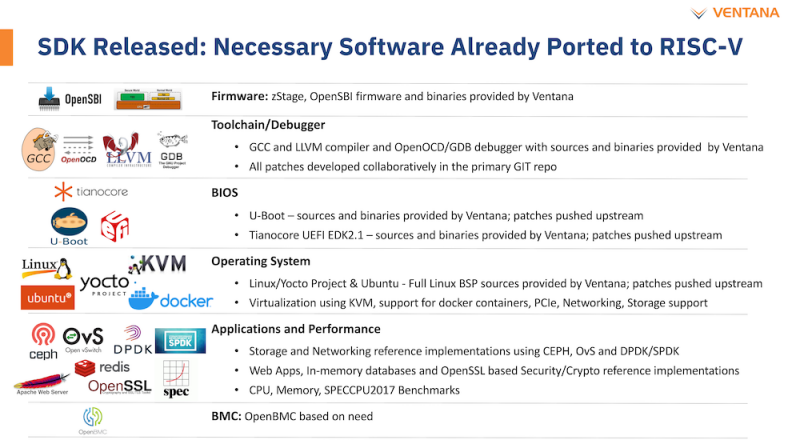

A Ventana oferecerá suporte à nova plataforma em todos os níveis de desenvolvimento de software de sistema e aplicativo

A maior parte do software crítico já foi portada para a arquitetura RISC-V

A empresa também não se esqueceu do suporte de software: as plataformas de desenvolvedor Ventana Veyron V1 serão acompanhadas por um SDK completo com o software principal já portado para a nova arquitetura. A lista inclui os compiladores GCC e LLVM, o depurador OpenOCD/GDB, fontes e binários do carregador U-Boot e Tianocore UEFI EDK2.1. Várias distribuições do Linux são suportadas, bem como outros softwares de sistema e aplicativos. Espera-se que os novos sistemas estejam disponíveis no início do próximo ano.