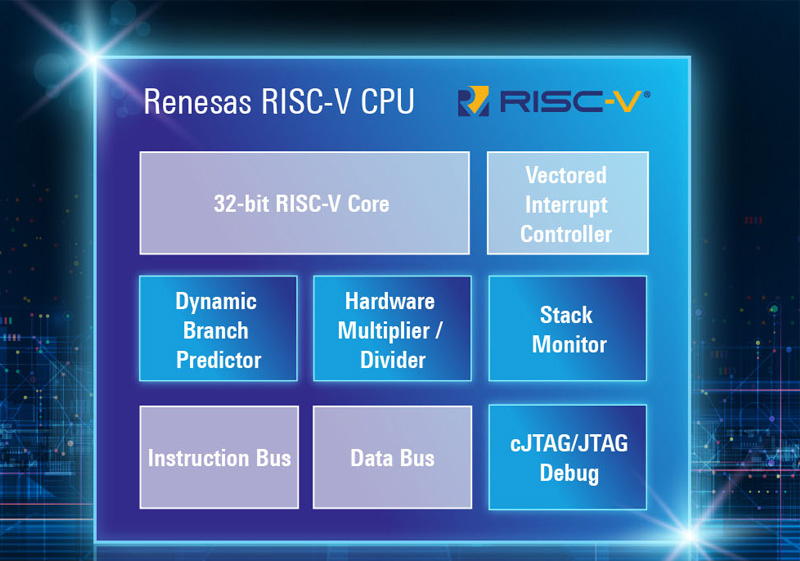

A Renesas Electronics anunciou a criação de seu próprio núcleo de processador de 32 bits baseado na arquitetura de conjunto de instruções (ISA) RISC-V de código aberto. A solução complementará a família existente de unidades microcontroladoras (MCUs) de 32 bits da Renesas, incluindo produtos proprietários RX e RA baseados na arquitetura Arm Cortex-M.

O núcleo RISC-V da Renesas foi projetado para criar chips de uso geral. Espera-se que tais processadores encontrem aplicação em dispositivos da Internet das Coisas, eletrônicos de consumo, equipamentos médicos, sistemas industriais, etc.

Fonte da imagem: Renesas

O novo núcleo pode servir como controlador de aplicativo primário ou como nó secundário opcional no SoC. Além disso, o núcleo é adequado para uso em subsistemas on-chip e produtos específicos de aplicação (ASSP). O desempenho é avaliado em 3,27 CoreMark/MHz, que a Renesas afirma ser superior a outras soluções comparáveis no mercado.

O núcleo Renesas implementa várias extensões RISC-V ISA: M (multiplicação/divisão de inteiros), A (operações de memória atômica), C (formato de instrução compactado; um subconjunto de RV32I) e B (instruções de manipulação de bits). A Renesas planeja lançar seu primeiro MCU baseado em RISC-V e ferramentas de desenvolvimento relacionadas no primeiro trimestre de 2024. Detalhes técnicos sobre o produto serão anunciados naquele momento.