O fato de que os próximos processadores para servidor Intel Xeon Sapphire Rapids também receberão suporte para memória HBM, além do controlador DDR5, não é mais um segredo. As alterações correspondentes na documentação para desenvolvedores foram publicadas no final do ano passado.

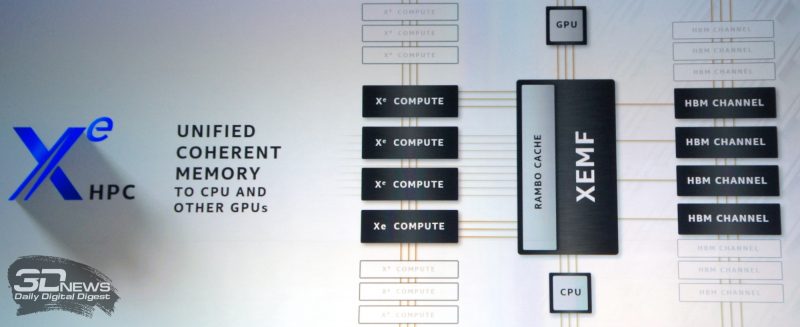

Esses processadores funcionarão em conjunto com aceleradores Intel Xe HPC (Ponte Vecchio), e haverá um barramento XEMF separado (XE Memory Fabric) com suporte de coerência para combinar blocos de acelerador, memória HBM e CPU. A AMD também aproveitará a coerência do barramento Infinity Fabric para conectar EPYC e Radeon Instinct. Em ambos os casos, estamos falando de sistemas de supercomputadores.

E, presumivelmente, os processadores Xeon Sapphire Rapids com memória HBM integrada serão preparados para esses sistemas. Isso é indicado diretamente pelos últimos patches da Intel para o kernel do Linux, para os quais o recurso Phoronix chamou a atenção. Os patches estão relacionados ao driver EDAC (Error Detection And Correction). Eles também mencionam o processador de rede neural SoC Ice Lake para inferência de aprendizado profundo (ICL-NNPI) – Intel Nervana NNP-I (Spring Hill).