O problema da organização eficiente de sistemas de computação multicore e multinó é conhecido há muito tempo. Mesmo interconexões e barramentos especialmente projetados como o InfiniBand nem sempre funcionam bem o suficiente. O consórcio CXL vê a solução para o problema no desenvolvimento de um padrão com o mesmo nome, Compute Express Link, que usa PCI Express como base. Sua primeira versão foi lançada em março de 2019, e todo esse tempo ela vem se desenvolvendo ativamente. As especificações do CXL versão 2.0 foram publicadas oficialmente.

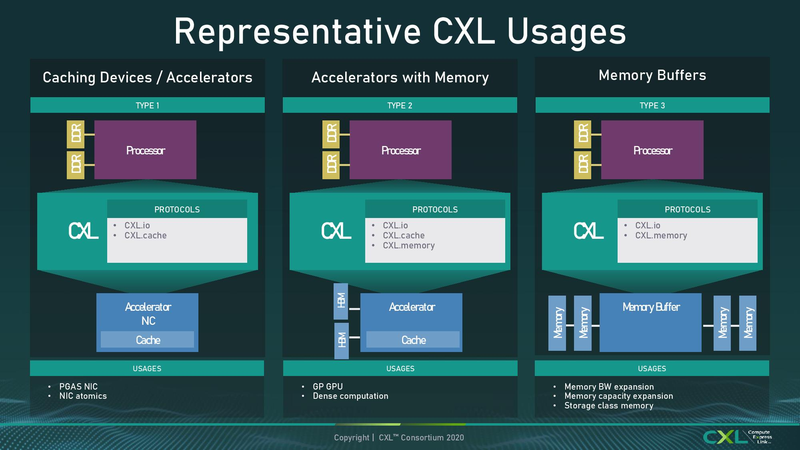

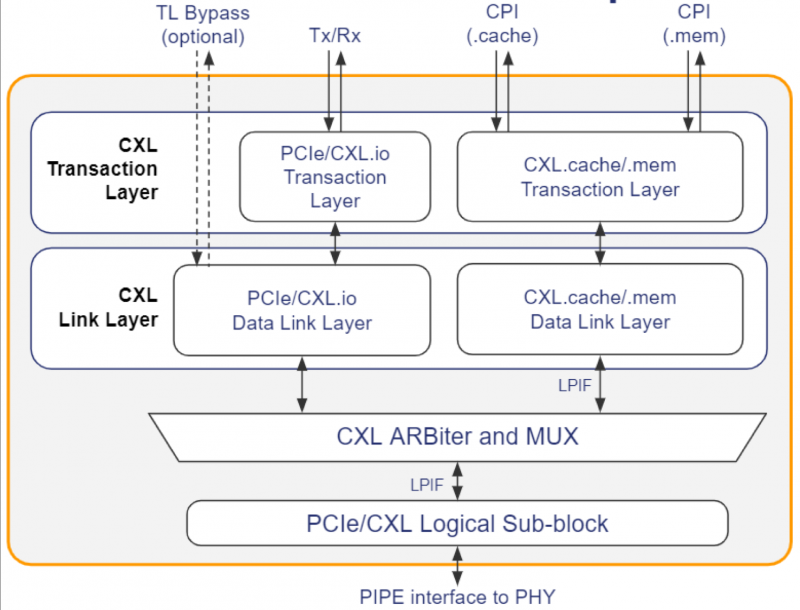

Inicialmente, o PCI Express é um sistema bastante simples, geralmente fornecendo uma conexão ponto a ponto entre um dispositivo host e um cliente. Mas para sistemas de computação multisite complexos, tais recursos claramente não são suficientes, e o CXL implementa vários protocolos de comunicação, otimizados para três tipos de tarefas: entrada-saída (IO), cache (Cache) e acesso à memória (Memória).

Em vez disso, essa especialização tripla foi descrita em versões anteriores do padrão CXL, mas na versão 2.0 o padrão foi significativamente aprimorado. O CXL 2.0 ainda é baseado no PCI Express 5.0 e não há mudanças na velocidade e latência, mas o protocolo recebeu suporte para comutação e criptografia. Agora também pode funcionar com dispositivos de memória persistente, como memória 3D XPoint.

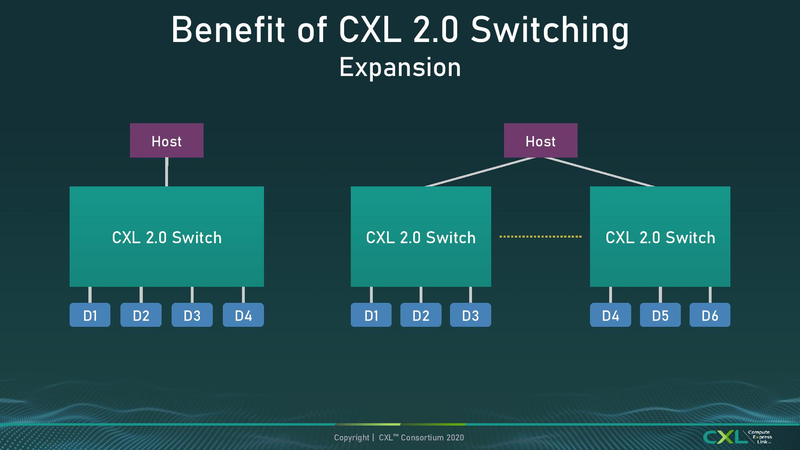

Os switches são uma parte importante do ecossistema PCI Express, tais chips permitem expandir artificialmente o número de linhas de barramento disponíveis. Claro, o limitador de largura de banda ainda é o canal “upstream”, mas, por exemplo, os aceleradores em tal sistema, graças ao switch, podem se comunicar uns com os outros, ignorando a unidade principal.

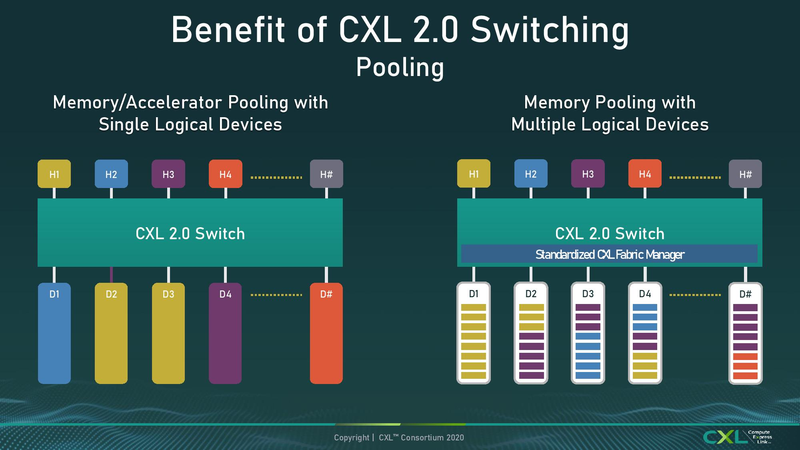

O CXL 2.0 tem suporte total para comutação, incluindo a capacidade de expandir o sistema conectando switches adicionais, os dispositivos cliente e host podem funcionar no modo 1: 1 e com vários hosts ao mesmo tempo, até 16. Ao mesmo tempo, ferramentas de qualidade de serviço são suportadas (QoS). Até agora, apenas um modelo de chaveamento plano foi implementado, no entanto, os planos dos desenvolvedores do CXL incluem a introdução de um modelo de vários níveis.

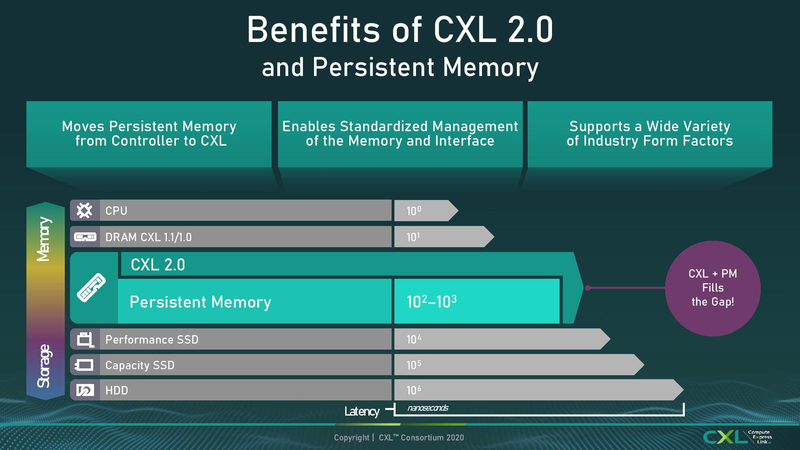

Nos últimos anos, os dispositivos de memória persistente (PMEM) cresceram em popularidade à medida que a memória não volátil se tornou verdadeiramente popular e, além disso, surgiram soluções como a memória persistente Intel Optane DC que não são muito inferiores em desempenho à DRAM clássica, mas ao mesmo tempo com todos os benefícios do NAND.

O suporte para dispositivos PMEM tornou-se parte integrante do CXL 2.0, e agora os recursos desse tipo podem ser agrupados, disponíveis na lógica CXL.memory. Esses pools nos complexos CXL ocuparão um lugar intermediário entre os pools DRAM e os arrays SSD, o acesso a eles é totalmente padronizado e não depende do fabricante do dispositivo final.

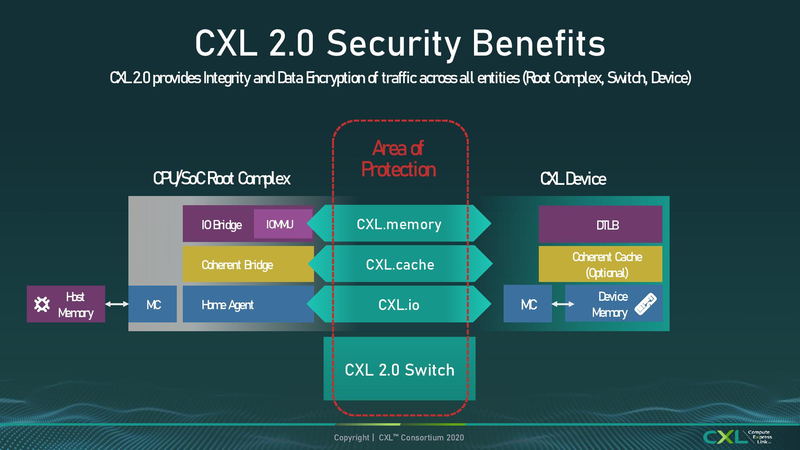

As primeiras versões do CXL não suportavam nenhum padrão de criptografia único, o que significava que esse sistema de interconexão não era realmente seguro. Na versão 2.0, esse suporte apareceu. É opcional, mas agora qualquer canal de transmissão de dados dentro do complexo CXL pode ser criptografado por meio dos aceleradores de criptografia integrados aos controladores CXL 2.0.

O uso de criptografia pode afetar as taxas de latência, mas a quantidade dessa penalidade depende do caso de uso específico e dos recursos dos controladores CXL. Você pode desativar o suporte à criptografia CXL 2.0 se quiser minimizar a latência.

As inovações introduzidas no CXL 2.0 estão alinhadas com as tendências atuais no mundo da computação de alto desempenho. Em particular, a implementação de suporte para comutação CXL indica que os desenvolvedores do padrão estão muito familiarizados com o conceito de desagregação de recursos de servidor. Quanto ao modelo físico, não estão planejados desvios do PCI Express 5.0. Todos os dispositivos habilitados para CXL serão capazes de trabalhar no modo PCIe “puro”, embora talvez com a perda de alguns recursos.

PLDA já oferece blocos IP com suporte CXL 2.0 e PCIe 5.0

É muito cedo para falar sobre as perspectivas de mercado para o CXL, apenas porque mesmo a implementação 1.0 / 1.1 requer suporte PCI Express 5.0, e não existem tais sistemas no mercado ainda. Os processadores Intel Sapphire Rapids devem receber esse suporte, mas não devem ser esperados até 2021. Você pode aprender mais sobre as especificações do CXL 2.0 enviando uma solicitação aqui.