Em fevereiro de 2024, a empresa holandesa ASML, única fabricante mundial dos mais avançados equipamentos para fotolitografia semicondutora, anunciou o início dos trabalhos na mais recente máquina High NA EUV. Já se sabe que são de 10 a 20 pedidos dessas unidades, do tamanho de um ônibus de dois andares e com preço de US$ 350 milhões, e até 2028 o fornecedor pretende atingir uma taxa de entrega de 20 unidades por ano. Supõe-se que toda fotolitografia “subnanômetro” (com um padrão tecnológico nominal de “1 nm” ou menos) no futuro previsível será produzida usando precisamente essas máquinas. E que, consequentemente, os países que não têm acesso a eles (como a RPC, cujos fornecimentos de equipamento EUV e, no futuro, de equipamento DUV são directamente proibidos pelo Departamento de Comércio dos EUA) serão em breve postos à margem da alta caminho do progresso técnico planetário. É realmente assim – e não há realmente nenhuma alternativa à fotolitografia ultravioleta extrema em termos de maior miniaturização das tecnologias de semicondutores?

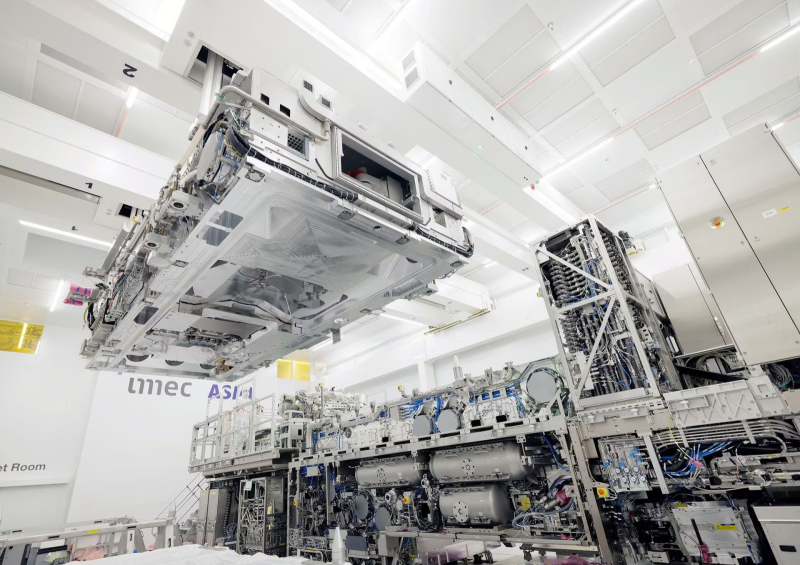

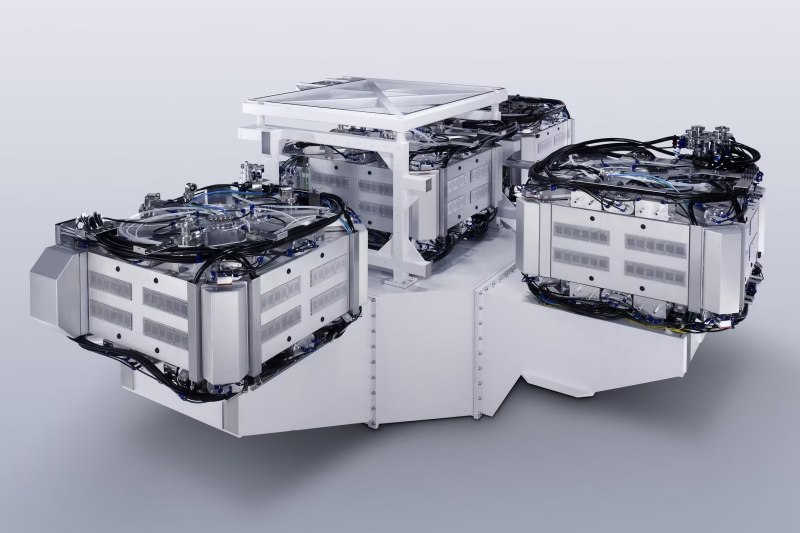

Uma das etapas finais da montagem da instalação High NA EUV na fábrica em Veldhoven holandês: o bloco com o sistema de espelhos é movido para o módulo principal com a fonte de radiação (fonte: ASML)

⇡#Fundo rochoso e rochoso

No grego antigo, λίθος significa “pedra”, e a palavra “litografia” na era pré-semicondutor denotava tanto o processo de obtenção de impressões em papel a partir de placas de pedra especialmente processadas, quanto essas próprias impressões. Uma imagem foi criada em uma pedra plana, calcária densa, com um corante gorduroso ou oleoso – na maioria das vezes com um lápis de cera, após o qual a placa de pedra foi preenchida com uma solução aquosa de goma arábica com a adição de uma pequena quantidade de ácido nítrico. Onde a superfície do calcário não estava protegida por uma película gordurosa, esta solução causticava-o ligeiramente, tornando-o hidrofílico (propenso a absorver água). Após esse tratamento, um rolo com tinta à base de óleo foi rolado sobre a pedra, lavado dos produtos químicos e umedecido com água, e essa tinta permaneceu exclusivamente nas áreas hidrofóbicas (repelentes à água); os mesmos que representavam os traços da imagem original. A seguir, só faltou colocar uma folha de papel por cima e pressioná-la firmemente com uma prensa para obter uma impressão nítida e nítida.

Posteriormente o processo foi aprimorado, passando do calcário e cera para o alumínio e produtos químicos artificiais, mas o princípio geral permaneceu o mesmo: criar uma imagem do futuro desenho na superfície da placa – ataque raso seletivo com hidrofilização das áreas expostas – limpeza e aplicação do carimbo acabado. É importante distinguir a litografia (e a sua sucessora directa, a impressão offset) da gravura em metal ou madeira: estas duas últimas técnicas envolvem a remoção de uma parte significativa do material original da base do carimbo, enquanto a pedra litográfica permanece essencialmente plana após gravura. É a mudança nas propriedades químicas da superfície (o calcário tratado com ácido se transforma em nitrato de cálcio hidrofílico e a goma arábica fecha os poros da estrutura da pedra, evitando que o corante oleoso saia fisicamente das zonas hidrofóbicas) que permite que a tinta para serem retidos nas áreas desejadas e depois transferidos para o papel, não a diferença de altura

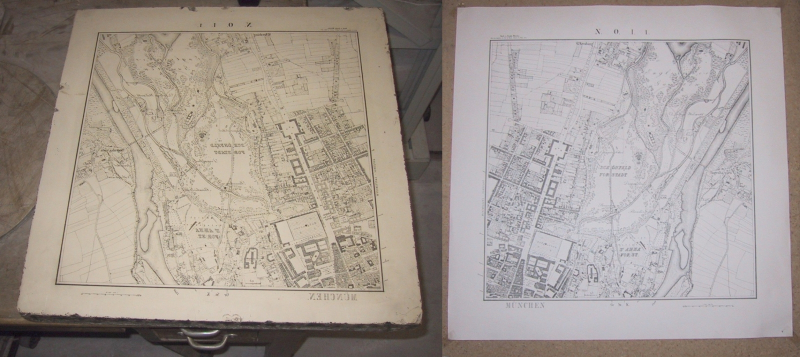

Pedra litográfica com planta de parte de Munique do início do século 19 (à esquerda) e uma impressão dela (fonte: Wikimedia Commons)

Na fotolitografia de semicondutores, a base para a criação de estruturas ordenadas também é um wafer plano – um semicondutor, na maioria das vezes silício; revestido com um fotorresiste que, após exposição a uma radiação bastante forte através de uma fotomáscara especial, altera suas propriedades químicas nas áreas que interagem com os fótons. Além disso, essas áreas são submetidas a alguma influência adicional – pode ser gravação química ou de plasma, introdução de íons, etc. – o que possibilita a criação de estruturas semicondutoras complexas na superfície da placa de base. Isso foi discutido com algum detalhe em nossos materiais anteriores sobre conquistas e dificuldades na produção de microcircuitos, por isso não entraremos em detalhes aqui. O principal é que a resolução máxima alcançável pelos métodos fotolitográficos (o tamanho mínimo característico das estruturas na superfície de uma pastilha de silício) é determinada em última análise pelo comprimento de onda da radiação utilizada para iluminação. Sim, através de uma série de truques é possível criar chips com um laser de 193 nm de acordo com os padrões de produção “7 nm” e até “5 nm”, mas a miniaturização adicional requer uma transição para ultravioleta extremo (EUV), essencialmente radiação de raios X suave – com comprimento de onda de 13,5 nm.

A tecnologia de fotolitografia EUV começou a ser desenvolvida na década de 1990 por vários centros de pesquisa financiados pelo Departamento de Energia dos EUA: os laboratórios Sandia, Berkeley e Lawrence. Assim, em 1997, Sandia patenteou uma fonte de radiação ultravioleta extrema e, em 2002, em colaboração com a TRW, demonstrou pela primeira vez um suporte de engenharia viável para fotolitografia semicondutora com comprimento de onda de 13,5 nm. Naquela época, a Intel era líder global indiscutível na indústria de microprocessadores – e foi através de seus esforços que a Extreme Ultraviolet Limited Liability Company (EUV LLC) foi formada no final da década de 1990. Esta estrutura, que além da própria Intel incluía a Motorola e a AMD, formou uma parceria com os laboratórios do Departamento de Energia com base num acordo de investigação e desenvolvimento conjunto.

Funcionários da fábrica Carl Zeiss em Oberkochen, Alemanha, diante de uma enorme câmara de vácuo na qual o sistema óptico da mais recente fotolitografia High NA EUV está sendo testado (fonte: ASML)

Com o tempo, a EUV-LLC incluiu a já mencionada ASML holandesa e a empresa SVGL, na época o único fornecedor norte-americano de motores de passo com a precisão necessária para máquinas fotolitográficas. Também foram realizadas negociações sobre a adesão ao consórcio EUV das japonesas Canon e Nikon, alemãs Infineon Technologies e outras empresas, mas o Departamento de Comércio dos EUA se opôs diretamente à inclusão de quaisquer empresas estrangeiras (com exceção da mesma ASML) nestes extremamente desenvolvimentos promissores. Em 2000, a ASML adquiriu a SVGL por 1,8 mil milhões de euros – tornando-se assim a única empresa comercial do planeta que detém os direitos de utilização de desenvolvimentos patenteados no domínio da fotolitografia EUV.

Surgiu assim o que se chama em economia de monopólio natural: na verdade, a única (não a única em geral, mas a única adequada para a produção rápida e em massa) de obter radiação de 13,5 nm ainda é complexa e extremamente consumidora de energia. método – implicando a evaporação por poderoso laser de gotículas de estanho líquido ultrapuro com diâmetro de 20-30 mícrons caindo em uma câmara especial com frequência de 50 mil unidades por segundo (é o plasma formado a partir desse procedimento que forma o fluxo de fótons EUV). E como um grande número de processos tecnológicos, soluções de engenharia e unidades de trabalho inteiras de tal instalação são protegidos por patentes intransferíveis, é simplesmente impossível para desenvolvedores terceirizados obterem plasma produzido a laser (LPP) de qualquer forma semelhante. .

Limitações puramente físicas não acrescentam espaço para manobras de engenharia: embora a tecnologia LPP utilizando várias substâncias permita, em princípio, obter radiação com comprimentos de onda de 4 a 20 nm, um espectro quase monocromático adequado para uso industrial com um máximo pronunciado só é possível no caso de estanho – os mesmos 13,5 nm. Ou seja, não é sequer possível romper formalmente com os limites traçados pelas patentes propondo algum outro fluido de trabalho em vez do estanho.

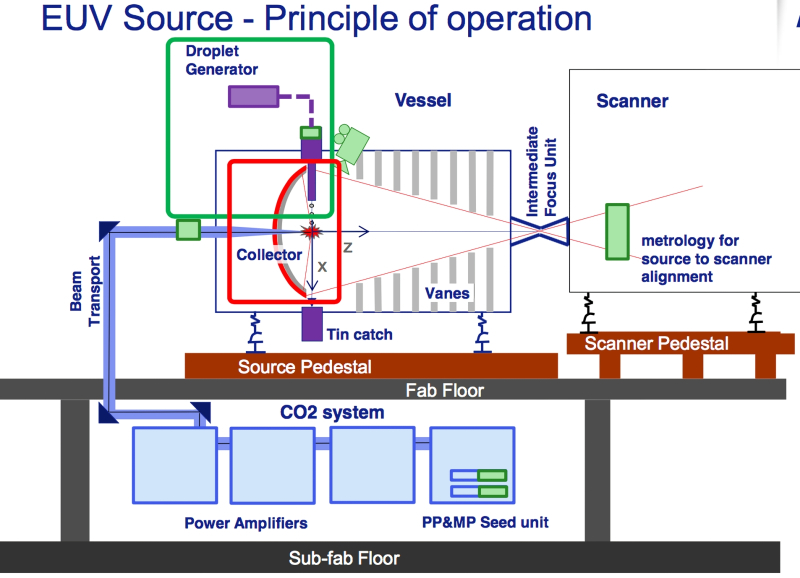

Diagrama esquemático de uma fotolitografia EUV: o laser de dióxido de carbono está localizado sob o piso da instalação principal, cuja maior parte do volume recai sobre a unidade de geração de plasma (fonte: ASML)

Em suma, embora as autoridades americanas continuem a bloquear a transferência de patentes para desenvolvimentos EUV (em grande parte financiados por agências governamentais dos EUA, notamos por uma questão de justiça) para fabricantes terceiros de equipamento fotolitográfico, a ASML detém o monopólio na produção de máquinas para fabricação de chips funcionam a partir de “3 nm” e abaixo da escala de tamanho continuarão a persistir. Outra coisa é que nos últimos anos têm vindo a desenvolver-se uma série de tecnologias promissoras, pelo menos uma das quais – e talvez mais do que uma – tem a oportunidade de se tornar a base para a miniaturização contínua dos padrões de produção na indústria de semicondutores sem o envolvimento de EUV. Quais são exatamente as direções que essa pesquisa está tomando?

⇡#Então, menos ou mais é melhor?

A rigor, se o processo de produção do LPP EUV fosse inteiramente satisfatório para os clientes finais – desenvolvedores de chips semicondutores, o monopólio da ASML na fabricação das máquinas correspondentes não seria um fardo pesado para o mercado global de TI. Este mercado é geralmente propenso ao monopólio, pois simplifica muito a padronização – vejamos, por exemplo, a interface USB (para a qual até a Apple concordou recentemente em mudar, tendo interrompido o desenvolvimento a longo prazo de seus próprios conectores Lightning) ou “aberta” ( até certos limites) arquiteturas de processador x86 e ARM. Todos os tipos de chips são procurados no mundo em tais volumes que, de fato, a máquina mais avançada para sua produção contínua custará US$ 350 milhões, 500 milhões ou 750 – a diferença para o consumidor final não será muito grande. O problema é que, já no seu estado atual, a tecnologia LPP EUV causa certas preocupações entre os representantes da indústria – em termos da possibilidade de sua melhoria economicamente adequada.

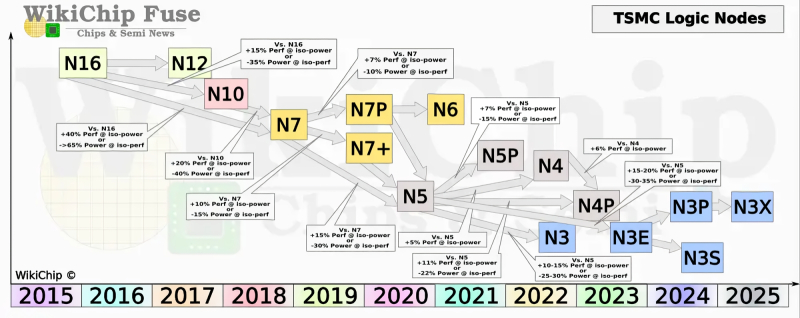

Evolução dos processos tecnológicos da TSMC de “16 nm” para “3 nm” por ano; Blocos de notas indicam em que porcentagem o novo padrão de produção proporciona aumento de produtividade ou diminuição de potência em relação ao anterior (fonte: WikiChip)

Um exemplo vivo: se a primeira versão do processo técnico “3 nm” dominado pela TSMC, N3B (básico), previa 25 procedimentos de exposição sequencial da peça à radiação EUV (mais, em cada um desses ciclos, as etapas de acompanhamento de aplicação de fotorresistente, ataque químico, lavagem, etc.), então o próximo é N3E (aprimorado) – já 19. Não mais operações – para obter estruturas mais densas usando o método de fotolitografia de duas passagens, por exemplo – mas menos ! Qual é a razão?

Especialistas independentes acreditam – é claro que os próprios fabricantes de chips e os desenvolvedores de máquinas para eles se abstêm de discussões públicas sobre um tema tão delicado – que a questão é precisamente a eficiência energética extremamente baixa do plasma de estanho induzido por laser como fonte de radiação. Já discutimos com algum detalhe as dificuldades que os engenheiros enfrentam durante a fotolitografia de 13,5 nm e observamos que a principal razão para os problemas com a miniaturização adicional do processo semicondutor é a energia muito alta de cada fóton individual que atinge a camada fotorresistente na peça de trabalho. chip futuro.

Quanto mais próximo de dezenas e até mais unidades de angstroms estiver o tamanho característico real das estruturas na superfície do microcircuito, maior será o impacto que a estocástica tem na qualidade do dispositivo acabado. Ela se manifesta tanto na distribuição desigual de moléculas fotorresistentes sobre a superfície revestida com esta substância, quanto na natureza aleatória das cascatas secundárias de partículas geradas por poderosos fótons EUV na espessura do fotorresistente. Como resultado, cada degrau sucessivo na escada x-nm dos padrões de produção é muitas vezes mais caro que o anterior: a fração inicial do rendimento de chips adequados de um wafer padrão é, via de regra, ridiculamente pequena, e notável esforços de engenharia são necessários para aumentá-lo ao mínimo adequado para produção em massa de 70 a 80%. Aqui é importante entender que erros (falhas) causados estocasticamente não são defeitos tecnológicos (defeitos) que podem ser eliminados melhorando padrões e procedimentos: a partir de uma certa escala (e os fabricantes de chips de “3 nm” agora dominados já estão perigosamente próximos de isto) aleatório e fundamentalmente a natureza imprevisível de sua ocorrência anula literalmente todos os esforços para combatê-los.

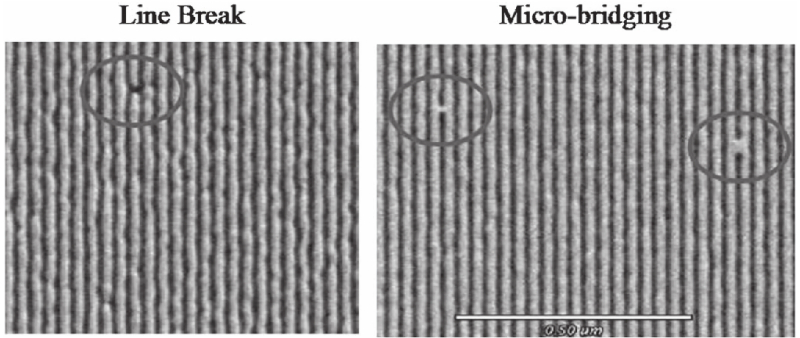

Fotomicrografias de erros estocásticos em fotolitografia EUV: quebra de linha sólida (esquerda) e junção de linha indesejada; a distância característica entre as linhas é de 30 nm (fonte: The Japan Society of Applied Physics)

Talvez a única forma de contrariar eficazmente as manifestações da estocasticidade seja regressar de eventos únicos a grandes números; operam não com dezenas e unidades, mas com centenas, ou melhor ainda, milhares de partículas, de modo que o “mau comportamento” de fótons individuais seja calculado e suavizado. Mas aqui está o problema: um fóton com comprimento de onda de 13,5 nm tem 14 vezes mais energia que um de 193 nm e, portanto, se for 1 nm² de um fotorresiste padrão que precisa ser exposto a uma dose de pelo menos 10 mJ/cm² para “disparar”, 97 fótons DUV, então as partículas EUV mais poderosas são apenas 7. A incerteza relativa de medição é inversamente proporcional à raiz quadrada do número de eventos, e enquanto para quase cem fótons de 193 nm ela está em uma situação completamente faixa aceitável de ± 10% (o que, de fato, permite aos engenheiros aumentar teoricamente a porcentagem de chips utilizáveis de um wafer para 90%, eliminando gradualmente defeitos de fabricação), então, para sete partículas de 13,5 nm, a incerteza dispara instantaneamente para ± 40% – e esta barreira é polida por polimento de munhão, limpeza de eixos ópticos e outros métodos puramente procedimentais não podem ser superados.

Existem, em geral, duas saídas aqui: você precisa aumentar a dose de exposição à radiação EUV por meio de exposições repetidas (em vez de um pulso, produza, digamos, uma dúzia) ou aumentando a potência da fonte de radiação, concentrado em um único pulso. O primeiro método é atrativo pela sua simplicidade, porém, no caso de produção contínua, acaba sendo pior que o roubo, pois multiplica o tempo de processamento de cada placa de peça e, além disso, exatamente da mesma forma, é aumenta o desgaste relativo (em termos de uma placa acabada) dos elementos internos da fotolitografia: espelhos de Bragg, matrizes fotográficas, etc. A única maneira de retornar os investimentos em fotolitografias EUV incrivelmente caras em um tempo razoável é trazê-las à produtividade máxima o mais rápido possível (medido pelo número de chips condicionalmente utilizáveis por hora) e desacelerar deliberadamente o processo de produção várias vezes obviamente não contribui para isso.

O segundo método para aumentar o número de fótons que atingem o fotorresistente é multiplicar a potência de um único fluxo de radiação ultravioleta extrema. No entanto, a unidade LPP para gerar tais partículas é muito difícil de escalar em potência: se as primeiras máquinas EUV operavam com geradores de feixe de trabalho de 250 W, então as instalações avançadas de High NA EUV já precisam de 600 W – e este é praticamente o limite além do qual um fluxo excessivamente denso de partículas de alta energia começará a destruir elementos do caminho óptico do sistema a uma velocidade que é simplesmente inaceitável para um negócio com fins lucrativos. Afinal, a progressiva miniaturização dos processos tecnológicos na produção de semicondutores está sendo implementada não por puro amor à solução de problemas de engenharia inusitados, mas para obter lucros tangíveis em um prazo bastante razoável.

Unidades de laser de dióxido de carbono para fotolitografia EUV também são produzidas pela única empresa no mundo – TRUMPF de Ditzingen, Alemanha (fonte: TRUMPF)

De acordo com uma avaliação realizada em 2019 por especialistas da Kioxia, para fotolitografia eficaz de estruturas semicondutoras com padrões de produção de “3 nm” e “2 nm” (eficaz no sentido de que a densidade de fótons no feixe de trabalho será suficiente para reduzir o influência dos efeitos estocásticos na qualidade) Serão necessários emissores EUV com potência de 1,5 a 2,8 kW. A tecnologia LPP, nem no seu estado atual nem no futuro próximo, é capaz disso e, portanto, a ideia de abandonar o complexo método multiestágio de obtenção de um fluxo de fótons de 13,5 nm parece completamente natural. Na verdade, como é inútil brincar com a transformação do estanho em plasma com pulsos de laser, talvez seja possível construir um laser que gere imediatamente radiação coerente com o comprimento de onda necessário?

⇡#Liberdade para os elétrons!

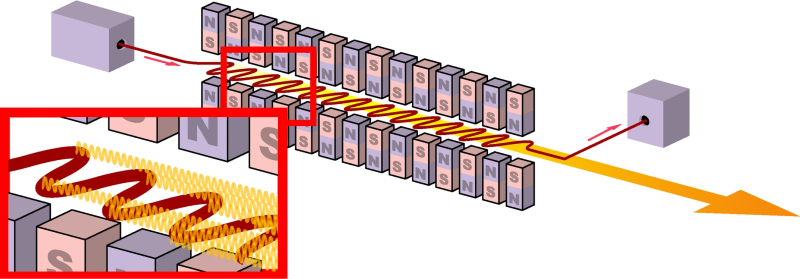

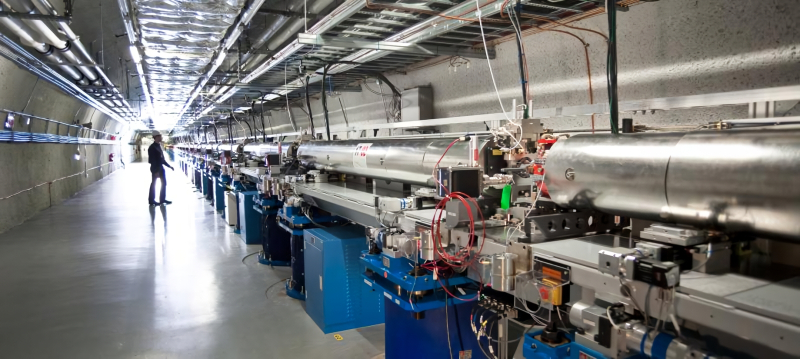

Um projeto de emissor teoricamente adequado é conhecido pela ciência – este é o laser de elétrons livres (FEL), proposto em 1971 por John MJ Madey. O princípio de operação do dispositivo é direcionar um feixe de elétrons, acelerado a velocidades abaixo da luz dentro de um acelerador linear, em um ondulador ou wiggler – uma série de ímãs localizados sequencialmente com um campo transversal espacialmente periódico. Lasers mais convencionais baseados em elétrons ligados a moléculas ou átomos não são adequados para gerar luz ultravioleta extrema, até porque um elemento essencial de seu design é um ressonador óptico – espelhos translúcidos e transparentes que limitam o volume do fluido de trabalho – e quais problemas técnicos surgem da necessidade de refletir efetivamente a radiação EUV, discutimos em detalhes no material relevante anteriormente. Os lasers de elétrons livres não apenas fornecem a capacidade de ajustar suavemente (e em uma ampla faixa) o comprimento de onda da radiação emitida, mas também são dispositivos essencialmente clássicos e não quânticos, uma vez que cada elétron, ao passar pelo ondulador, consegue emitir dezenas , ou mesmo centenas de milhares de fótons. Isso elimina automaticamente o problema da estocasticidade – tudo o que resta é selecionar materiais fotorresistentes que resistam adequadamente ao aumento da densidade de fluxo da radiação de alta energia.

Ondulador – é fácil! (Fonte: Wikimedia Commons)

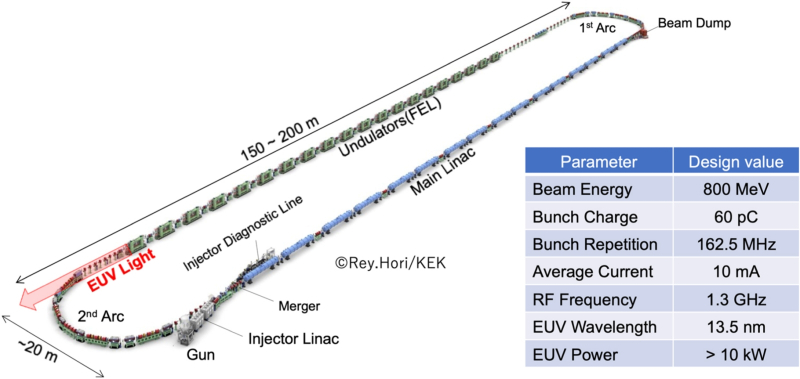

A Organização Japonesa de Pesquisa de Aceleradores de Alta Energia (a abreviatura tradicionalmente aceita de seu nome em japonês é KEK) propôs recentemente um protótipo conceitual da instalação FEL EUV, especificamente destinada ao uso na fabricação de chips. Uma máquina com 200 m de comprimento (é exatamente quanto ocupam as seções retas de seus aceleradores) gerará um feixe de fótons de 13,5 nm com potência de 10 kW e, segundo estimativas preliminares, custará US$ 400 milhões, mais cerca de outros US$ 40 milhões para manutenção e suporte anuais. Entre suas vantagens está a escalabilidade (o feixe de fótons na saída pode ser dividido em fluxos paralelos, garantindo a operação não de uma fotolitografia de 10 kW, mas, digamos, dez de uma vez, 1 kW cada) e a capacidade de reconfiguração para outros comprimentos de onda (por exemplo, 6 nm, se 13,5 for insuficiente num futuro próximo, ou mesmo 1 nm). Além disso, o projeto da instalação KEK é muito eficiente em termos energéticos: com um consumo de energia de 7 MW, para cada quilowatt de feixe de trabalho criado, os desenvolvedores estimam que serão consumidos 0,7 MW de eletricidade. No caso do LPP EUV, esta taxa de conversão é muito menor: 4,4 MW de consumo de energia por 1 kW de potência do feixe de fótons.

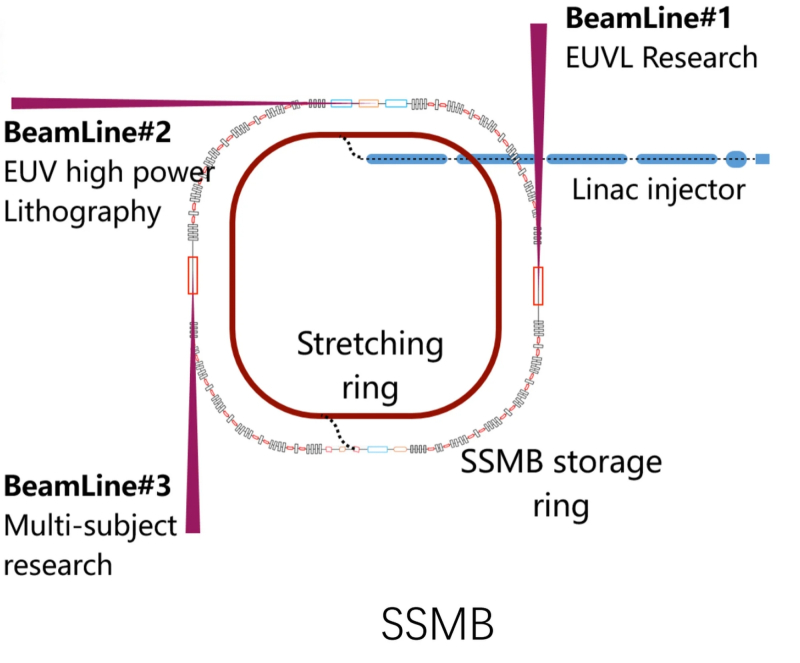

Desenvolvimentos no campo do FEL estão atualmente em andamento na Europa (projeto europeu XFEL), EUA (projeto SLAC), China (onde já existem planos para usar lasers de elétrons livres para fotolitografia de semicondutores até 2035). Além de uma instalação com acelerador linear, também é possível obter feixe de elétrons de alta energia em aceleradores de anéis ressonantes, principalmente síncrotrons, e projetos para um gerador EUV de potência em quilowatts baseado em síncrotrons também já estão sendo considerados. Em particular, no outono de 2023, soube-se que a Universidade Tsinghua da China estava a preparar-se para lançar uma “arma de litografia” – um acelerador com microbunching em estado estacionário (SSMB).

O princípio SSMB – proposto em 2010 pelo professor de Stanford Zhao Wu e seu aluno Daniel Ratner – envolve o armazenamento de elétrons de alta energia em um anel acelerador, estratificando-os por velocidade, de modo que em vez de um fluxo pulsado de fótons (como em um acelerador linear) para receber radiação contínua em certos comprimentos de onda. Embora a implementação prática do SSMB EUV por investigadores da Universidade de Tsinghua possa levar, segundo os especialistas, de 5 a 13 anos, à luz do reforço contínuo das restrições do Departamento de Comércio dos EUA ao fornecimento de equipamento de produção de chips à RPC – não apenas equipamentos americanos, mas também aqueles produzidos em outros países usando patentes americanas – parece não haver outra maneira de substituir aqui a fonte LPP EUV.

Projeto do laser de elétrons livres EUV e suas principais características (fonte: KEK)

É verdade que o mais difícil é o começo: para reproduzir de forma independente uma fotolitografia capaz de assar microcircuitos de acordo com padrões tecnológicos de “3 nm” ou menos, escolher um gerador de fluxo de fótons adequado de 13,5 nm ainda não é suficiente. Embora a fonte FEL ou SSMB possibilite implementar um projeto óptico mais simples do que o projeto LPP com suas dezenas de refletores de Bragg, a radiação na saída do acelerador ainda terá que ser de alguma forma redirecionada para a fotomáscara e depois para a placa da peça de trabalho revestido com fotorresistente, então existem espelhos esféricos e asféricos de ultraprecisão (polidos literalmente para tolerâncias nanométricas). Aqui, de uma forma ou de outra, serão necessários.

E a produção deste tipo de ótica é uma área de engenharia completamente especial: não é por acaso que a ASML encomenda espelhos e lentes para as suas máquinas ao único fornecedor em todo o mundo – a alemã Carl Zeiss AG. É claro que este estado de coisas se deve em grande parte ao monopólio dos fabricantes holandeses de fotolitografias EUV: nenhum outro fabricante de sistemas ópticos, incluindo os muito dignos japoneses a este respeito (Canon, Nikon), devido à falta de um potencial de vendas mercado, simplesmente não tinha necessidade de desenvolver as competências correspondentes no nível adequado. É provável que, mais cedo ou mais tarde, a óptica chinesa comece a fornecer espelhos adequados para a produção de EUV em linha. Mas é preciso desenvolver essa área separadamente da construção e finalização do acelerador SSMB, o que exige investimentos adicionais consideráveis – e, claro, tempo. Recordemos que a ASML começou a trabalhar na área da fotolitografia EUV em 1997, e apenas em 2022 – um quarto de século depois! – o primeiro dispositivo serial desta classe iniciou a produção em linha (em vez de pequenos lotes experimentais) de chips.

No entanto, todas as discussões sobre o retorno razoável do investimento na produção de microprocessadores só fazem sentido em condições económicas normais, no caso extremo – para um mercado mundial superglobalizado, quando a capacidade de produção de um fornecedor de equipamento EUV (o mesmo ASML) é mais do que suficiente para satisfazer a demanda de alguns fabricantes líderes de chips (TSMC, Samsung Electronics, Intel). A partir do qual, por sua vez, qualquer desenvolvedor de chips de qualquer país – com o orçamento disponível necessário, é claro – tem a oportunidade de encomendar um lote de chips de acordo com seu próprio projeto de engenharia (como fizeram os projetistas do russo Baikal-M, transformando para a TSMC como fornecedora ODM, por exemplo). Na realidade da desglobalização digital – que ainda não atingiu o nível de protocolos e padrões mutuamente incompatíveis, mas já está próximo – o custo e o retorno das tecnologias inovadoras tornam-se menos significativos em comparação com a sua disponibilidade potencial para as necessidades urgentes de um determinado estado. . E, nesse sentido, não se deve descartar uma tecnologia de fabricação de chips tão conhecida como a litografia sem máscara – não mais “foto”, já que a ferramenta de trabalho aqui não é um feixe de fótons, mas elétrons ou íons de alta energia.

Diagrama de projeto do acelerador SSMB que está sendo projetado na Universidade de Tsinghua: a estratificação de elétrons por velocidade permite a geração de radiação EUV com diferentes comprimentos de onda e finalidades diferentes (fonte: Universidade de Tsinghua)

Para a fotolitografia de projeção utilizada na produção em larga escala, talvez o critério mais importante seja a produtividade, medida no número de wafers brutos processados por hora (desde o carregamento na fotolitografia até a obtenção do produto acabado, que é então transferido para uma empresa especializada para cortar os wafers em chips individuais e testá-los e embalá-los em caixas com contatos de montagem). Como a peça de trabalho é exposta através de uma máscara fotográfica, em seções relativamente grandes de uma só vez, a produtividade é alta – até 170 chapas por hora para as atuais fotolitografias EUV. Um litógrafo sem máscara traça as estruturas desejadas na superfície de um wafer com um feixe estreito de partículas carregadas – um processo muito parecido com a gravação a laser – de modo que a velocidade é drasticamente reduzida para cerca de 0,1 wafer por hora. E se também levarmos em conta a necessidade de exposição repetida para uma série de operações particularmente delicadas, a velocidade real de cozimento dos chips acabados pode ser ainda menor.

⇡#Feixes, íons, selos

Na verdade, uma litografia sem máscara também é possível com base num feixe de fótons de raios X suaves (ou ultravioleta extremo) – como a unidade que está sendo desenvolvida pelo Instituto de Tecnologia Eletrônica de Moscou (MIET) “baseada em um síncrotron e/ou fonte de plasma. ” O baixo desempenho de tal dispositivo não é um problema quando o volume potencial de vendas de chips fabricados nele não é calculado em bilhões, mas em dezenas e centenas de milhares. É interessante que a fotomáscara na litografia proposta ainda esteja virtualmente presente – seu papel é desempenhado por um conjunto de microespelhos baseados em matrizes MEMS, que permite, ao expandir o diâmetro do feixe (e, consequentemente, a área da superfície da peça exposto simultaneamente a ele), para realizar rapidamente litografia de elementos semicondutores com detalhe característico de 28 nm ou menos.

Presumivelmente, neste caso, não estamos falando do nome nominal de marketing do processo tecnológico, mas de resoluções fisicamente alcançáveis: por exemplo, o processo tecnológico TSMC N3E de “3 nm”, implementado via LPP EUV, fornece uma distância característica entre barramentos de metal adjacentes (passo metal-metal, MMP) em um nível de 23 nm, e entre cristas de transistor adjacentes (passo de aleta) – 26 nm. Uma litografia sem máscara usando fótons de alta energia é perfeitamente capaz de atingir escalas semelhantes usando tecnologias disponíveis hoje – deixando de lado por enquanto a questão de como exatamente o fluxo de trabalho de fótons de 13,5 nm será gerado.

«O Undulator Hall no grande sistema de acelerador linear SLAC consiste em 32 onduladores com 224 ímãs poderosos cada (fonte: Universidade de Stanford)

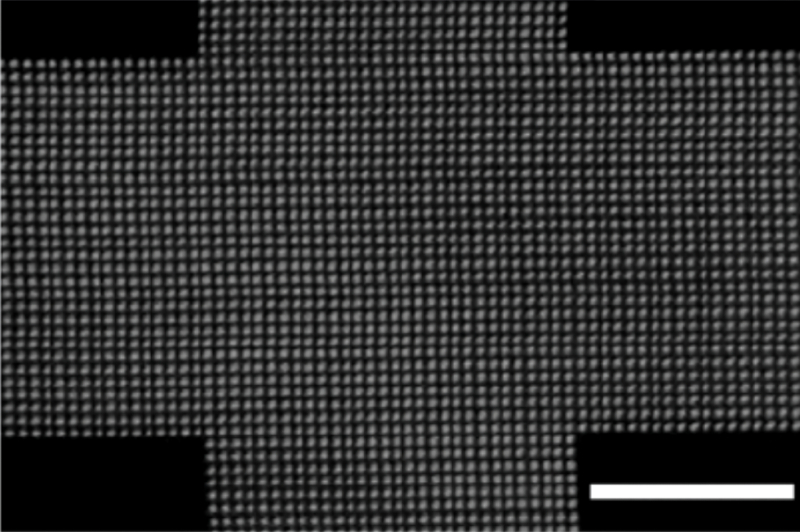

A litografia eletrônica, ou litografia por feixe de elétrons (litografia por feixe eletrônico), não é essencialmente muito diferente da litografia de raios X sem máscara: aqui o substrato, que é sensível – neste caso ao fluxo de elétrons em vez de fótons – é similarmente submetido a exposição sequencial a um feixe estreito de partículas. Como resultado, as áreas “expostas” alteram suas propriedades químicas, o que torna possível realizar ainda mais as operações usuais de fotolitografia na peça – fixação, gravação, etc. A litografia eletrônica torna possível a formação em equipamentos atualmente disponíveis (essencialmente os mesmos como aquelas usadas para projetar microscópios eletrônicos de varredura) estruturas semicondutoras com resolução característica de 10 nm ou até menos, mas a velocidade de processamento das peças é extremamente baixa mesmo em comparação com a litografia de raios X sem máscara. Por esta razão, os feixes de elétrons são utilizados principalmente para a fabricação de fotomáscaras e, menos comumente, para a produção em pequena escala de dispositivos semicondutores complexos.

A litografia por feixe de íons desenvolve a ideia da litografia por feixe de elétrons, usando partículas pesadas carregadas – geralmente íons de hidrogênio (prótons) ou hélio – para formar um feixe. O aumento da massa de partículas no fluxo possibilita a criação de feixes energeticamente densos; Além disso, o bombardeio pesado de substratos especialmente selecionados garante a formação de camadas finas com novas propriedades químicas – sem a necessidade de aplicar primeiro uma substância polimérica semelhante ao fotorresistente. Além disso, as partículas pesadas possuem inércia significativa, o que reduz seu espalhamento na espessura do material exposto – e assim elimina os efeitos estocásticos característicos dos fótons EUV, mesmo para feixes de densidade relativamente baixa. Isto permite maior resolução do que no caso da litografia eletrônica, e o uso de impurezas de certos elementos no feixe de íons permite dopar seletivamente o material do substrato com alta precisão e sem o uso de métodos químicos. É verdade que, como os íons massivos são absorvidos pelo material exposto com muito mais eficiência do que as partículas mais leves, surgem dificuldades com a formação de estruturas essencialmente tridimensionais (como as cristas FinFET), mas os engenheiros aprenderam a lidar com elas. Mas a velocidade reduzida de processamento das peças durante a litografia por feixe de íons – mesmo em comparação com a litografia eletrônica – continua a ser sua desvantagem significativa.

Imagem de microscopia eletrônica de varredura de nanoestruturas produzidas por litografia por feixe de íons; comprimento do segmento dimensional (canto inferior direito) – 400 nm (fonte: Microelectronic Engineering Journal)

A propósito, a litografia sem máscara, muito mais do que a LPP EUV, lembra o próprio método de criação de imagens replicadas em placas de pedra, com as quais compartilha seu nome, só que aqui um feixe de partículas carregadas é usado em vez de um lápis de cera para alterar as propriedades químicas da superfície da peça de trabalho. Porém, antes do surgimento da litografia como processo artístico no final do século XVIII, o principal meio de produção seriada de gravuras durante séculos foi a gravura incisiva, cuja principal característica é a significativa diferença de altura entre os fragmentos elevados do carimbo esculpido, que é pressionado contra o papel, e os recuados, onde se acumula tinta. As próprias depressões são obtidas por ataque profundo ou por remoção física do material.

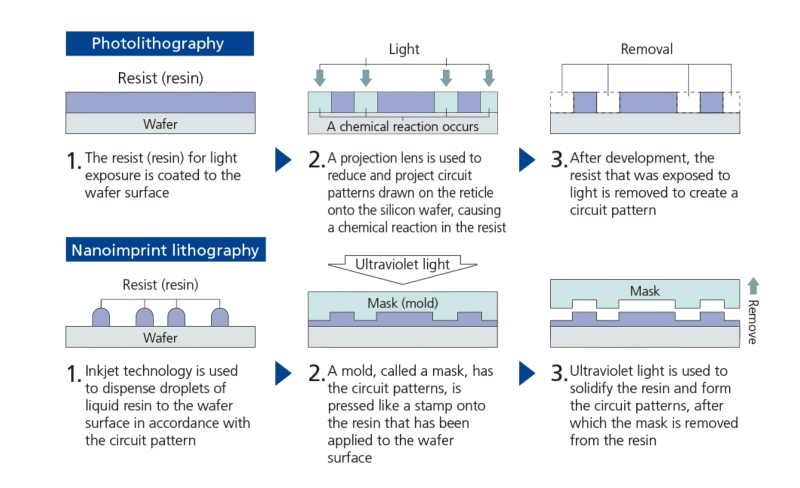

Acontece que um método semelhante em espírito é bastante adequado para a produção de nanoestruturas semicondutoras. Em 2014, a japonesa Canon adquiriu a empresa americana Molecular Imprints e desde então vem desenvolvendo ativamente, embora não muito apressadamente, um novo rumo na produção de microeletrônica – a litografia de nanoimpressão (NIL). Seria mais correto chamar esse método de “nanoformação”, pois se trata de nivelar um fotorresiste na superfície da peça com um carimbo especial (molde) – que, aliás, é pré-gravado usando na maioria das vezes elétrons litografia por feixe. Uma impressora jato de tinta especializada com bicos nanométricos forma os contornos das futuras estruturas semicondutoras no wafer – as mesmas que, no caso da fotolitografia, se formam em áreas cobertas pela sombra de uma fotomáscara. Em seguida, o carimbo, no qual estão gravados os mesmos contornos (na forma inversa: uma saliência no local onde será necessário o recesso na peça), é pressionado contra a placa – e gotas de fotorresiste sob ele preenchem os recessos designados, formando nanoestruturas das configurações e tamanhos necessários. Em seguida, diretamente através do carimbo, que é transparente à radiação ultravioleta, um poderoso flash é utilizado para fixar a substância fotossensível. Em outras palavras, não apenas o procedimento de exposição do fotorresistente através de uma fotomáscara, fixando as áreas necessárias, gravando e lavando áreas desnecessárias, mas também todo o volumoso conjunto óptico – junto com a fonte de radiação e um conjunto de lentes/espelhos – são excluído do ciclo de produção.

Comparação passo a passo das principais etapas da fotolitografia semicondutora (acima) e da litografia nanoimpressa (fonte: Canon)

Parece ridiculamente simples, mas ainda existem muitas dificuldades técnicas a superar no caminho para transformar a NIL num concorrente de pleno direito da LPP EUV. A Canon anunciou no final de 2022 o início da construção de uma fábrica para a produção de litografias de nanoimpressão, que custará à empresa US$ 345 milhões (estimado no momento do início dos trabalhos) e, presumivelmente, começará a produzir produtos acabados em 2025 – durante este tempo será necessário aperfeiçoar todas as etapas de produção contínua de microcircuitos em unidades nanoimpressas. E antes de tudo, o alinhamento (com precisão subnanométrica!) das máscaras aplicadas sequencialmente à peça de trabalho, porque esses chips, como qualquer um de seus análogos modernos, conterão uma dúzia ou uma camada e meia de várias interconexões. Mais adiante na lista de desafios de engenharia enfrentados pela produção de chips de nanoimpressão está a violação das proporções originais do selo devido às mudanças de temperatura, a necessidade de garantir “limpeza” (sem aderência – com subsequente separação parcial e outros danos – impressos e ultravioleta- nanoestruturas verticais fixas) desprendimento do carimbo da peça etc. Mas ainda assim, o jogo vale a pena: segundo a Canon, o consumo de energia do NIL é 90% menor do que o de uma máquina LPP EUV que produz microcircuitos de escala comparável classe, e o custo de processamento de um único wafer convencional é 50% menor.

Anunciada no outono de 2023, a litografia de nanoimpressão FPA-1200NZ2C (presumivelmente, essas máquinas são atualmente fabricadas individualmente por uma empresa japonesa em empresas existentes enquanto uma fábrica especialmente projetada para elas está sendo construída) é capaz, de acordo com a Canon, de formar semicondutores estruturas com resolução real na superfície da peça de trabalho de 14nm, o que é aproximadamente equivalente ao processo “5nm” em máquinas LPP EUV. No futuro, afirma o desenvolvedor, os procedimentos de confecção de carimbos e aplicação de fotorresistente na peça poderão ser melhorados tanto que fornecerão uma resolução real de 10 nm – isso já corresponderá à norma de marketing de “2 nm”. Para começar, como espera a administração da Canon, os fabricantes de memória NAND semicondutora estarão interessados em máquinas NIL, uma vez que para esses chips multicamadas com repetibilidade extremamente alta de estruturas em cada camada, é muito mais lucrativo usar estampagem repetida do que exposição repetida através de um fotomáscara (com o inevitável esgotamento do recurso deste componente caríssimo).

A primeira litografia de nanoimpressão serial do mundo operando na classe de tamanho de 5 nm é a FPA-1200NZ2C (fonte: Canon)

De uma forma ou de outra, no marco dos “2 nm”, em apenas um ou dois anos, pelo menos três tecnologias diferentes de fabricação de chips já poderão convergir – LPP EUV, nanoimprint e sem máscara. É extremamente difícil dizer agora qual deles sairá vitorioso desta luta. Além disso, se a desglobalização da indústria das TI continuar ao ritmo actual, poderão muito bem formar-se zonas tecnológicas de TI vizinhas e apenas parcialmente sobrepostas – não necessariamente apenas duas, a propósito – cada uma das quais será dominada pelo seu próprio processo litográfico.