O barramento PCI Express tem sido o padrão de fato: não requer muitos pinos, seu desempenho por pista já atingiu ≈4 GB / s (32 GT / s) na versão PCIe 5.0 e o uso do CXL stack tornará o PCI Express verdadeiramente universal. Mas para conectar chiplets ou comunicação entre processadores, este barramento em sua forma atual não é adequado da melhor maneira.

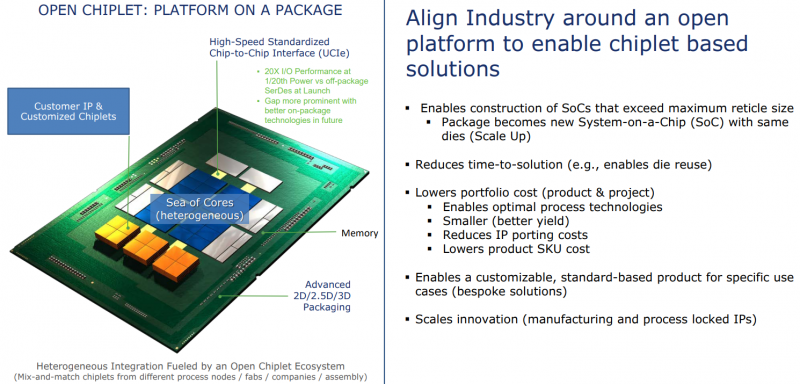

Mas o uso de tecnologias proprietárias limita significativamente o potencial das soluções de chiplet e, em março deste ano, 10 grandes desenvolvedores, incluindo AMD, Qualcomm, TSMC, Arm e Samsung, fundaram o novo padrão Universal Chiplet Interconnect Express (UCIe) para superar essa limitação .

Imagem: Consórcio UCie

Já a primeira implementação do UCIe deve superar o PCI Express em muitos aspectos: se a pista PCIe 5.0 for de quatro pinos físicos com largura de banda de 32 GT/s, então o UCIe permitirá a transmissão em um único pino até 12 Gb/s, e então a barra será aumentada para 16 Gb /com. Ao mesmo tempo, o consumo de energia do UCIe é menor e a eficiência é maior. Na mesma distância do PCIe, o novo padrão pode ser quatro vezes mais rápido com o mesmo número de condutores.

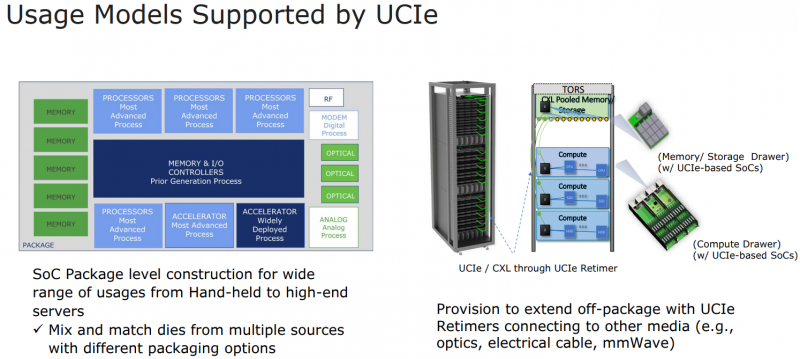

No futuro, esse número pode ser aumentado em até 10-20 vezes, ou seja, obviamente não haverá um gargalo entre os chiplets UCIe. Além disso, a nova interconexão não é apenas compatível nativamente com o CXL, mas também muito mais adequada para tarefas de desagregação. Em outras palavras, a comunicação rápida diretamente entre chipsets é possível não apenas no mesmo pacote ou dentro do nó, mas também fora dele.

Imagem: Consórcio UCie

A Intel está muito interessada no novo padrão, que planeja usar UCIe de forma que na próxima geração de processadores, núcleos x86 possam coexistir com Arm ou RISC-V. Ao mesmo tempo, está planejado garantir a compatibilidade UCIe com as tecnologias de empacotamento Intel EMIB e TSMC CoWoS, ao mesmo tempo adicionando suporte para outros barramentos, incluindo Arm AMBA, bem como a capacidade de converter facilmente para protocolos proprietários de outros desenvolvedores.

Atualmente, a Intel já possui vários exemplos de uso de UCIe. Assim, em uma das opções, os aceleradores e uma unidade de controle são conectados aos núcleos do processador usando o novo barramento, e o pacote EMIB é usado para conectar o chip à memória DDR5 desagregada e às linhas PCI Express.