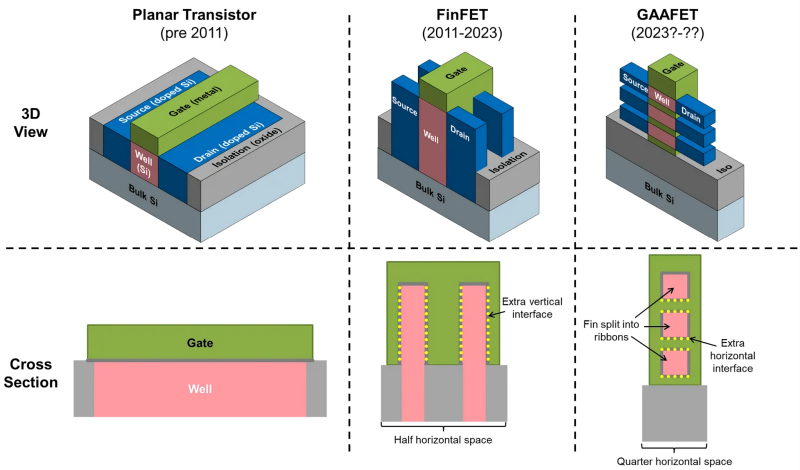

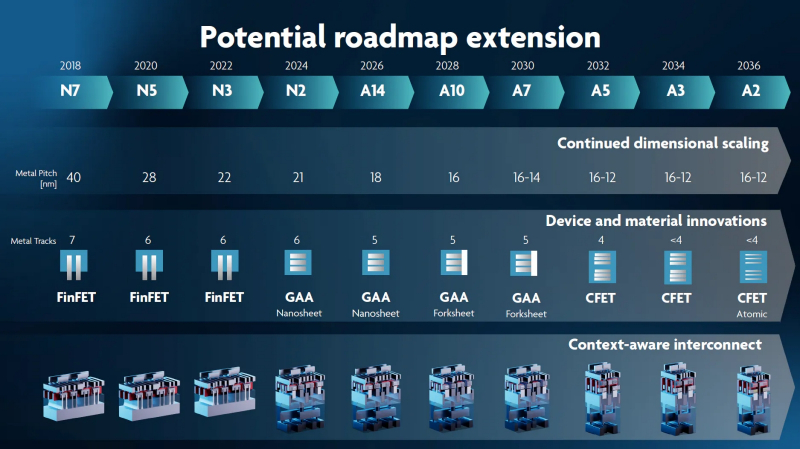

No verão de 2022, a divisão de semicondutores da Samsung Electronics informou o início da produção em série de microcircuitos utilizando o processo técnico “3 nm”, cuja característica distintiva era a produção de transistores GAAFET avançados em um substrato de silício usando sua própria nanofolha tecnologia, que é considerada superior a um conceito inicial de nanofios porque fornece uma área de canal maior para a carga elétrica fluir através do transistor. Ao mesmo tempo, a TSMC, hoje líder indiscutível no volume de VLSI “3 nm” fabricados para clientes, continua a contar com transistores “comb” ou “fin” da geração anterior, FinFET, considerando a possibilidade de desenvolver GAAFET não antes de 2025. E a Intel pretende mudar para uma “fita” proprietária – RibbonFET – implementação da abordagem GAA na fabricação de transistores não antes do segundo semestre de 2024, começando apenas com a tecnologia de processo “Intel 20A”. Mas qual é exatamente a diferença – e por que o usuário final deveria, em princípio, se preocupar com que tipo de transistores estão localizados sob o capô do próximo processador, ou mais precisamente, sob a tampa da caixa?

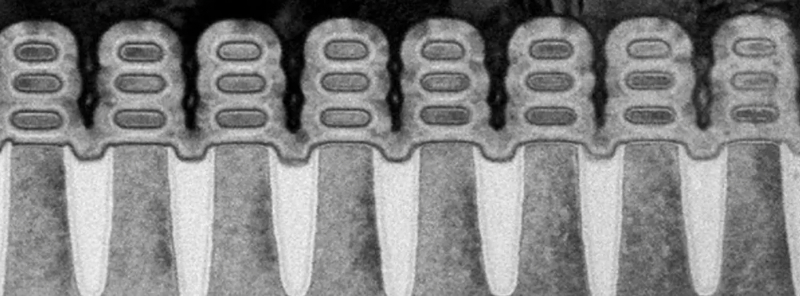

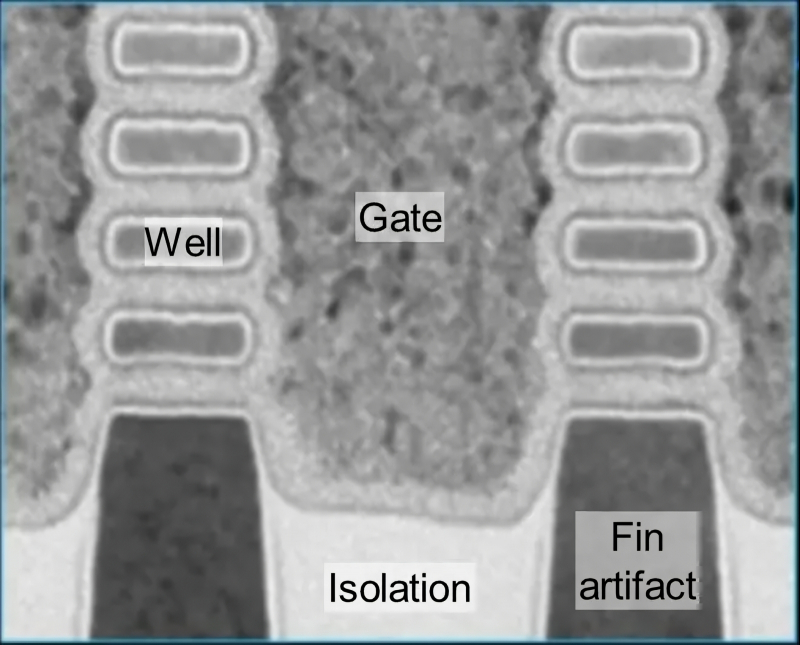

Seção transversal (através das aletas, ao longo da porta envolvente) de um chip litografado com transistores GAAFET (fonte: IBM)

⇡#Levante suas nadadeiras!

O elemento básico da moderna tecnologia de computação de semicondutores, uma espécie de “átomo” de qualquer estrutura de microprocessador, é um transistor de efeito de campo de porta isolada, também conhecido como MOSFET. Este nome (MOSFET, transistor de efeito de campo semicondutor de óxido metálico) vem de uma indicação direta da composição química dos componentes estruturais do projeto dos primeiros dispositivos desse tipo: sua porta era feita de metal, a base ( em cuja espessura se forma um canal para o fluxo de carga elétrica) havia um semicondutor, e entre esses dois elementos havia uma fina camada isolante de dielétrico – geralmente óxido de silício. Examinamos anteriormente com algum detalhe o princípio de funcionamento do transistor MOS e as dificuldades associadas à miniaturização de sistemas semicondutores devido às suas propriedades físicas. O resultado final é que o transistor forma um canal através do qual uma carga elétrica se move da fonte para o dreno, e a porta controla se esse canal está aberto ou fechado.

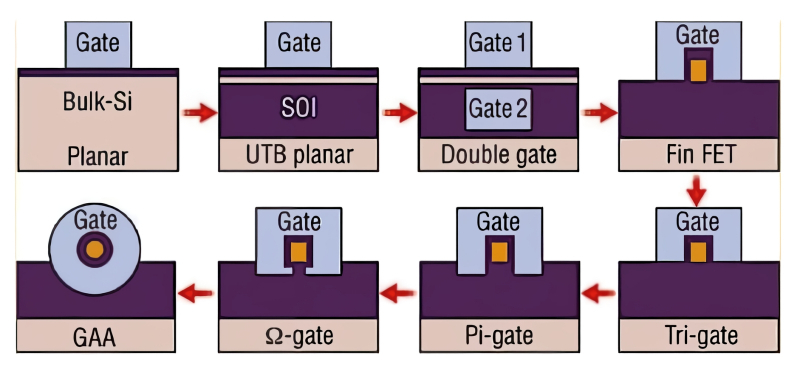

O design clássico de um transistor MOS fornece posicionamento plano, ou seja, adjacente ao mesmo plano convencional (em lados opostos dele), do canal e da porta. E embora as dimensões físicas dos elementos do transistor fossem bastante grandes em comparação com as dimensões de um único átomo – ou seja, átomos de silício e outros materiais de estrutura semelhante com escassez ou excesso de elétrons nas camadas externas, lembramos, são responsáveis para a manifestação das propriedades especiais dos semicondutores, nos quais quase toda a microeletrônica moderna – tudo era bastante simples: a miniaturização ingênua do processo de fabricação desses mesmos transistores MOS levou a um aumento no desempenho de todo o microcircuito construído sobre eles. Até porque quanto mais curto o canal, menos tempo os portadores de carga irão superá-lo, movendo-se sob a influência da diferença de potencial entre a fonte e o dreno.

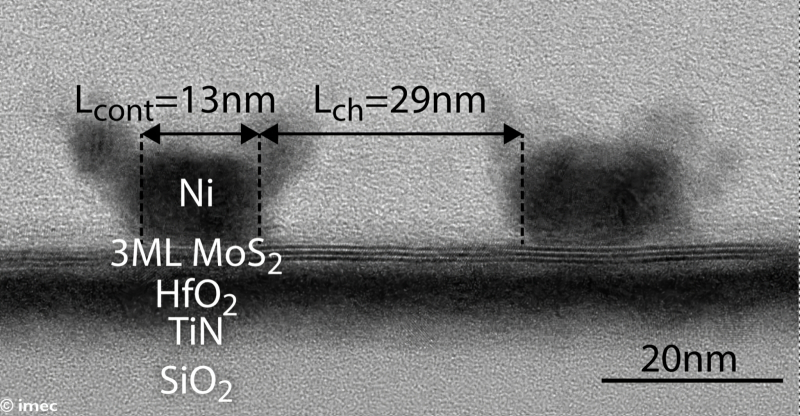

Um transistor planar baseado em um filme de três camadas de dissulfeto de molibdênio “bidimensional” (MoS2; cada camada tem literalmente uma molécula de espessura) elimina muitos dos efeitos de canal curto inerentes aos transistores de silício (fonte: IMEC)

Uma vez que o canal atinge o limite de aproximadamente 90 nm, devido às peculiaridades da implementação fotolitográfica da fonte e dreno no substrato de silício, as correntes de fuga começam a se fazer sentir visivelmente, devido às quais, mesmo com a porta formalmente fechada, um carga elétrica ainda pode passar pelo canal, mesmo que e com menos intensidade do que no estado “fechado”. Existem vários fatores conhecidos como efeitos de canal curto que ajudam a diminuir a barreira de potencial (aquela que impede a carga de fluir através do canal quando a porta está fechada) devido ao vazamento. Em particular, com uma porta ativa em torno da fonte e dreno de carga – que, no método fotolitográfico de fabricação de estruturas semicondutoras, são regiões com condutividade tipo n embutidas na base com condutividade tipo p – regiões depletadas de cargas negativas ( surgem zonas de depleção), o que efetivamente reduz o comprimento de trabalho do canal controlado por portão. E assim que as zonas esgotadas em ambos os lados do canal são fechadas, o fechamento da porta (removendo a tensão de controle dela) não leva mais à suspensão da transferência de carga através do transistor: o papel de um canal alternativo é desempenhado por aqueles mesmas regiões esgotadas conectadas. Isto acontece precisamente em um comprimento de canal de aproximadamente 25-28 nm.

Sim, em princípio, tais efeitos podem ser combatidos a nível eletroquímico, como dizem, utilizando outros materiais em vez do silício dopado com impurezas diversas, colocando uma camada isolante entre a base de silício e o próprio transistor, o que evita a formação de esgotamento zonas (método silício sobre isolador, SOI ), etc. Mas os processos tecnológicos exigidos são um pouco diferentes, especialmente no caso da produção em massa, o que ameaça aumentar o custo dos microcircuitos assim obtidos para valores absolutamente inaceitáveis.

Outro ponto extremamente desagradável: quando o comprimento do canal diminui excessivamente, a distribuição desigual dos átomos dopantes começa a se manifestar. A dopagem de um semicondutor, lembramos, é realizada com doses extremamente pequenas de impurezas – aproximadamente um ou dois átomos adicionais por dez milhões de átomos de silício – de modo que em uma seção com comprimento de 20-30 nm e largura comparável pode haver 2-3 átomos dopantes, ou talvez 5-6, o que levará a uma diferença notável nas propriedades dos transistores vizinhos no chip. Estas diferenças terão de ser compensadas aumentando a tensão de funcionamento em todo o microcircuito, o que ameaça compensar a vantagem de um processo tecnológico mais diminuto em termos de eficiência energética.

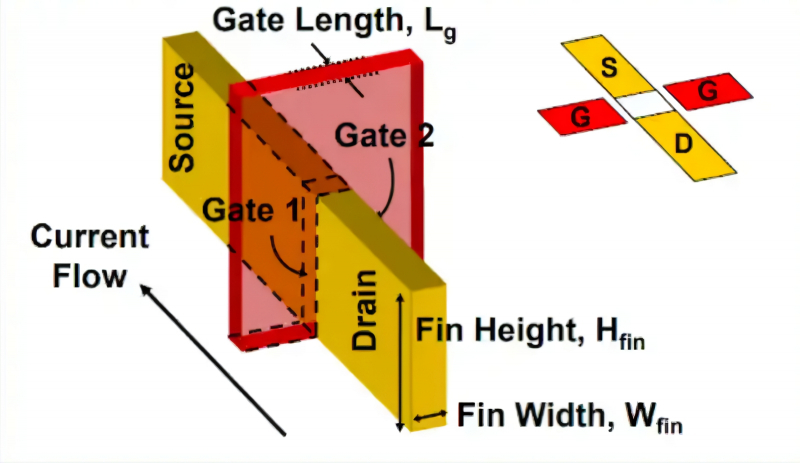

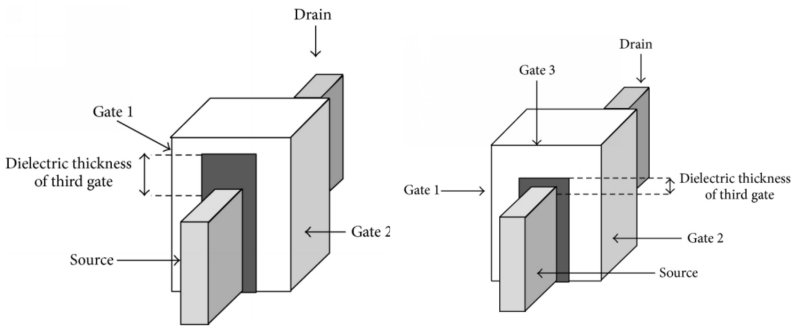

Os principais elementos de um transistor de aleta: fonte e dreno (fonte/dreno) e áreas de contato com a porta estendida devido à crista (gate1, 2) (fonte: SiliconVLSI)

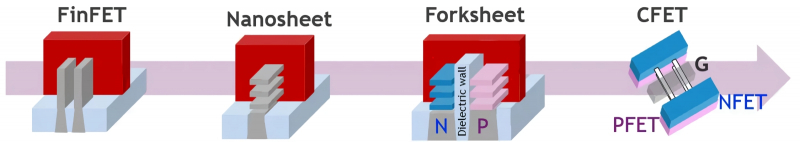

Em 2009, na próxima Developers Conference, a Intel demonstrou um wafer de silício litografado usando um processo tecnológico de “22 nm”, e os chips nele eram formados não por transistores planos clássicos, mas por transistores “fin” ou “pente” – FinFET. Ao mesmo tempo, foi afirmado que em dois anos entrariam no mercado processadores seriais criados com o mesmo princípio, e a empresa manteve sua palavra: a família de CPUs Ivy Bridge lançada em 2011 foi de fato a primeira na história da empresa a ser baseado em transistores FinFET de “três portas” ou “volumétricos”. Esses nomes figurativos – tri-gate, 3D – enfatizam a principal diferença entre o novo tipo de transistores e os planares: o canal de passagem de carga no caso do FinFET não é mais uma pequena seção de semicondutor diretamente sob o portão, mas três seções de uma vez só. Devido à nova geometria da base do semicondutor, não mais plana, mas estreita e alongada para cima (em forma, na verdade, de uma aleta ou crista), e agora cobrindo-a em três lados da porta, mais duas verticais são adicionado à seção convencionalmente horizontal anterior do canal – o mesmo estendido transversalmente, mas muito mais alongado.

Apesar da aparente simplicidade desta solução, o caminho do FinFET desde uma ideia inicial até à produção em massa acabou por ser longo. Não é por acaso que a própria Intel, em 2011, classificou a transição para transistores penteados como a mudança mais radical na tecnologia de semicondutores do último meio século. Tudo começou em 1997, quando um grupo de pesquisadores da Universidade da Califórnia em Berkeley, liderado pelos professores Chenming Hu, Jeff Bokor e Tsu-Jae King Liu, se perguntou qual a melhor maneira de superar o limite fisicamente determinado do comprimento do canal de um canal. transistor planar clássico de 25 nm, que descrevemos acima. Naquela época, lembremos, o processo técnico mais avançado utilizado comercialmente para a produção de eletrônicos fornecia detalhes de cerca de 250 nm, o que diz muito sobre a visão da famosa agência governamental americana DARPA, que apoiou esta pesquisa. Mais tarde, grandes empresas de TI como Intel, IBM, Texas Instruments, AMD, Motorola e UMC juntaram-se para trabalhar nesta área.

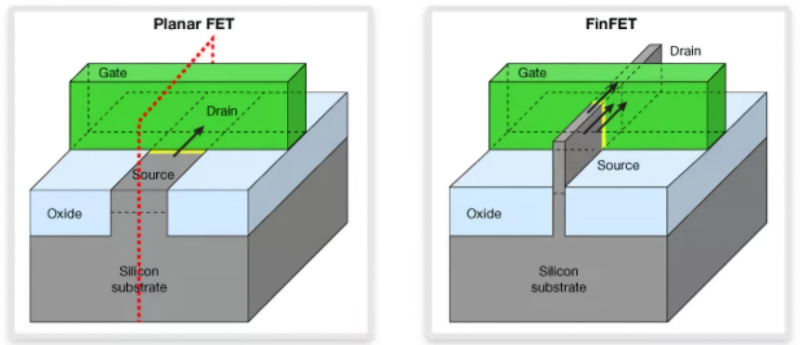

Comparação de diagramas de circuitos de transistores planares e pente (fonte: Synopsys)

Professor Hu em 1999, quando o grupo revelou o conceito geral de FinFET – para ser justo, destacamos que em 1989, Digh Hisamoto e colegas do Grupo de Pesquisa e Desenvolvimento Hitachi em Tóquio propuseram uma estrutura de transistor semicondutor de porta dupla semelhante ao FinFET ”, descreveu sua vantagem sobre um transistor planar: “Você pode fazer uma analogia com um vaso sanguíneo: se ele for danificado como resultado de uma lesão, a maneira mais eficaz de estancar o sangramento é comprimir o vaso em ambos os lados. Pressionando apenas de um lado também é possível obter um resultado, mas não é tão eficaz.” Seções longas e estreitas do canal de condução em ambos os lados da aleta do transistor pente fornecem controle significativamente melhor sobre as correntes de fuga em toda a área do tridimensional (mais precisamente, ainda plano, mas agora localizado perpendicularmente ao plano da placa da peça) canal – simplesmente porque não há literalmente nenhum lugar para os elétrons escaparem do campo elétrico do obturador na espessura da aleta estreita. Já em 2000, Berkeley fundamentou teoricamente o desempenho dos transistores FinFET até os padrões de produção de “10 nm” – e, como vemos hoje, a realidade superou visivelmente até mesmo essas estimativas ousadas de quase um quarto de século atrás.

Como a seção do semicondutor diretamente abaixo do canal do transistor pente é elevada acima da base comum de toda a estrutura, fortemente alongada e afinada, as áreas sob a fonte e dreno esgotadas de cargas negativas não têm mais o mesmo efeito destrutivo aqui que no caso de um transistor planar, e outros efeitos negativos de um canal curto parecem visivelmente mais fracos. Não é de surpreender que, na próxima década, “átomos” semicondutores do tipo FinFET tenham se tornado o padrão industrial para a organização de sistemas semicondutores: com variações mínimas, transistores com aletas foram introduzidos em sua produção por todos os fabricantes de chips do planeta que ousaram ir além. o limite de tamanho convencional de “22 nm”.

Representação visual da diferença entre um design FinFET em geral (esquerda; a espessura da camada de isolamento acima da ponta da crista é tão espessa que impede completamente a ativação da seção correspondente do canal) e TrigateFET (fonte: Universidade de Princeton)

A propósito, estritamente falando, o termo FinFET refere-se a quaisquer transistores com cristas e pelo menos duas seções de porta localizadas verticalmente. Se a espessura do isolador no topo da cumeeira for muito espessa, esse pedaço de canal horizontal estreito e específico não funcionará; em vez de um canal contínuo e quebrado em dois lugares, formam-se dois separados – e então a analogia proposta pelo professor Hu com a pinça de um vaso sanguíneo de ambos os lados revela-se completa. Em 2011, a Intel implementou em escala serial não apenas um transistor de pente, mas um de três portas – Trigate FET – uma vez que a espessura da camada isolante entre a aleta e a porta que o abraça foi mantida a mesma tanto verticalmente quanto em um estreito seção horizontal. Porém, para uma compreensão geral da essência do assunto, essa diferença não é fundamental e, portanto, entenderemos por FinFET quaisquer variedades de transistores pente com separação incompleta do “poço de potencial” (nos diagramas também indicados; a espessura do semicondutor do qual a aleta é feita) da base sobre a qual o transistor cresceu em uma instalação litográfica.

⇡#Cercado por

Como a porta no caso do FinFET cobre uma aleta fina em três lados, o vazamento de carga na espessura da crista é praticamente eliminado, o que significa que é possível reduzir as correntes que acionam o transistor sem medo de pouca diferença entre a condutividade do canal nos estados “portão fechado” e “portão aberto”. Isso, por sua vez, abre caminho para uma maior miniaturização dos processos tecnológicos: no caso de um transistor pequeno, a intensidade da corrente necessária para sua ativação é reduzida, e essa própria ativação ocorre mais rapidamente devido ao aumento da largura do canal, o que permite um significativo número de elétrons que passam por ele simultaneamente. Por esta razão, o desempenho do transistor menor de nova geração (expresso na relação entre a potência gasta em sua ativação e a vazão do canal de condução) aumenta significativamente em comparação com seu antecessor maior.

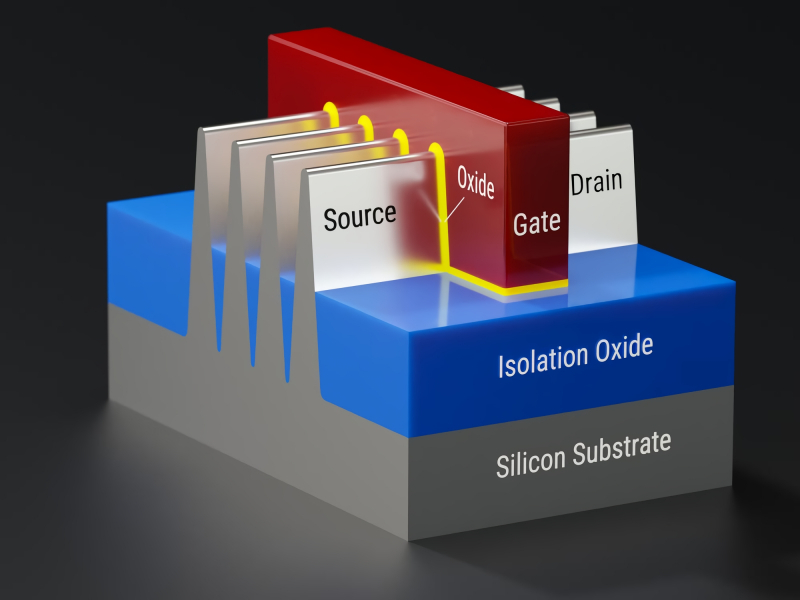

Renderização 3D de um FinFET multi-comb (fonte: Dreamstime)

A força de acionamento da porta lógica é uma característica importante de um circuito lógico que determina a rapidez com que o circuito em questão (no nosso caso, um único transistor), tendo recebido um determinado sinal de entrada, o converte em um sinal de saída. Para um padrão de produção fixo (“22 nm”, “14 nm”, etc.), o comprimento (extensão) do canal de cada transistor da fonte ao dreno é constante e, portanto, é correto dizer que quanto maior o canal largura (e para FinFET soma as alturas das duas aletas e sua espessura), melhor será o rendimento. Um transistor planar pode, relativamente falando, ser tão largo quanto desejado para aumentar seu rendimento, embora neste caso ocupe muito espaço no plano. O pente é uma questão diferente: você pode, em primeiro lugar, aumentá-lo e, em segundo lugar, cobrir várias aletas com o mesmo portão, formando assim um FinFET multi-comb.

A propósito, segue-se daqui que o rendimento desse tipo de transistor é quantizado: como a espessura do pente é muito menor que a altura, ela pode ser desprezada como uma primeira aproximação, e então a largura efetiva do multi -comb transistor (e, como consequência, o rendimento de seu canal) será diretamente proporcional à altura da aleta da unidade. A necessidade de lidar com quanta de largura de banda (bastante grande) limita a liberdade dos engenheiros de microeletrônica de equilibrar as características elétricas do chip como um todo. Isto significa, em particular, a impossibilidade de equipar alguns transistores no mesmo substrato com canais ligeiramente mais largos (para aumentar a produtividade), enquanto para outros tornar os canais apenas ligeiramente mais estreitos (para reduzir o consumo de energia): dentro do processo técnico escolhido , resta operar apenas com o número de cristas por processador, sem espaço para ajustes mais finos. Mas para estruturas FinFET semicondutoras, surgem imediatamente duas novas oportunidades para aumentar a densidade de transistores por unidade de área – além de uma redução linear nos padrões de produção devido à transição para processos técnicos cada vez mais pequenos.

Em primeiro lugar, você pode reduzir a altura das cristas (ao mesmo tempo aumentando seu número – para que o rendimento final pelo menos não diminua); em segundo lugar, pelo contrário, aumente as cristas – e ao mesmo tempo reduza o seu número por transistor (com a mesma ressalva). Hoje, o segundo método é mais utilizado, pois leva diretamente à redução da área ocupada pelos transistores individuais, ou seja, ao aumento da densidade dos elementos semicondutores por polegada quadrada. Sim, ao mesmo tempo é necessário resolver uma série de problemas de engenharia não triviais para garantir resistência mecânica suficiente de barbatanas altas e estreitas de “arranha-céus”, mas no final vale a pena.

Uma olhada na suposta evolução estritamente sequencial dos transistores semicondutores a partir de 2012 (Fonte: EEPower)

Mais precisamente, valeu a pena até muito recentemente, até que os padrões nominais de produção se aproximassem do limite inferior de vários nanômetros. Em 2020, alguns especialistas previram que em distâncias de cerca de 5 nm a abordagem FinFET perderia relevância – precisamente por causa do aumento excessivo das dificuldades na fabricação de cristas de transistores cada vez mais altas e estreitas. As dimensões máximas do menor transistor de pente duplo alcançável no nível atual de desenvolvimento tecnológico são estimadas em 5 nm para a distância entre as aletas e 15 nm para o comprimento do canal condutor. Foi assumido que, tendo passado por uma série de etapas evolutivas com convergência progressiva das pontas das portas – nomeadamente porta pi e porta ómega – os transistores MOS atingirão o estágio de anel, ou porta fechada, porta-all-around ( GAA).

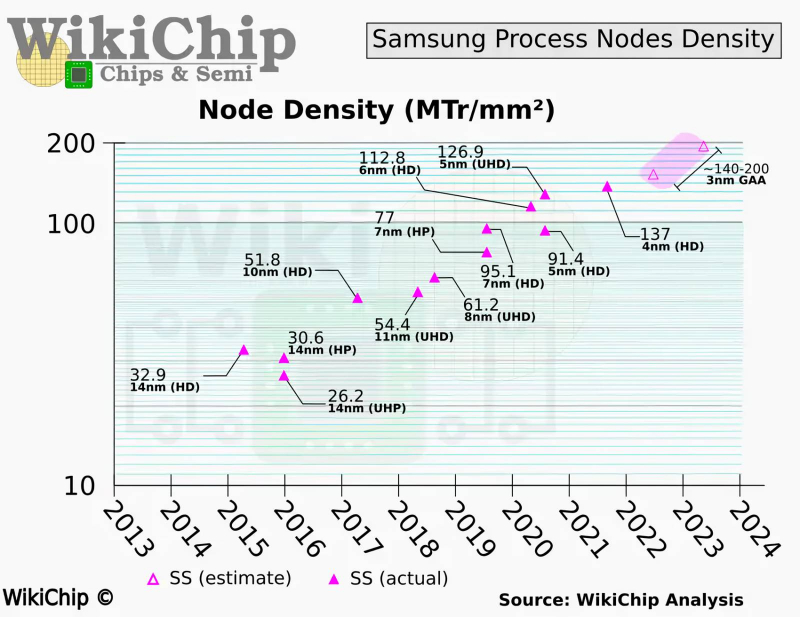

Na verdade, como já mencionado no início, os principais fabricantes de dispositivos semicondutores do mundo – com exceção apenas da Samsung Electronics (e mesmo assim, no seu caso, estamos falando de uma implementação antecipada do processo técnico, muito modestamente chamado 3GAE, ou seja, “classe 3nm gate-all-around early”) – pelo menos até 2024 eles continuarão a contar com FinFET. Sem parar, é claro, entretanto, de lembrar suas próprias implementações de GAAFET – RibbonFET, MBCFET (Multi-Bridge-Channel), transistor Nanosheet, transistor Nanowire, etc. : o investimento necessário para lançar a produção em massa de chips baseados em transistores de porta fechada é tão grande que ainda é geralmente mais sensato investir em uma maior modernização das tecnologias FinFET.

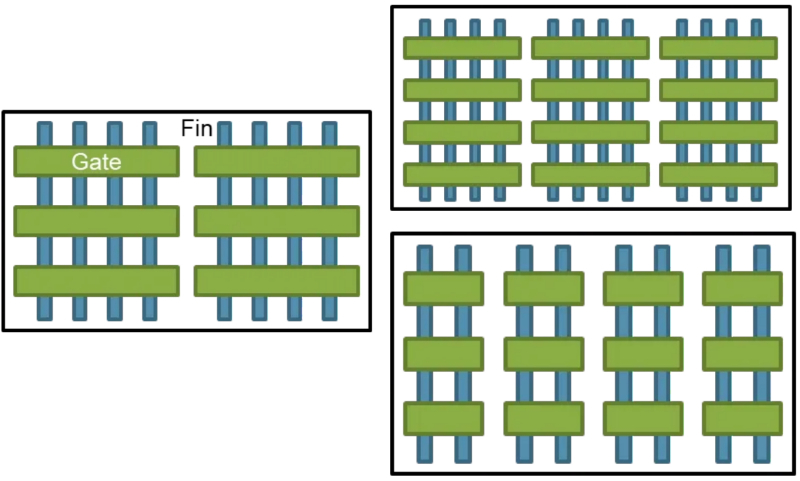

Em essência, GAAFET representa o caso extremo da estratégia de despovoamento do transistor de pente – reduzindo o número de pentes para um sem perder todas as outras propriedades úteis deste “átomo” semicondutor e, melhor ainda, melhorando-as ainda mais. O despovoamento atua como uma alternativa à redução do tamanho físico dos elementos do transistor (mudando para um processo técnico mais diminuto), embora muitas vezes – desde que o número médio de aletas por transistor disponíveis para redução permita – esses métodos para aumentar a densidade dos transistores por polegadas quadradas de um microcircuito foram usadas juntas.

Duas opções para aumentar a densidade do transistor por unidade de área: reduzir a taxa de produção (acima à direita) ou, deixando o processo igual, reduzir o número de cristas por processador (fonte: Médio)

As estruturas semicondutoras no substrato são geralmente dispostas em blocos retangulares, lembrando grades: fileiras alongadas de cristas são sobrepostas por tiras de portas, e cada transistor representa a intersecção de uma porta sólida com todas as cristas que ela cobre (há uma sutileza associada a a colocação alternada de tipos p e n-MOSFETs, mas falaremos mais sobre isso um pouco mais tarde). À medida que o processo tecnológico é reduzido, esses blocos de treliça são reduzidos proporcionalmente, de modo que um transistor ainda consistirá nas anteriores, digamos, quatro cristas por porta sólida – apenas as dimensões geométricas dessa estrutura se tornarão menores. Mas se você organizar o despovoamento corretamente – garantindo que (em particular, aumentando a altura da aleta) em vez de quatro canais, a taxa de transferência total anterior seja fornecida por dois – então você poderá dobrar o número de transistores por polegada quadrada sem alterar a taxa de produção. Física!

Além disso, ao longo de mais de dez anos de desenvolvimento ativo de tecnologias FinFET, os engenheiros propuseram várias maneiras de aumentar o rendimento de transistores multicomb sem despovoamento – além do trivial (e bastante difícil de implementar, aliás) esticando as nadadeiras verticalmente. Estas incluem a busca de novos materiais e/ou aditivos para a porta, fonte/dreno e camada isolante na base de toda a estrutura do transistor, reduzindo a espessura das cristas dielétricas que isolam o material da porta, etc. a miniaturização física dos elementos do transistor tornou-se essencialmente o último recurso, ao qual se recorre apenas nos casos mais extremos: quando é hora de salvar a lei de Moore (e de fato, lembremos, uma profecia autorrealizável), mas avanços em outras áreas de pesquisa ainda não podem ser feitas.

O desenvolvimento lógico de FinFETs multi-comb está gradualmente se tornando GAAFETs (fonte: Medium)

Porém, não importa como você torça a corda, haverá um fim: por volta do início da década de 2020, ficou claro que o despovoamento como forma mais importante de aumentar a densidade dos transistores está saindo de cena – simplesmente porque a esmagadora maioria dos eles já eram apenas pentes duplos. Resta espaço para o único passo decisivo – um retorno ao circuito “uma aleta – um transistor”, que é frequentemente usado para explicar a essência da tecnologia FinFET, mas que inicialmente, embora uma ênfase consciente fosse colocada no multi-comb, foi não de natureza aplicada, mas puramente ilustrativa. É aqui que entra o GAAFET – um repensar radical da morfologia de uma única aleta, visando a transição da produção de semicondutores de uma saída formal para a terceira dimensão (quando o canal através do qual as cargas elétricas se movem no transistor ainda permanece plano – ele apenas estica e dobra) para submeter o desenvolvimento do espaço acima do plano da peça de silício, no qual as estruturas semicondutoras são criadas usando o método fotolitográfico.

A essência da tecnologia GAAFET é que agora cada aleta é cortada horizontalmente em longas barras que passam pela espessura do material da veneziana, uma acima da outra. Um elemento separado do canal do transistor torna-se assim o limite interno fechado entre um dos fragmentos da aleta (que ainda possui uma fonte de carga em um lado da extremidade e um dreno no outro) e a espessura da porta perfurada por ele. Ao colocar as vigas com bastante frequência e firmeza (fitas, fios, folhas – os nomes das “marcas” mudam dependendo da imaginação de um desenvolvedor específico), é perfeitamente possível garantir que a largura total do novo canal exceda a de um único – pente a estrutura FinFET dessas mesmas dimensões geométricas.

Uma seção transversal de protótipos de engenharia de transistores RibbonFET com quatro portas fechadas por crista – é exatamente assim que eles devem ficar após a fabricação usando o processo técnico “Intel 20A”, que ainda não foi levado ao estágio de produção (fonte: Intel)

É claro que quanto maior o número de vigas nas quais cada aleta é cortada, e quanto mais firmemente elas são empilhadas umas sobre as outras, mais complexo será o projeto final na produção. O salto no nível de complexidade dos problemas puramente de engenharia aqui é tão impressionante que a abordagem GAAFET, proposta quase simultaneamente com o FinFET, levou cerca de uma dúzia de anos para passar para sua primeira implementação serial (por enquanto – apenas nas instalações da Samsung Electronics, que foi discutido no início). Basta dizer que onde a formação de uma aleta contínua requer um ciclo de operações (aplicação de fotorresiste a um substrato de silício → exposição através de uma fotomatriz → lavagem da camada protetora sobre as áreas destinadas à remoção → gravação → aplicação de uma camada isolante), a estrutura GAAFET necessita de um número múltiplo de etapas, pois após criar a base para uma futura pilha vertical de barras, será necessário aplicar uma camada “sacrificial”, resistente aos procedimentos de iluminação/gravura, e repetir este procedimento após a formação de cada barra seguinte e, finalmente, remova as camadas “sacrificiais” e, em seguida, substitua-as por material de veneziana.

⇡#Adição importante

É intuitivamente claro que a transição de FinFETs de pente duplo para GAAFETs, mantendo todos os outros parâmetros de formação de estruturas semicondutoras (e, acima de tudo, a norma tecnológica), permitirá que os fabricantes de chips dobrem imediatamente a densidade de transistores por polegada quadrada “ de graça”. Entre aspas – porque os custos para a realização de todos os procedimentos adicionais necessários serão, sem dúvida, extremamente elevados – presumivelmente, é por esta razão que nem a Intel nem a TSMC têm pressa em despovoar os seus transistores para aletas únicas. E, no entanto, um dia – e provavelmente mais cedo ou mais tarde – chegará o momento em que as estruturas do GAAFET terão de ser transferidas para o próximo nível de miniaturização. Se levarmos em conta o aumento múltiplo no número de etapas de produção necessárias, esse prazer definitivamente não será barato, e definitivamente não será possível ir indefinidamente para a região das unidades de angstroms: os comprimentos dos canais dos transistores começarão a ser medido em alguns átomos, o que não nos permitirá mais ignorar os efeitos quânticos extremamente desagradáveis para os sistemas de computação de Von Neumann no nível dos transistores individuais. E então o que? O fim do progresso?

Uma explicação clara de por que exatamente a Samsung Electronics tem tanta pressa em implementar o GAAFET: devido à nova tecnologia, a densidade dos transistores em um ou dois anos promete quase dobrar em comparação ao limite alcançado no final de 2022 com a tecnologia FinFET ( fonte: WikiChip)

De forma alguma: assim como no final do século 20, os desenvolvedores já estavam pensando em protótipos do próximo FinFET, hoje o trabalho está a todo vapor na próxima tecnologia de organização de transistores depois do GAAFET (e, portanto, ainda muito distante em termos de implementação prática) – FET complementares (CFET). Essas estruturas são chamadas de “adicionais” porque aqui não haverá mais uma aleta por transistor MOS, mas dentro de uma aleta (mais precisamente, que manteve seu contorno geral de estrutura vertical) vários transistores separados estarão localizados ao mesmo tempo, e não apenas MOS, mas CMOS – o que são, como já mencionamos, feixes complementares (mutuamente complementares) de transistores construídos em canais com condutividade eletrônica e de furo: n-MOS e p-MOS.

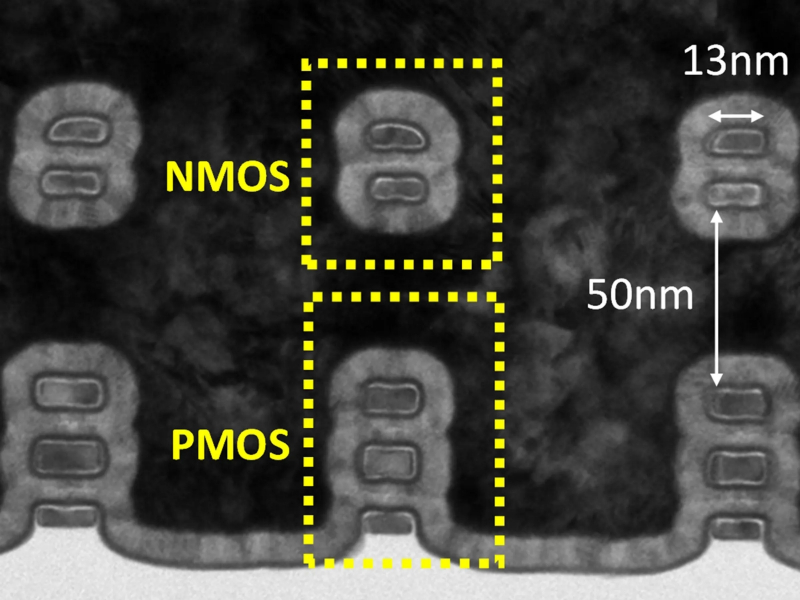

Lembremos que os transistores n-MOS são chamados de diretos (eles abrem quando a tensão é aplicada à porta), e os transistores p-MOS são chamados de inversos (pelo contrário, eles abrem quando a tensão é removida da porta). Complementaridade – complementaridade – manifestam-se no fato de o transistor MOS inverso ser projetado de forma oposta ao direto: a base do p-MOS é formada por um semicondutor tipo n, a fonte e o dreno formam p -inclusões do tipo, e em vez de condutividade eletrônica, forma-se condutividade de buraco no canal aberto, enquanto para n-MOS o oposto é verdadeiro. A abordagem FinFET, em particular, implica que cristas alternadas do tipo p e n (mais precisamente, conjuntos de aletas – afinal, não estamos falando de GAAFETs de aleta única) são sobrepostas pela mesma porta, o que permite dois transistores adjacentes com um dispositivo complementar para formar um par que funcione eficientemente. Nesse caso, eles não interferem entre si, pois a princípio não podem atuar simultaneamente – se a tensão de operação for aplicada à porta, o transistor n-MOS está aberto e o p-MOS está fechado, e vice-versa.

Transistores n-MOS e p-MOS formam pares complementares em cristas CFET (fonte: Intel)

Portanto, o princípio fundamental do CFET é que, acima da base do futuro microcircuito, pares complementares de transistores n-MOS/p-MOS com portas fechadas estão localizados um acima do outro – olá, GAAFET! Novamente, parece completamente lógico, e nos diagramas explicativos parece inteligível – as diferenças em relação ao estágio anterior de evolução do transistor são mínimas: as mesmas barras passando pela espessura do obturador alongado verticalmente, apenas em cores diferentes. No entanto, se a tecnologia GAAFET já é extremamente difícil de implementar do ponto de vista da engenharia, então o CFET a este respeito aumenta as apostas numa ordem de grandeza: colocar pares de transístores complementares um acima do outro é incrivelmente mais difícil do que no mesmo plano. Há uma enorme diferença aplicada entre os transistores n-MOS e p-MOS em termos de implementação de engenharia: eles requerem metais diferentes, aditivos diferentes nas seções semicondutoras e até mesmo os contatos para conectá-los aos circuitos lógicos devem ser colocados à sua maneira. .

E a própria tecnologia para produção em fluxo de transistores CFET precisa ser desenvolvida quase do zero. O fato é que todos os esforços anteriores dos pesquisadores nesse sentido, não excluindo o método de obtenção de estruturas GAAFET, concentraram-se na moldagem seletiva de estruturas verticais individuais com o mesmo tipo de conteúdo, seja um pente FinFET sólido ou barras GAA dispostas em um escada. No caso dos CFETs, é necessário formar seletivamente estruturas heterogêneas – as mesmas barras, mas com condutividade n ou p – dentro da mesma vertical.

Embora o passo do metal mude pouco após a mudança para CFETs, espera-se que a espessura das portas dentro dos transistores CMOS embalados verticalmente atinja o nível atômico até 2036 (fonte: IMEC)

Até muito recentemente, a fotolitografia semicondutora desenvolveu-se, essencialmente, dentro de um único plano com estruturas individuais “alongadas” verticalmente – e aqui os engenheiros alcançaram alturas incríveis (na época da primeira menção teórica do FinFET). A fotolitografia verdadeiramente tridimensional, destinada a criar estruturas semicondutoras subminiaturas heterogêneas em volume, está apenas em sua infância, portanto, é improvável que o caminho para dominar a produção em série de microcircuitos com transistores CFET leve menos de uma década.

No mínimo, as estimativas conservadoras dos analistas do IMEC apontam para 2032, e não antes. É bem possível que o elo intermediário entre GAAFET e CFET seja a tecnologia Forksheet FET proposta pela Intel como conceito em 2019, que envolve colocar altas pilhas de barras isoladas com condutividade n e p próximas umas das outras, mas com uma parede dielétrica dielétrica vertical entre eles – e de modo que sejam cobertos por uma única veneziana. Não há diferença fundamental com a abordagem GAA, no entanto, um arranjo mais denso dos elementos complementares que compõem os transistores permitirá, como esperam os engenheiros, desenvolver melhor as tecnologias necessárias para estabelecer a produção de CFET em streaming.

Perspectiva de evolução das estruturas semicondutoras na próxima década (fonte: IMEC)

O mais interessante é que até agora os especialistas na área de tecnologias de semicondutores não podem dizer com certeza o que acontecerá após o CFET – além dos padrões de produção de um 1 angstrom convencional. O bom e velho silício com todos os tipos de aditivos será substituído por nanotubos de carbono? Talvez haja um avanço fundamental no campo da fotônica e os semicondutores, em princípio, desapareçam de cena? Surpreendentemente, no final da década de 1980 era perfeitamente possível olhar para as tecnologias avançadas da década de 2020, mas hoje fazer uma previsão informada para “apenas” uma década parece ser uma tarefa extremamente difícil. Tal é o ritmo actual do progresso tecnológico – a incerteza no intervalo de apenas alguns anos é demasiado grande. Será ainda mais interessante quando surgir pelo menos alguma certeza. Os engenheiros microeletrônicos certamente não ficarão entediados no futuro próximo!