O material anterior sobre calibração de padrões tecnológicos na produção de microprocessadores trouxe, gostaria de acreditar, alguma clareza sobre o porquê dos nomes dos processos de produção “22 nm”, “10 nm”, “7 nm” não correspondem diretamente às características dimensionais físicas das estruturas semicondutoras ativas, na verdade formadas por máquinas litográficas nos chips correspondentes.

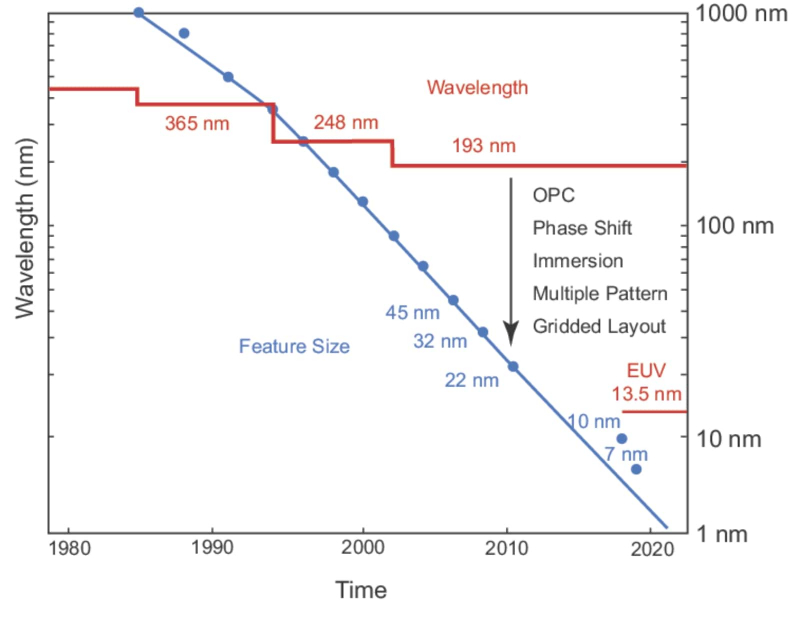

Obviamente, o comprimento real de um transistor típico formado em uma pastilha de silício excede significativamente o tamanho indicado no nome de marketing de qualquer processo técnico moderno. Mas ainda assim, esse valor é significativamente menor que o comprimento de onda do laser de trabalho na máquina de litografia DUV – 193 nm. Então, de alguma forma, engenheiros de microeletrônica conseguem criar elementos semicondutores com dimensões características de dezenas e até unidades de nanômetros usando uma ferramenta tão indelicada. Deve-se notar que os padrões de produção em série até “7 nm” nas fábricas de fabricantes de chips hoje usam máquinas DUV, e somente a partir desta marca o patrimônio de unidades EUV se estende para baixo.

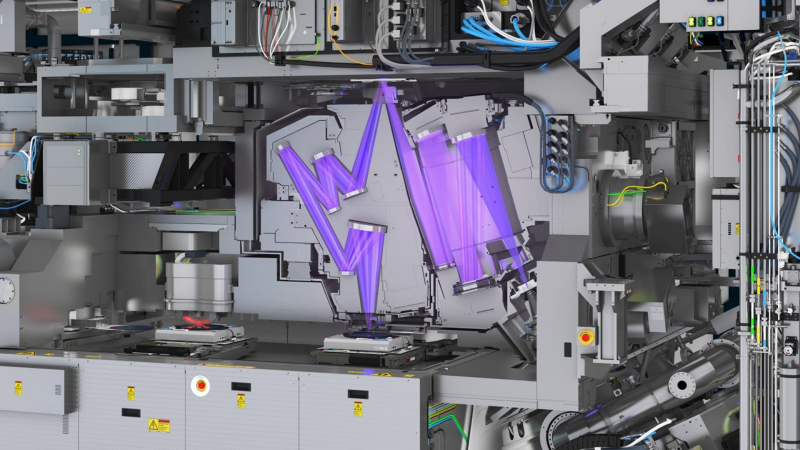

Primeiro, a microeletrônica é simplesmente linda. (Fonte: Taiwan Semiconductor Manufacturing Co., Ltd.)

⇡#Mais profundo!

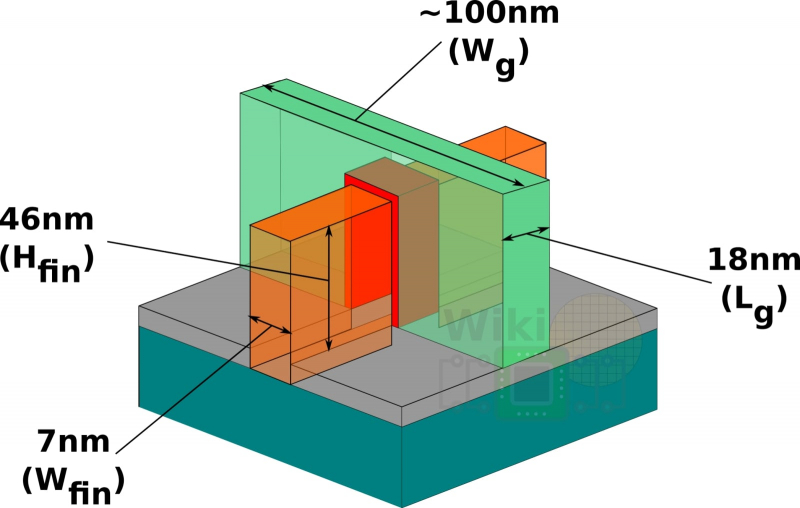

Vale a pena começar pelo fato de que nem todas as dimensões dos elementos estruturais VLSI são igualmente significativas. De fato, a largura mínima da crista do transistor FinFET, feita de acordo com o padrão de produção TSMC “7 nm”, é próxima de 6 nm e comparável a ela em miniatura Intel “10 nm”, a 7 nm. Mas, em si, esse valor não é fundamentalmente importante: do ponto de vista da lei de Moore – o aumento progressivo da densidade de transistores por polegada quadrada – a distância entre os elementos semicondutores básicos, na terminologia inglesa, o pitch é de suma importância.

As principais dimensões características do transistor Intel “10-nm”: altura do cume (Hfin) – 46 nm, largura do cume (Wfin) – 7 nm, espessura do portão (Lg) – 18 nm (fonte: WikiChip)

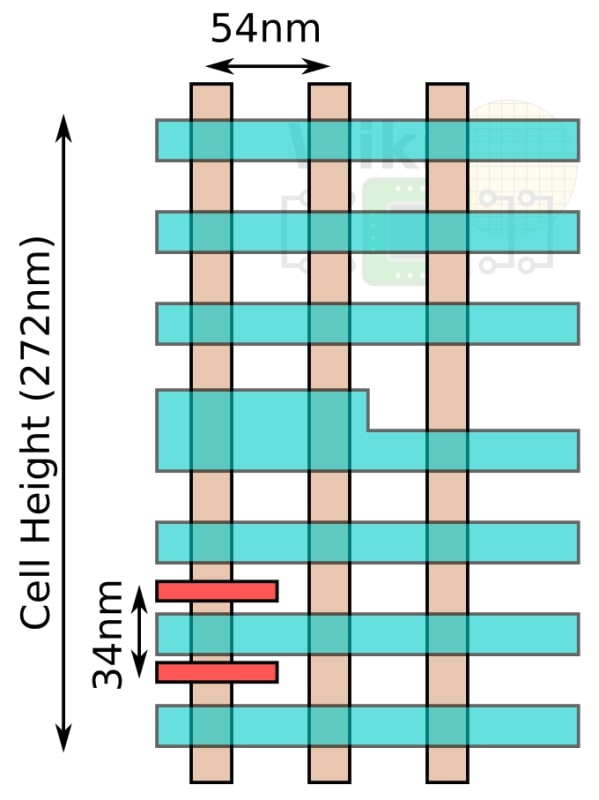

Assim, para a tecnologia de processo Intel “10 nm”, a distância entre as cristas adjacentes (fin pitch) chega a 34 nm. Um pouco menor é o comprimento do intervalo entre as cristas semicondutoras para a norma de produção Intel 4 (nee “Intel 7 nm”), 30 nm. E todo esse esplendor incrivelmente em miniatura é realizado usando fotolitografias DUV, cuja principal ferramenta de trabalho é um laser com comprimento de onda de 193 nm.

A célula de fabricação básica, dentro da qual a máquina litográfica DUV forma estruturas semicondutoras usando o processo de 10 nm da Intel com um intervalo de 34 nm entre pentes de transistor (mostrados em vermelho), se estende até 272 nm. Os portões são destacados em terracota (a distância entre os adjacentes é de 54 nm), água-marinha são as interconexões metálicas da camada mais baixa (separadas por 40 nm) (fonte: WikiChip)

Enquanto isso, o ultravioleta ultra-duro ou extremo (EUV, comprimento de onda de 13,5 nm) se destaca apenas começando com os padrões de produção de marketing de “7 nm” nas fábricas da Samsung e “5 nm” no caso do TSMC, além disso, o o fornecimento dos fabricantes de chips ASML holandeses das máquinas litográficas correspondentes começou apenas em 2019. O fato é que a maneira mais aparentemente óbvia de miniaturizar o processo técnico – instalar uma fonte de luz de comprimento de onda ainda mais curto na litografia – é muito mais difícil do ponto de vista da implementação técnica do que a melhoria consistente da máquina DUV, continuada com sucesso por décadas.

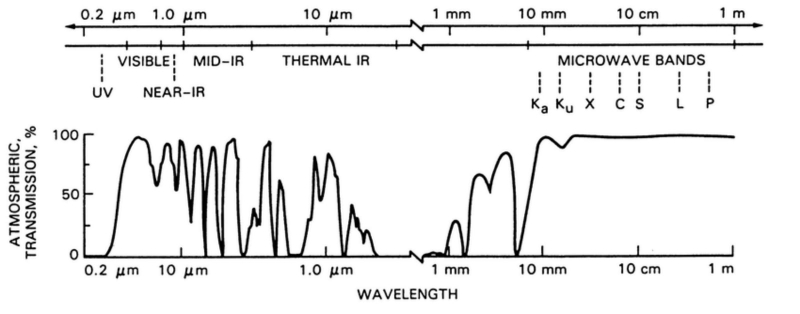

A tecnologia DUV mostrou-se extremamente bem-sucedida para a fabricação de microprocessadores, pois toda radiação com comprimento de onda menor que ~200 nm é rapidamente absorvida sem resíduos, mesmo pelo ar atmosférico, sem falar no vidro óptico. Os fótons de energias tão altas interagem muito ativamente com quase todos os meios pelos quais passam – é isso que leva à sua rápida absorção. Deve-se notar que mesmo nos primeiros anos do século 21, os engenheiros tentaram usar um laser de flúor molecular de 157 nm para fotolitografia, mas até agora não conseguiram levar essa tecnologia ao estágio de aplicação comercial.

«Janelas de transparência” da atmosfera terrestre para radiação em diferentes comprimentos de onda, de UV a rádio. Você pode ver uma queda acentuada na taxa de transferência de 0,2 mícrons (200 nm) – ondas mais curtas não podem mais passar pelo ar (fonte: INPE)

As máquinas EUV que todo mundo ouve falar hoje dependem de radiação UV tão curta que é, de fato, um raio-X suave: se o ar atmosférico a absorve efetivamente, o vidro óptico ainda mais. Portanto, em vez de um esquema óptico refrator (transmissor), as máquinas EUV usam um reflexo (refletor) – com muitos espelhos de foco multicamadas de formato complexo, feitos com incrível precisão e colocados em uma câmara de vácuo.

Cada uma das camadas alternadas de molibdênio e silício na composição de tal espelho tem uma espessura de cerca de 3,4 nm (um quarto do comprimento de onda da radiação de trabalho). Por que isso é assim, ainda não consideraremos em profundidade (para quem estiver interessado, mencionaremos a lei de Bragg), – é importante aqui que a fabricação, instalação e ajuste de apenas um sistema de espelhos para uma fotolitografia seja incrivelmente procedimento complexo e caro.

Diagrama de transmissão de radiação de 13,5 nm em um sistema evacuado de espelhos dentro de uma fotolitografia EUV comercial (fonte: ASML)

Não é à toa que a ASML holandesa, a única fabricante mundial de máquinas EUV, estima cada uma delas em 200 milhões de dólares americanos (para comparação: suas fotolitografias DUV custam aos clientes apenas 40-60 milhões de dólares por peça). E enquanto a maior parte dos chips modernos do mundo são produzidos em equipamentos DUV, faz sentido descobrir como exatamente ele, embora no limite de suas capacidades, ainda consegue formar estruturas de silício com o tamanho máximo característico fisicamente alcançável de 6- 7nm.

Até o momento, muitos desses métodos foram desenvolvidos – e, a propósito, alguns deles também encontraram aplicação em equipamentos EUV, o que permite que essa tecnologia explore com confiança horizontes de escala de unidades de angstroms no futuro. Esses métodos estão agrupados em dois grandes blocos: aqueles que melhoram as capacidades das máquinas litográficas na área desde a fonte de luz até seu contato com o fotorresistente (óptico) e depois (engenharia e tecnológica). Vamos começar com a óptica – e primeiro vamos descobrir exatamente como uma imagem em nanoescala é formada em uma camada fotorresistente; quais são os limites físicos da sua miniaturização ao nível do sistema óptico.

⇡#Lançando luz

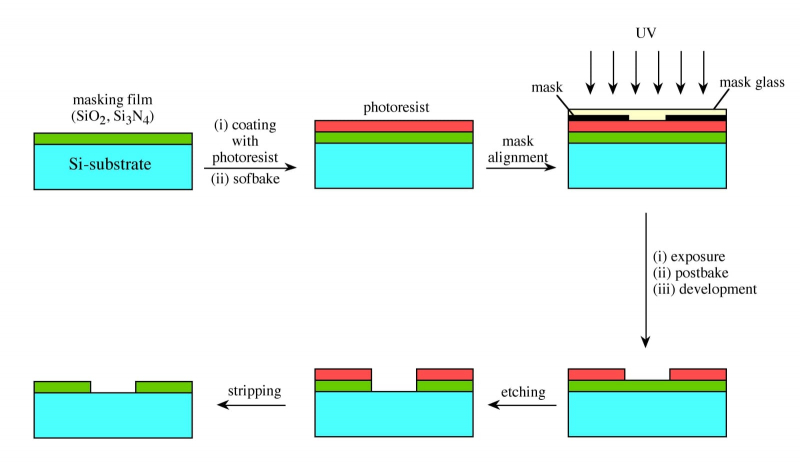

O processo de fotolitografia consiste no fato de que uma camada de material sensível à luz (fotorresistente) é aplicada na superfície de um wafer de silício, então essa camada é exposta a um fluxo de luz que passa por uma máscara (fotomáscara) – desenhando a estrutura do um futuro circuito eletrônico. As máscaras de hoje são muito maiores (em escala) do que as estruturas semicondutoras de silício finais – então a iluminação é produzida através de um sistema de lentes redutoras.

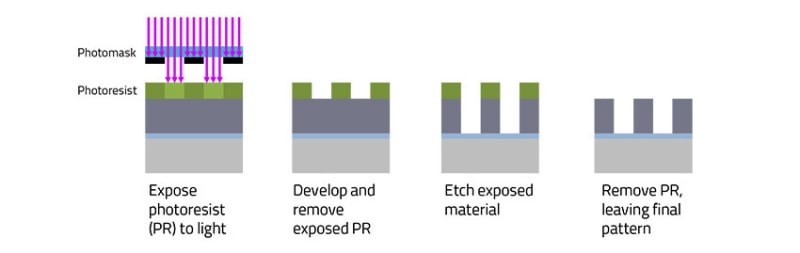

As principais etapas do processo fotolitográfico (para simplificar, na ausência de lentes): aplicar uma base dielétrica (filme de máscara) a um substrato semicondutor (Si), revestir a base com um fotorresistente, instalar uma máscara, exposição, revelação, gravação (gravação) de áreas abertas do dielétrico e lavagem (remoção) do resíduo fotorresistente (fonte: OpenStax)

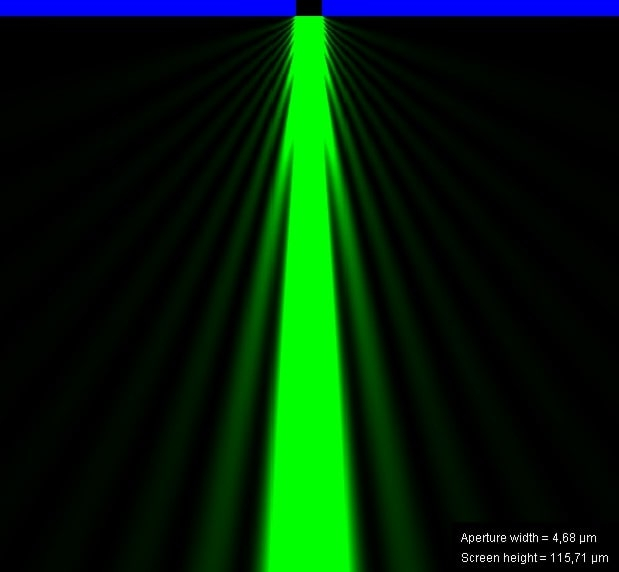

Mesmo se deixarmos de lado as próprias lentes por enquanto (e ao mesmo tempo os problemas associados a elas que degradam a qualidade da imagem, como aberrações, retroespalhamento, absorção do fluxo de luz na espessura do vidro, etc.) , a exposição do fotorresiste através de uma máscara com orifícios microscópicos é tarefa extremamente difícil devido ao fenômeno de difração.

A luz que passa pela fenda inevitavelmente se espalha devido à sua natureza dualista de onda-partícula, de modo que a imagem no alvo (no fotorresistente) fica um pouco borrada nas bordas. Mas se a fenda é tão pequena que os padrões de difração de suas bordas realmente se tocam, ou mesmo se sobrepõem, nenhuma imagem nítida pode ser obtida na camada fotorresistente.

Difração da luz passando por um buraco que encolhe de 4,69 µm para 194 nm (Fonte: Wikimedia Commons)

Acontece que é impossível obter elementos menores de futuros transistores no substrato exposto devido à miniaturização das fendas apenas na fotomáscara. A escala mínima permitida de uma imagem claramente distinguível após a passagem da luz através de uma fenda estreita determina o chamado. limite de difração.

O comprimento de onda da radiação usada para expor a fenda (λ), a característica integral do sistema óptico utilizado (sua abertura numérica, NA) e a resolução do mesmo sistema óptico – ou seja, a escala real mínima de detalhe do imagem (dimensão crítica, CD) – estão sujeitos à seguinte lei especificada:

CD = k*(λ/NA)

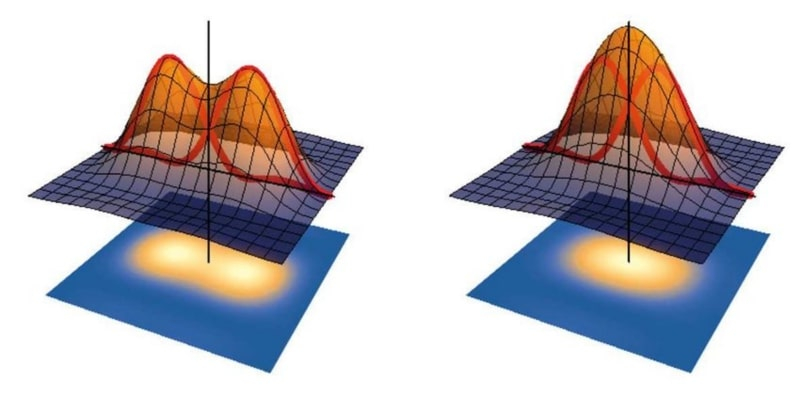

«É chamado de refinado “porque na maioria das vezes em óptica aplicada, especialmente em microscopia, o coeficiente adimensional k é assumido como 0,61 – então uma fórmula é obtida para determinar o tamanho mínimo de um objeto que um sistema óptico pode exibir com confiança: o critério de Rayleigh . No caso geral, entretanto, k depende de maneira bastante complexa da abertura do sistema óptico.

Representação gráfica do critério Rayleigh distinguindo com confiança (esquerda) e mesclando (direita) picos de intensidade de luz vizinhos (fonte: European Physical Journal Plus)

A lei refinada da resolução limitante, também chamada de fórmula principal da litografia óptica, aponta claramente para possíveis maneiras de miniaturizar os processos de produção na indústria de semicondutores. Para minimizar a escala CD, deve-se reduzir o comprimento de onda de radiação λ (e é por isso que, em cada nova geração de máquinas de fabricação de chips, ele vai cada vez mais para o ultravioleta distante), ou aumentar a abertura NA, ou fazer as duas coisas no mesmo tempo. É verdade, uma vez que k ainda depende de NA – ou seja, diminui não linearmente de 0,61 para 0,50 com um aumento na abertura de 0 para 1 – isso deve ser levado em consideração, não assumindo que um aumento de NA seja compensado por uma diminuição tinta.

De uma forma ou de outra, em máquinas fotolitográficas reais, a escala máxima de detalhe atingível da imagem final acaba sendo proporcional ao comprimento de onda da radiação usada para iluminação do fotorresistente com um coeficiente de aproximadamente 0,5. Na década de 1970, as máquinas fotolitográficas usavam lâmpadas de mercúrio de alta pressão (aproximadamente 350-470 nm de comprimento de onda operacional), lentes com uma abertura de 0,16 e k de cerca de unidade, produzindo VLSI com o tamanho mínimo alcançável de elementos funcionais de cerca de 2,7 mícrons. – isto é, 2700 nm. E desde que a escala de detalhes na superfície do chip fosse obviamente maior que o comprimento de onda do emissor da máquina fotolitográfica, não havia problemas particulares.

O uso de fontes de luz de comprimento de onda cada vez menor (gráfico vermelho) começou a dar uma contribuição visivelmente menor aos padrões tecnológicos dominados pelos fabricantes de chips (gráfico azul) na segunda metade da década de 1990, e consideraremos todas as ferramentas de miniaturização usadas para isso. processo abaixo: são correção de proximidade óptica, máscaras de deslocamento de fase, litografia imersiva e multipass (fonte: Newport Corporation)

No entanto, já em meados da década de 1990, esses dois valores se aproximaram pela primeira vez e, em seguida, a escala de detalhes começou a se mostrar repetidamente (uma geração de tecnologias após a outra) cada vez menor que o comprimento de onda do trabalho. radiação – primeiro lâmpadas de arco e, em seguida, lasers de fluoreto de criptônio (248 nm). Em 2004, surgiram as primeiras máquinas DUV, contando com lasers de excimer argônio-fluoreto com comprimento de onda de 193 nm – foi então que a escala de detalhes geralmente aceita em cristais semicondutores (meia lacuna entre estruturas de silício adjacentes na superfície do chip, metade -pitch) atingiu primeiro 65 nm – e, portanto, acabou sendo menos da metade do comprimento de onda da radiação aplicada. Nesse ponto, as possibilidades da fórmula principal da litografia óptica pareciam esgotadas.

⇡#Fluido, máscaras, mudança

No entanto, mais ou menos nessa época, os fabricantes de chips começaram a introduzir ativamente melhorias no caminho óptico de seus processos técnicos, projetados para contornar a lei refinada da resolução máxima. E para começar… apenas adicionei água.

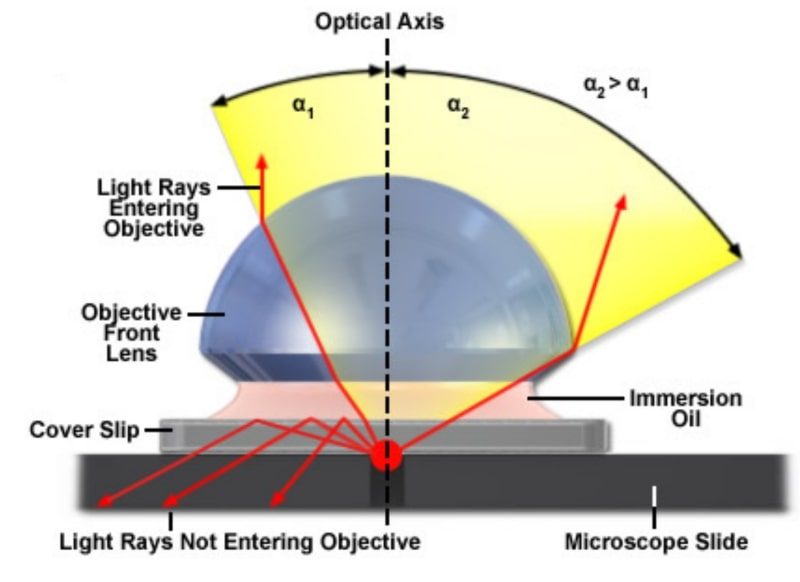

Comparação do caminho do feixe em um microscópio convencional (esquerda) e de imersão: você pode ver que o feixe que passa pelo meio líquido é mais desviado, o que corresponde a um aumento na abertura (fonte: Florida State University)

A abertura do sistema óptico NA mencionado acima é determinada pelo índice de refração do meio que transmite luz, n, e o ângulo de meia abertura do fluxo de luz que entra na lente, α:

NA = n * sin α

Как видно, чем выше n, тем больше апертура. Сравнительно простой способ увеличить n — погрузить (англ. immerse, отсюда иммерсионная фотолитография) нижнюю линзу микроскопа и образец в жидкость, обладающую бóльшим показателем преломления, чем атмосферный воздух при нормальных условиях (т. е. с n > 1,0).

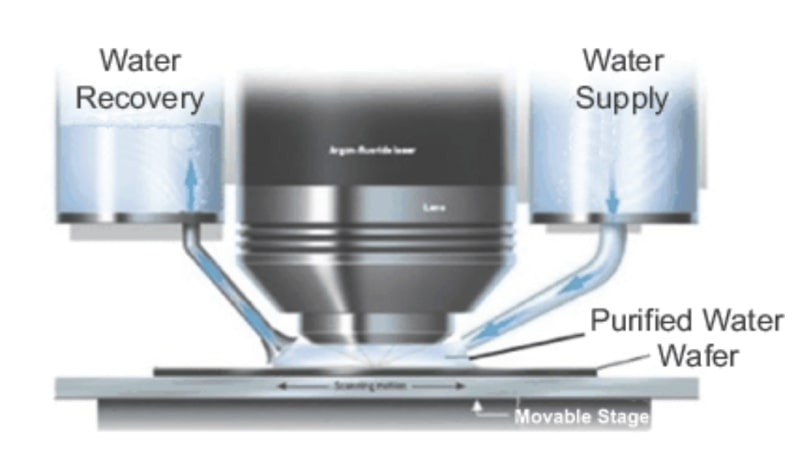

A fotolitografia de imersão usa água altamente purificada, que também é completamente deionizada (fonte: Newport Corporation)

Na maioria das vezes, na litografia por imersão, a água mais comum é usada – claro, livre de todos os tipos de impurezas e até íons – com n ≈ 1,4 (para radiação com comprimento de onda de cerca de 200 nm), mas em princípio é possível use líquidos especiais com um índice de refração ainda maior. Embora, lembre-se, a radiação de comprimento de onda curto em um meio mais denso será absorvida muito mais fortemente, então simplesmente derramar óleo mineral com n ≈ 1,6 na fotolitografia, que é usado em microscópios de imersão para pesquisa biológica, por exemplo, não funcionará: você terá que aumentar a potência da fonte de laser, desviar calor adicional das lentes, para combater sua expansão térmica, etc.

Aumentar a abertura NA permite reduzir a escala de detalhes, mas ainda não drasticamente. Além disso, a difração distorce o fluxo de luz que passa pelas ranhuras da máscara da máquina litográfica, devido ao qual a imagem formada no fotorresistente é inevitavelmente borrada nas bordas. Isso é especialmente irritante se as dimensões da imagem forem dezenas de nanômetros: passando por uma ranhura estritamente retangular na máscara, a luz do laser DUV atinge o fotorresistente, infelizmente, na forma de uma oval perdendo nitidez em direção às bordas.

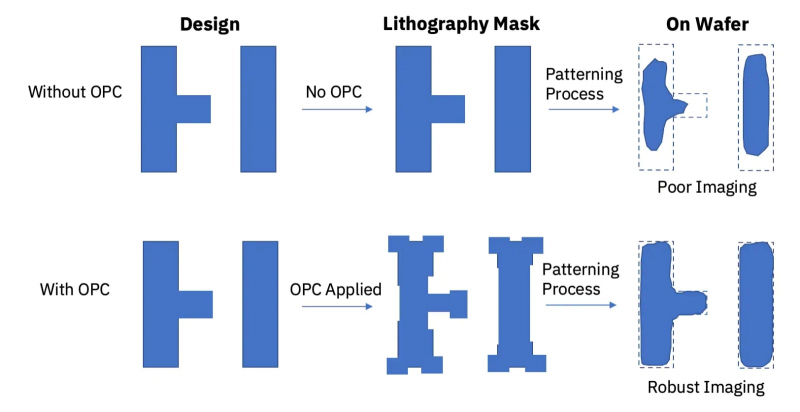

No entanto, a difração é um fenômeno que obedece a leis matemáticas, o que significa que também pode ser usada na direção oposta, guiada pelo conhecido princípio “quem nos atrapalhar nos ajudará”. É bastante realista não apenas para uma fenda retangular, mas também para uma fenda arbitrariamente complexa resolver o problema inverso: qual deve ser o tamanho da fenda realmente cortada na máscara para que, após a passagem do feixe de laser através dela e através do todo o sistema óptico da litografia de imersão, a forma inicialmente desejada seria exibida no fotorresistente?

A correção de proximidade óptica permite, tendo calculado previamente o perfil de fenda desejado, obter uma imagem litografada muito mais nítida (fonte: IBM)

Tal tarefa é chamada de correção de proximidade óptica (OPC), e embora um poder computacional bastante significativo esteja envolvido em sua solução em cada caso específico, o jogo aqui definitivamente vale a pena. É verdade que a situação é complicada pelo fato de que a difração na fotomáscara para a fabricação do VLSI moderno é múltipla: não um, nem dois, mas milhões, se não bilhões de minúsculos orifícios estão lotados nele.

Sob essas condições, a resolução realmente alcançável acaba sendo ainda menor do que a fórmula principal da litografia óptica permite – mesmo levando em consideração o OPC. E tudo porque os padrões de interferência de fendas próximas muitas vezes se sobrepõem sem sucesso (na amplitude máxima de uma onda há um mínimo da vizinha), que o contraste da frente de onda no nível do fotorresistente cai drasticamente. E, como resultado, a estrutura fina das fendas cortadas na máscara simplesmente não é reproduzida.

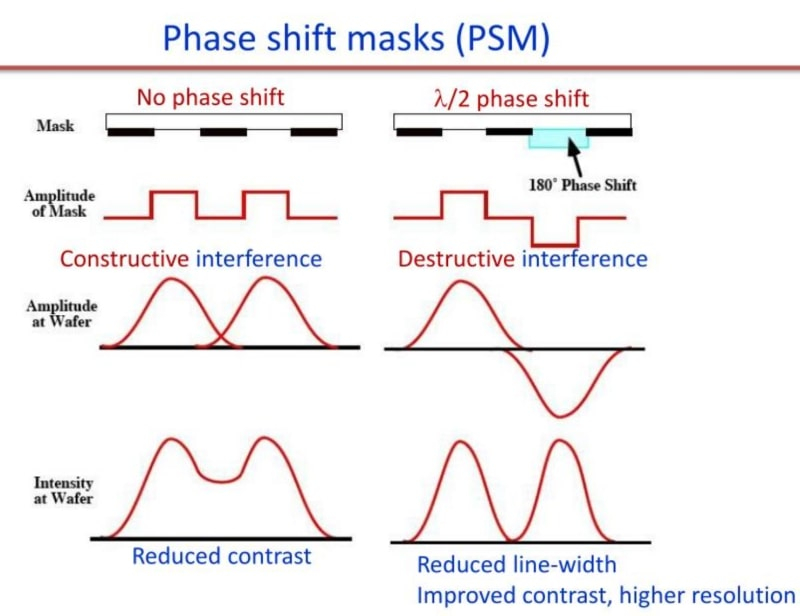

O princípio de operação da máscara de mudança de fase: após adicionar placas transparentes a alguns dos slots que retardam a radiação transmitida em metade do comprimento de onda, a interferência parasitária construtiva se transforma em destrutiva e o contraste da imagem aumenta (fonte: University of Waterloo)

Para combater esse flagelo, é usado um mecanismo tão engenhoso como uma máscara de mudança de fase: fendas comuns alternam com aquelas bloqueadas por uma substância transparente especial, passando pela qual a onda de luz muda de fase por Pi / 2. Como resultado, padrões de interferência sobrepostos de fendas adjacentes se reforçam mutuamente exatamente onde necessário. Desde a tecnologia de processo de 85 nm, as máscaras de mudança de fase tornaram-se componentes integrantes das máquinas litográficas.

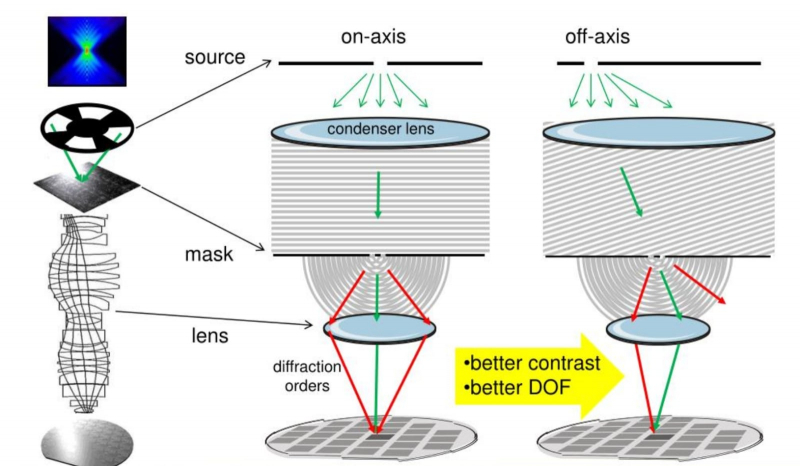

Outra opção para combater a interferência envolve o uso de iluminação fora do eixo: quando, em vez de direcionar o fluxo de luz perpendicularmente ao plano da máscara, ele é deixado em um determinado ângulo. Nesse caso, pode-se controlar com bastante precisão a sobreposição mútua de padrões de interferência de fendas adjacentes, alcançando o efeito desejado sem manipulações caras e complexas com máscaras de mudança de fase. No entanto, a própria iluminação fora do eixo dá origem a uma série de problemas que precisam ser resolvidos e, acima de tudo, a iluminação parasita das paredes internas do canal óptico no qual o sistema de lentes está localizado.

A iluminação fora do eixo de uma fotomáscara em uma máquina litográfica melhora o contraste e a profundidade de campo (Fonte: Synopsys)

Como resultado, os fotolitógrafos DUV modernos são equipados com sistemas de lentes de imersão volumosos e extremamente caros com uma abertura de 1,33 e um fator k de 0,3 – tudo isso para formar objetos na superfície fotorresistente com um tamanho mínimo de pouco mais de 40 nm (aproximadamente 130 empilhados em uma fileira de átomos de carbono). Este já é um limite de resolução física, que é impossível ultrapassar sem truques adicionais.

Além disso, para que os elementos que formam o transistor funcionem de forma confiável, são necessários espaços entre eles, cuja largura exata é determinada pelas propriedades dos semicondutores usados - e é aproximadamente igual à distância entre a fonte e o dreno . Assim, o pitch realmente alcançável (pitch) do arranjo de elementos estruturais para a tecnologia DUV de imersão – o indicador numérico que corresponde diretamente às capacidades físicas do processo – acaba sendo de aproximadamente 82 nm.

Uma fotomáscara moderna para litografia de semicondutores é uma verdadeira obra de arte, e não apenas de engenharia (fonte: SKC)

Tendo esgotado as possibilidades de reduzir a escala de detalhes no caminho óptico, os engenheiros voltaram-se para o próprio objeto do processo fotolitográfico – uma pastilha semicondutora, na qual as estruturas do transistor são eventualmente formadas pela exposição do fotorresistente e subsequente gravação. Mas, para entender exatamente como funcionam os métodos encontrados como resultado da miniaturização dos elementos lógicos semicondutores, é necessário atualizar várias idéias básicas na memória – tanto sobre o princípio de operação dos dispositivos semicondutores quanto sobre como os circuitos capazes de realizar cálculos são formados a partir desses dispositivos.

⇡#Elétron se rebelou

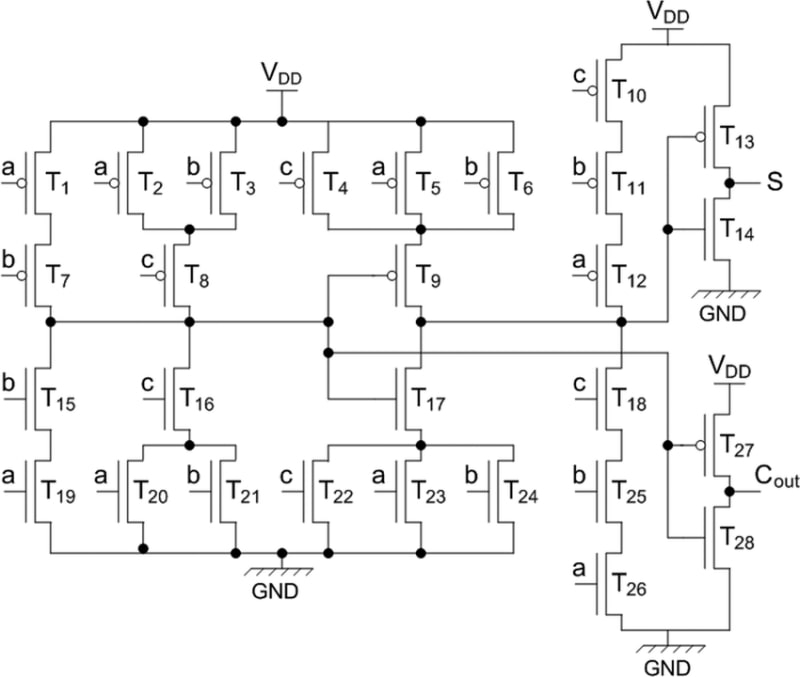

Por que os criadores de computadores precisavam de semicondutores? O fato é que essas substâncias não apenas ocupam uma posição intermediária entre os metais (passam uma corrente elétrica em condições normais) e os dielétricos (bloqueiam a transferência de carga elétrica), mas mudam suas propriedades eletricamente condutoras dependendo das circunstâncias externas. Ou seja, podem ser utilizados como relés controlados, colocando em prática uma variedade de circuitos lógicos. Veja como este simples adicionador, por exemplo:

Diagrama esquemático de um somador de 28 CMOS (fonte: IEEE Xplore)

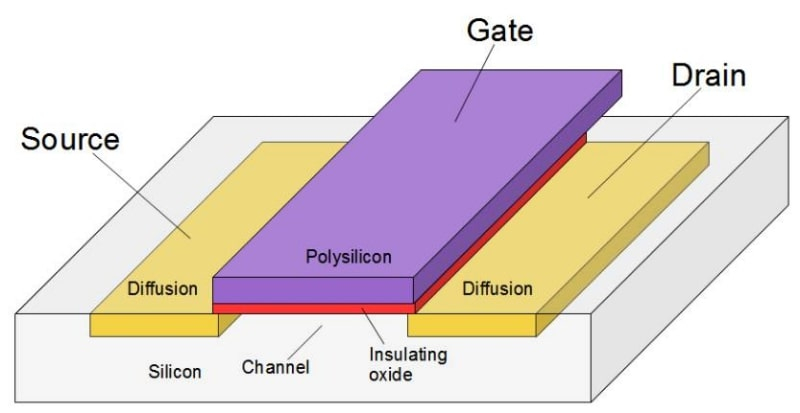

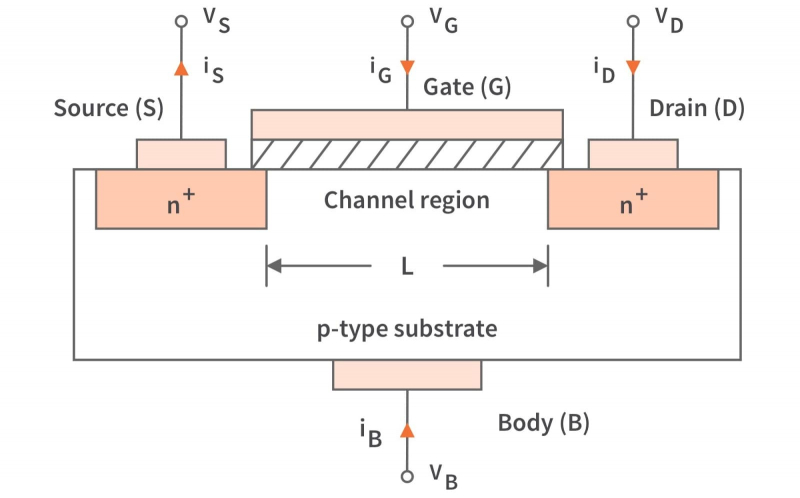

Talvez o tipo mais comum de dispositivo semicondutor em microeletrônica hoje, o transistor MOS, é controlado por uma tensão aplicada ao portão. “MOS” significa “metal-óxido-semicondutor”, e geralmente esse transistor de efeito de campo (transistor de efeito de campo de metal-óxido-semicondutor, MOSFET) consiste em:

- Zonas de fonte de carga (fonte) e dreno (dreno) – através dos contatos conectados a eles, o transistor é incluído em circuitos elétricos mais complexos,

- Canal não permanente (canal) para a passagem de carga entre a fonte e o dreno – se a tensão for aplicada ao portão, o canal está aberto e ativo, caso contrário ele simplesmente não existe,

- Uma porta isolante do canal da camada dielétrica (o mesmo óxido da abreviatura MOS – óxido isolante),

- Substrato de silício (silício),

- O próprio portão.

Elementos básicos de um MOSFET planar (fonte: Hackaday)

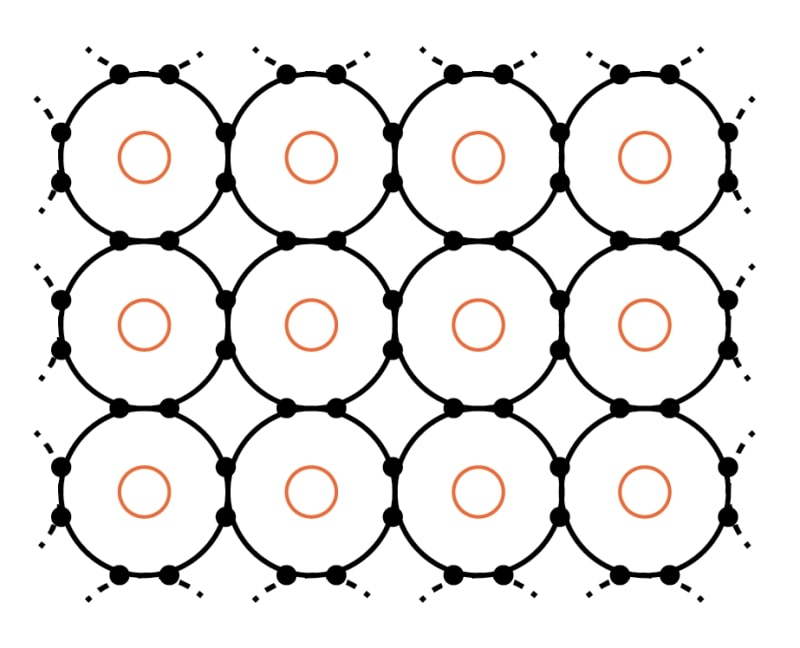

Um curso de física na escola é suficiente para entender como funciona um transistor MOS, mas por precaução, lembramos: a carga em um corpo sólido que tem uma estrutura cristalina é transportada por elétrons. Se tomarmos o silício como material de partida para um semicondutor, sua estrutura cristalina pode ser representada em um plano (na verdade, é volumosa, mas o princípio é importante aqui) como uma substituição uniforme por círculos contíguos, no centro de cada um dos quais há um núcleo carregado positivamente do átomo de Si, e nos próprios círculos estão dispostos 4 elétrons carregados negativamente – já que a camada externa do átomo de silício é formada por apenas quatro elétrons.

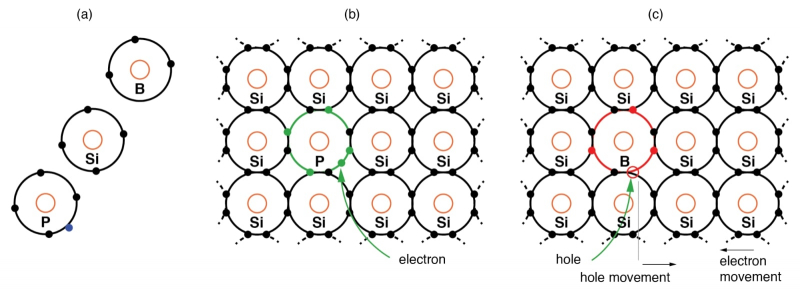

Os átomos em uma rede cristalina estão fortemente ligados por ligações eletrônicas covalentes (fonte: AllAboutCircuits)

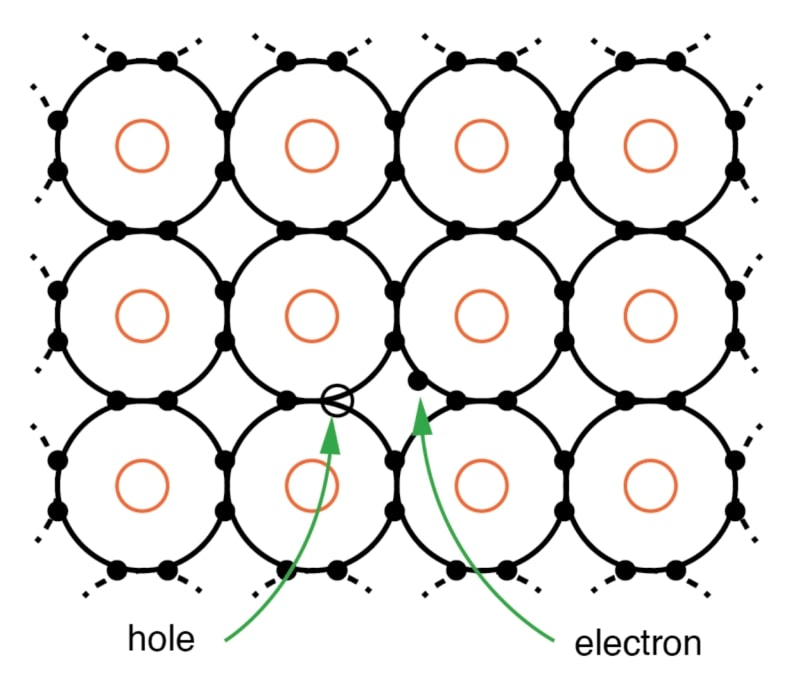

Nenhuma corrente fluirá através de tal estrutura: os elétrons adjacentes na rede cristalina são emparelhados por fortes ligações covalentes, então simplesmente não há nada para transferir a carga. Mas os elétrons, mesmo em pares, estão sujeitos à ação térmica. E se a temperatura da amostra subir tanto que a energia térmica transferida para os elétrons excede a energia da ligação covalente, um deles pode sair da órbita em torno de seu átomo e pular para o próximo na rede, deixando em vez de em si um “buraco” (buraco) – um lugar desocupado. Perto do átomo vizinho, respectivamente, não haverá mais 4 elétrons, mas 5.

Tendo saltado para uma posição vizinha na rede cristalina, o elétron se torna um portador de carga negativa e a ausência de um elétron (buraco, buraco) em seu lugar original se torna positiva (fonte: AllAboutCircuits)

Assim, o átomo do qual o elétron escapou (pulou para o vizinho) torna-se, por assim dizer, um íon e adquire uma carga positiva fictícia (um buraco no lugar do negativo que escapou), e o próximo a ele, que adquiriu um elétron em excesso, torna-se negativo. Em geral, esta seção da rede de dois átomos vizinhos ainda permanece neutra: as cargas não surgiram de nenhum lugar e não desapareceram em nenhum lugar, elas simplesmente se redistribuíram.

Mas o próprio fato dessa redistribuição dá origem à possibilidade de transferência de carga adicional por todo o volume de uma amostra macroscópica de semicondutor. Se uma diferença de potencial for criada em seus limites opostos, o elétron liberado receberá um incentivo para pular de órbita em órbita em direção ao “mais”, enquanto buracos – posições nas camadas atômicas que são equivalentes a um excesso de carga positiva livre de elétrons – será atraído para o “menos”.

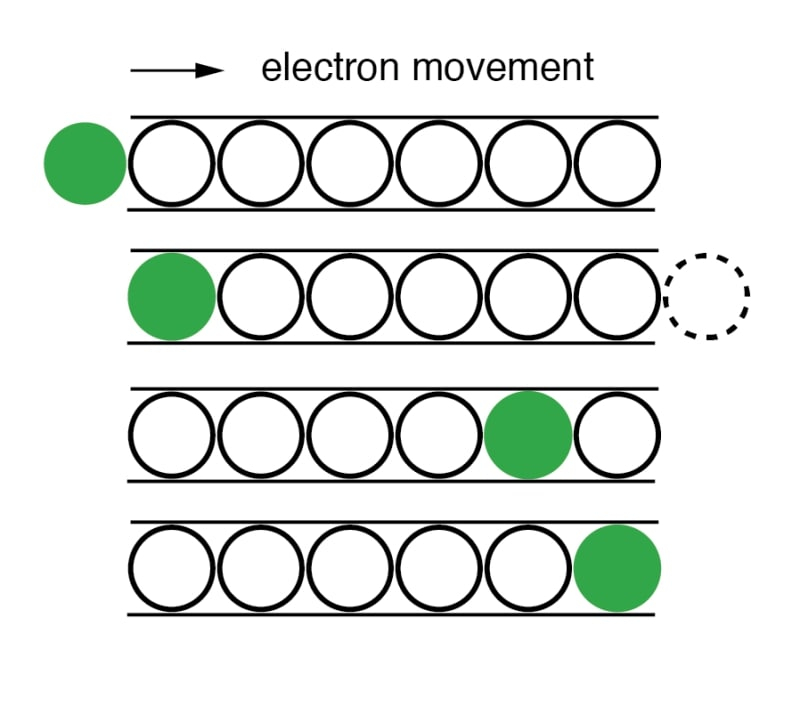

O movimento de um elétron na banda de condução de um semicondutor é semelhante ao movimento de uma bola ao longo de uma cadeia de buracos: sob a influência de uma diferença de potencial, ele se move sequencialmente de uma posição para outra na direção de “menos” para “ plus” (fonte: AllAboutCircuits)

Ao mesmo tempo, os próprios átomos dos nós da rede cristalina, é claro, não se movem para nenhum lugar – é apenas o próximo átomo, que está localizado cada vez mais próximo do limite “negativo” da amostra.

⇡#Miss não pode ser bloqueada

Se houver muitos elétrons livres na amostra, a recombinação de carga é inevitável de tempos em tempos: o próximo elétron será “mutuamente aniquilado” com um buraco, situado na camada externa de um átomo que não possui apenas um elétron no momento. É lógico, portanto, dopar um material semicondutor adicionando pequenas quantidades de impurezas a ele, o que fornecerá um excesso de cargas adicionais na amostra. Os “pequenos” são cerca de um ou dois átomos de impureza por dez milhões de átomos de silício, caso contrário haverá muitas cargas livres e a amostra começará a se comportar não como um semicondutor, mas como um metal fortemente contaminado com escórias.

A dopagem do silício cristalino é possível com átomos com um elétron extra na camada externa e com um ausente (fonte: AllAboutCircuits)

É importante que a dopagem seja possível com elétrons e buracos. Se um átomo, cujas propriedades físico-químicas permitirão que ele se encaixe facilmente na rede de cristal de silício, tiver mais elétrons na camada externa do que Si (ou seja, mais de 4 – por exemplo, 5, como fósforo, P), então isso será uma mistura do chamado tipo n, negativo: garante imediatamente a presença na amostra de elétrons livres adicionais – mais precisamente, não sobrecarregados por ligações covalentes. E se o número de elétrons na camada externa for menor que 4 (como no boro, B, que tem 3), obtém-se um dopante do tipo p, positivo, gerando automaticamente buracos adicionais na amostra.

Agora, eu gostaria de acreditar, o funcionamento de um transistor MOS fica muito mais claro, o que provavelmente já foi visto repetidamente por um leitor curioso. Neste caso, o diagrama mostra um transistor n-MOS (NMOS), com um canal na condutividade eletrônica (não buraco):

Uma fonte n-dopada e um dreno em um transistor NMOS são imersos em um substrato tipo p (Fonte: CircuitBread)

Em um substrato com condutividade do tipo p (buraco, ou seja, com falta de elétrons livres aumentados pela dopagem), duas zonas com condutividade n são criadas, novamente devido à dopagem pontual local de outro tipo, separadas por uma pequena distância (canal length L): fonte e dreno do futuro transistor. Em seguida, uma camada isolante é aplicada à superfície do semicondutor, através da qual os contatos metálicos são levados à fonte e ao dreno, e uma porta é colocada acima da zona do canal.

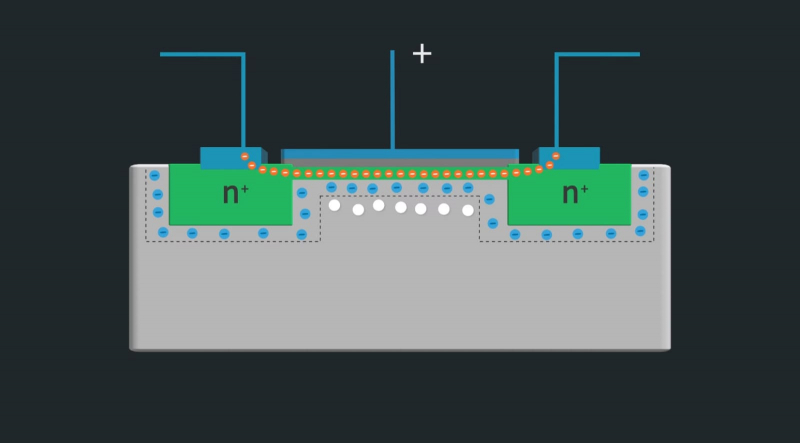

Se esse transistor estiver incluído em um circuito com uma fonte de energia, a corrente não fluirá através dele, pois o dreno é isolado da fonte pela região de condução p – os elétrons não podem se mover para lá (mais precisamente, podem, mas recombinará imediatamente com os furos disponíveis em excesso).

A tensão é aplicada ao portão – o canal está aberto (fonte: CircuitBread)

Quando uma tensão de controle positivo é aplicada à porta, ela gera uma carga positiva, que empurra o excesso de buracos da região do canal em direção ao substrato (base), e os elétrons livres disponíveis na espessura do semicondutor fluem para a zona diretamente sob a porta. . Mesmo apesar das lacunas remanescentes na espessura da amostra dopada com p, os elétrons livres inevitavelmente aparecerão sob a porta devido à quebra térmica das ligações covalentes, e serão suficientes para a formação temporária do canal.

Em algum momento, a concentração de elétrons na região diretamente abaixo da porta se tornará suficiente para que o canal se abra por um tempo, adquirindo propriedades condutivas. É então que a transferência de carga passará por ele. Quanto maior o nível de tensão no portão, mais amplo o canal obtido sob ele – e maior a corrente através do transistor.

⇡#Isso é lógico!

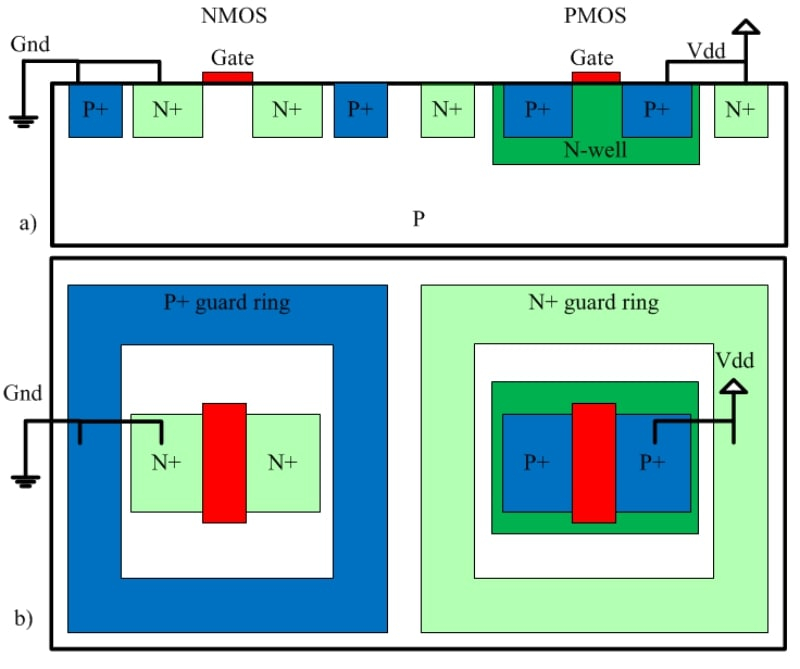

Um único MOSFET é, de fato, o interruptor mais simples: dependendo do comando externo (abrir/fechar o portão), ele passa ou não passa corrente. Em princípio, seria possível construir toda a microeletrônica em transistores n-MOS, mas descobriu-se que, do ponto de vista da lógica e da engenharia, é melhor usar pacotes complementares (mutuamente complementares) de n-MOS e p -MOS, obtendo assim estruturas CMOS (CMOS em notação inglesa).

Estrutura complementar de transistores NMOS e PMOS (vista seccional e superior): uma extensa área com n-doping (n-well) foi criada em um único substrato com p-condutividade, e um transistor PMOS já foi formado dentro dela, além de transistores de ambos os tipos delimitados de estruturas vizinhas por anéis de proteção que impedem o fluxo descontrolado de cargas (fonte: Centro Aeroespacial Alemão)

Os transistores n-MOS são chamados diretos (eles abrem quando a tensão é aplicada ao portão) e p-MOS são chamados inversos (ao contrário, eles abrem quando a tensão é removida do portão). Sua complementaridade se manifesta no fato de que o transistor MOS inverso está disposto de maneira oposta ao direto: a base p-MOS é formada por um semicondutor do tipo n, a fonte e o dreno formam inclusões do tipo p e, em vez de condutividade eletrônica, um buraco é formado no canal aberto.

A operação dos computadores da arquitetura von Neumann é baseada em operações lógicas binárias (binárias), que são fáceis e simples de implementar usando transistores CMOS. Bem, assim como…

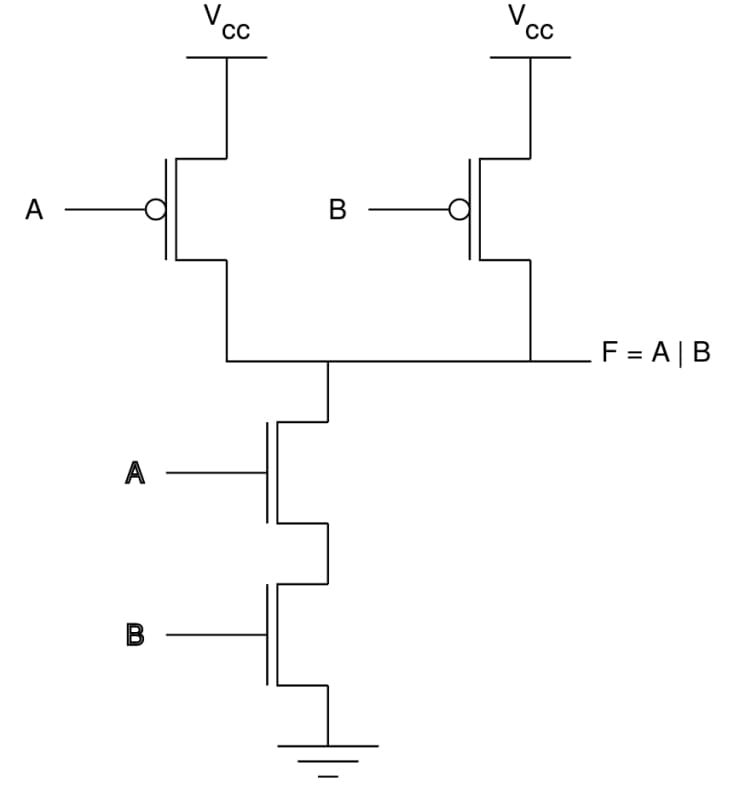

Schaeffer prime em transistores CMOS: Vcc significa “Voltage Collector Collector”, a tensão da fonte de alimentação common rail (Fonte: Wikimedia Commons)

Aqui está um diagrama da implementação em quatro transistores MOS do chamado curso de Schaeffer – uma operação lógica binária AND-NOT (na versão em inglês – NAND; uma das designações adotadas nas fórmulas de lógica binária é o traço vertical próprio, “|”), “negação da conjunção ‘ para dois argumentos. O significado do traço de Schaeffer é que se ambos os argumentos A e B são verdadeiros ao mesmo tempo, então o resultado da aplicação do traço de Schaeffer a eles é

F = A | B

— Acaba por ser falso. Em todos os outros casos, ou seja, quando pelo menos um dos argumentos é falso, o traço de Schaeffer dá o valor “verdadeiro”.

Em termos da conveniência dos cálculos manuais, esta operação pode parecer excessivamente complicada: o E lógico, o OU lógico, o NÃO lógico são muito mais simples para a percepção cotidiana. No entanto, do ponto de vista da microeletrônica aplicada, é valioso porque todas as operações básicas da lógica binária podem ser representadas por apenas um golpe de Schaeffer:

⇡#A | A = ¬A (NÃO lógico),

⇡#(A | A) | (B | B) = A || B (OR lógico),

⇡#(A | B) | (A| B) = A & B (AND lógico)

Etc. Como resultado, se abordarmos imediatamente o problema de construir circuitos lógicos complexos, levando em consideração a perspectiva de sua implementação em uma determinada base de elemento, verifica-se que um microcircuito preenchido com traços de Schaeffer (mais precisamente, blocos de transistor que implementam esta operação elementar) pode se tornar a base para a criação de sistemas computacionais de qualquer complexidade. “Qualquer” apenas dentro da arquitetura von Neumann, é claro – mas há muitas tarefas para máquinas desse tipo e, para as mais complexas, os computadores quânticos já estão sendo desenvolvidos. Do ponto de vista da produção de semicondutores, quanto maior o grau de uniformidade dos elementos em miniatura do microcircuito desenvolvido, mais fácil é projetar e fabricar.

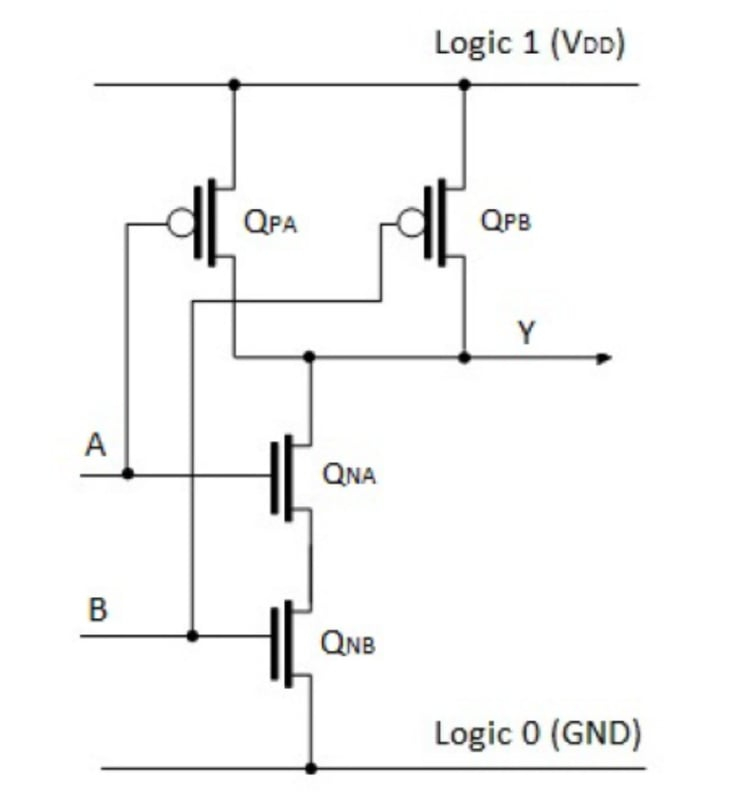

Outro diagrama de traço de Schaeffer em transistores CMOS: aqui Vdd, “Voltage Drain Drain”, denota a tensão no dreno do transistor conectado ao barramento comum e é equivalente em significado a Vcc da figura anterior (fonte: Wikimedia Commons)

Ler o esquema de implementação do traço de Schaeffer (transistores n-MOS e p-MOS nele é fácil de distinguir pela ausência ou, consequentemente, a presença de um círculo no símbolo do portão) é especialmente simples se você imaginar que o Vcc / O barramento Vdd para os elementos conectados a ele VLSI “é fornecido” por uma unidade lógica, e o barramento de terra “gera” um zero lógico. Sob essa suposição, o curso de Schaeffer atua como uma válvula complexa que, sob a influência de sinais de controle, de acordo com certas regras, muda para a saída um zero lógico de baixo ou uma unidade lógica de cima.

Então, se ambos (aplicados, lembre-se, às portas de cada par complementar de transistores n-MOS e p-MOS) os sinais de controle A e B se tornarem verdadeiros simultaneamente, dois MOSFETs diretos (abaixo, conectados em série) serão abertos e inversas (acima, conectadas em paralelo) – ambas são fechadas. Isso significa que um zero lógico do barramento de aterramento de baixo “passará” livremente para a saída de tal circuito, e uma unidade lógica do barramento de força será “bloqueada” por transistores inversos abertos.

Agora, seja pelo menos um dos sinais de controle A e B igual a zero lógico. Nesse caso, a parte inferior do circuito estará aberta (através dos transistores diretos conectados em série, pelo menos um dos quais certamente estará aberto, o zero lógico não “passará”) e pelo menos um dos transistores inversos “perderão” livremente o lógico de cima.

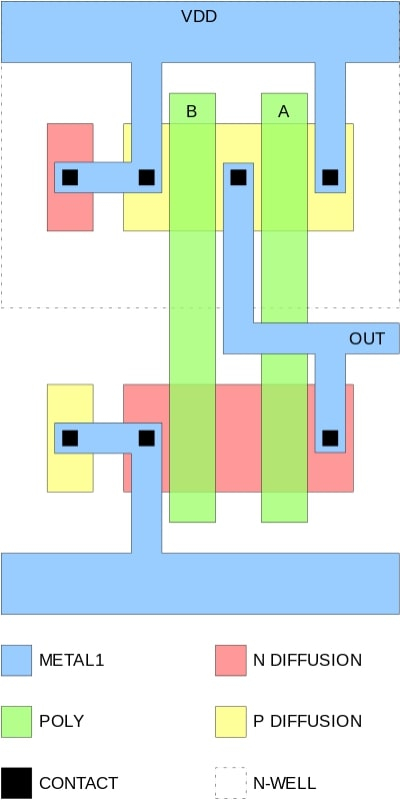

Assim, para construir um único curso de Schaeffer de acordo com o esquema dado anteriormente, será suficiente colocar duas fileiras de elementos semicondutores do tipo n e p alternados próximos com as inclusões correspondentes para fontes e drenos, colocar portas de controle perpendicularmente – e conectar tudo isso com pneus de metal. Acontece algo assim – esta é uma vista superior de um plano no qual os elementos que formam os transistores e as conexões entre eles são colocados em três camadas:

Implementação prática do golpe de Schaeffer em transistores CMOS (Fonte: Wikimedia Commons)

Os quadrados pretos representam os contatos de metal que conectam as camadas verticalmente. Para construir circuitos lógicos mais complexos, é necessário combinar os traços de Schaeffer de uma maneira especial – é isso que as camadas de metal adicionais (não mostradas aqui) servem em cima da mostrada em azul.

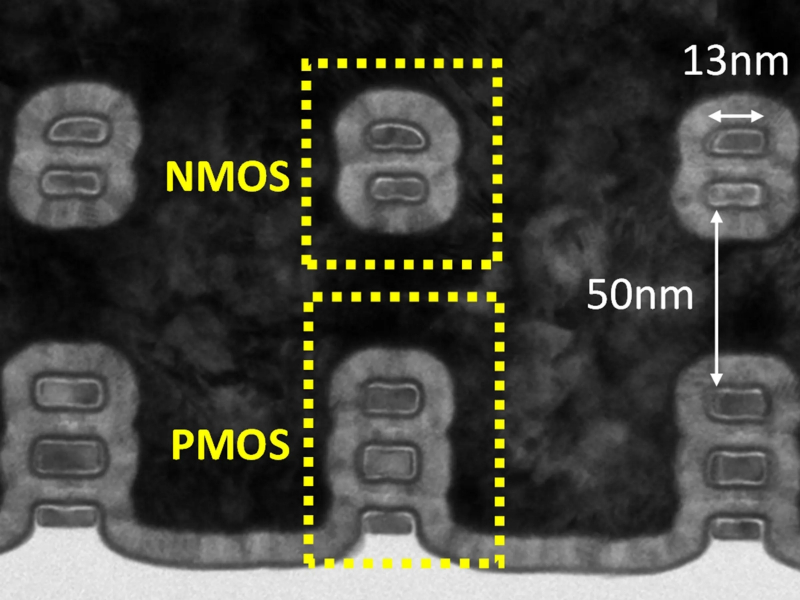

Recentemente, o trabalho está em andamento para criar transistores com transistores n-MOS e p-MOS localizados verticalmente, e não no mesmo nível – isso permitirá, sem truques adicionais, cumprir mais uma vez a lei de Moore, dobrando a densidade de transistores por polegada quadrada em equipamentos existentes. Mas até agora, a colocação vertical de transistores complementares (implementados, aliás, usando uma tecnologia relacionada ao SAMP, que será discutida a seguir) continua sendo um desenvolvimento promissor que não atingiu o nível de produção em massa.

Uma micrografia de uma amostra de laboratório de um chip semicondutor com transistores n-MOS colocados acima de seus p-MOS complementares (fonte: Intel)

Agora resta descobrir em detalhes como os componentes semicondutores subminiaturas de futuros transistores são tecnicamente formados durante a produção em massa de microprocessadores – e devido aos quais os fabricantes de chips ainda conseguem ultrapassar o limite da resolução máxima permitida de 82 nm (ou ~ 40 nm , se tomar metade da largura do espaço entre os componentes repetidos).

⇡#Como Lefty gravou o mandril

Um dos truques técnicos mais eficazes ao longo do caminho é o processamento de várias passagens (padronização múltipla) da peça de trabalho. O procedimento básico para fotolitografia em um semicondutor envolve uma única exposição do fotorresistente (fotorresistente, PR), seguida de revelação e lavagem, após o que o substrato do semicondutor é gravado nas áreas expostas (etch) e, finalmente, os restos do fotorresistente estão removidos.

Principais etapas da fotolitografia clássica (de passagem única) (Fonte: Lam Research)

Suponha que este procedimento já seja realizado no limite da resolução realmente alcançável do sistema (os mesmos 82 nm para fotolitografia DUV). No entanto, ninguém proíbe, tendo precisamente visado, expor a mesma amostra uma segunda vez com um deslocamento de metade desse mesmo limite de resolução – de modo que as estruturas criadas na superfície do semicondutor sejam colocadas exatamente entre as feitas na primeira passagem . Sem qualquer esforço adicional, a taxa de produção real é reduzida pela metade imediatamente.

Aqui, o fato de que as estruturas básicas em um chip semicondutor – seja um chip de memória ou um lógico – sejam do mesmo tipo e espaçadas de maneira bastante uniforme ajuda muito. Grosso modo, eles são os traços de Schaeffer alinhados em fileiras, e todas as combinações não triviais complexas deles – portas lógicas, somadores, etc. – são formadas conectando os elementos de AND-NOT uns aos outros na ordem correta com contatos de metal que já são realizados em camadas de microchip mais altas e com uma escala característica maior.

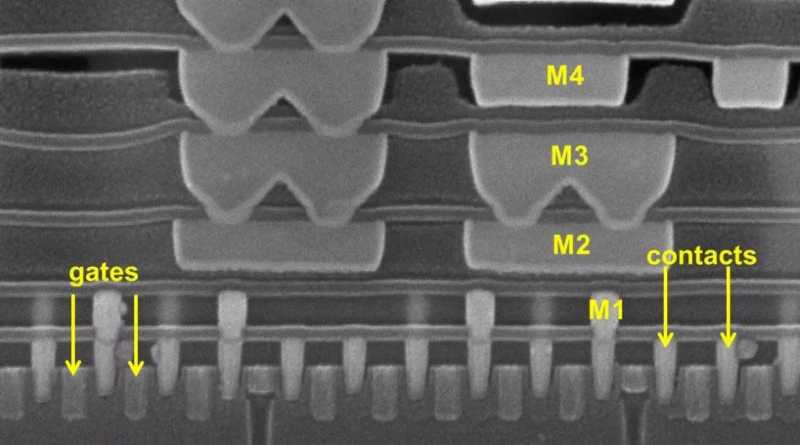

Micrografia de uma seção transversal de 16nm de um processador Exynos 7420 litografada usando tecnologia multipass, ao longo de uma das fileiras de aletas FinFET e através das portas do transistor: mostrando as próprias portas, os contatos adequados para as fontes / drenos e as camadas de interconexão de metal deitado por cima (fonte: TechInsights)

Para implementar a fotolitografia de duas passagens, várias técnicas foram desenvolvidas que envolvem o uso das chamadas máscaras duras. Eles são chamados de rígidos porque devem suportar o procedimento de lavagem da camada fotorresistente primária, de modo que os polímeros orgânicos semelhantes a gel usados em um processo de passagem única não possam atuar em seu papel.

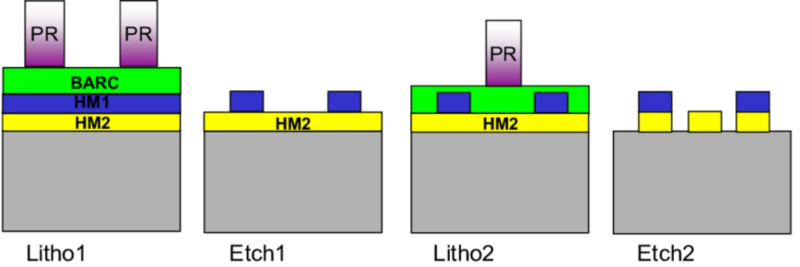

Além disso, a segunda máscara dura deve resistir ao ataque e lavagem da primeira, portanto também deve ser substâncias de propriedades químicas diferentes: carboneto e óxido de silício, por exemplo. Como resultado, a operação de reduzir pela metade a escala realmente alcançável de microestruturas se resume à sequência “litografia-gravura-litografia-gravura” (litografia-gravura-litografia-gravura, daí a abreviatura LELE).

Fotolitografia LELE de duas passagens: o fotorresistente (PR) é aplicado a uma camada antirreflexo especial (Bottom Anti-Reflectant Coating, BARC) e duas máscaras rígidas. Após o primeiro ciclo “litografia – gravação”, BARC e PR são aplicados novamente nas áreas desejadas, então o ciclo é repetido (fonte: IEEE Xplore)

Uma versão aprimorada desse método é o padrão múltiplo auto-alinhado (SAMP). O fato é que expor duas vezes uma pastilha de silício com um diâmetro de 300 mm (um blank padrão para máquinas DUV) com um deslocamento idealmente preciso de apenas dezenas de nanômetros é, para dizer o mínimo, uma tarefa tecnologicamente difícil.

É mais simples cuidar imediatamente para que na superfície de um semicondutor revestido com um fotorresistente, as estruturas sejam formadas com um passo característico metade do tamanho do limite de resolução realmente alcançável. É mais fácil, novamente, graças à regularidade deliberada de tais estruturas – e, consequentemente, aos padrões usados para expô-las.

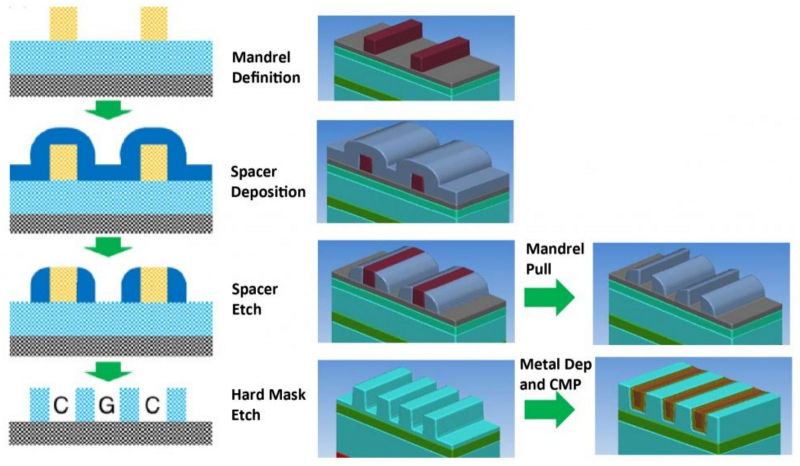

No processo clássico de passagem única, tiras estreitas separadas são formadas no fotorresistente, cada uma das quais, após a gravação, se tornará uma lacuna entre as aletas semicondutoras adjacentes (elas acabarão sendo as cristas dos transistores FinFET) e, portanto, o distância entre as tiras corresponde à espessura dessas mesmas nervuras. O modelo para SAMP é construído de tal forma que apenas cada segundo espaço entre as aletas semicondutoras é exposto através dele. As estruturas verticais que aparecem após o desenvolvimento e a lavagem da primeira camada de fotorresistente atuam como mandris ou mandris (mandril) – é o que é chamado no encanamento de um dispositivo em forma de cone ligeiramente afunilado em direção a uma das extremidades para estampagem / formação peças anulares ou cilíndricas, bem como para endireitar tubos amassados.

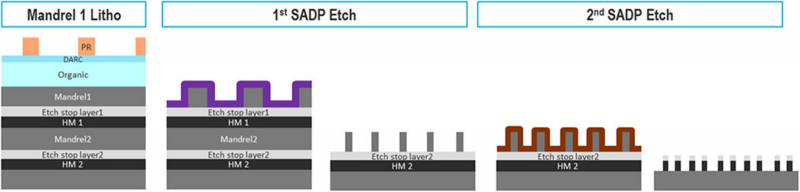

Fotolitografia de duas passagens SADP: moldando os mandris na máscara dura – aplicando o espaçador – gravando o espaçador e removendo o material do mandril – gravando final a máscara dura (Fonte: Lam Research)

Nas paredes desses mandris, usando métodos finos de deposição uniforme (deposição em camada atômica, ALD, ou deposição de vapor químico, CVD), literalmente átomo por átomo, é aplicada uma camada de material separador, formando, por assim dizer, um revestimento de estruturas criadas no limite de resolução da fotolitografia. A distância entre os limites externos de revestimentos adjacentes pode ser facilmente feita pela metade desse limite, conhecendo a taxa de deposição do material de revestimento e controlando o tempo.

Então, depois de remover os próprios mandris (durante um processo semelhante à lavagem do fotorresistente exposto, mas com outros produtos químicos) e gravar a superfície que permanece não coberta pelo material de separação, as nervuras semicondutoras vizinhas serão separadas umas das outras por uma distância metade do tempo que o processo realmente alcançável em uma determinada litografia. E nenhuma contradição com as leis da física – apenas engenharia engenhosa veio em auxílio da óptica.

Confiar no SAMP elimina a necessidade de fazer duas exposições separadas da placa em branco com seu deslocamento microscopicamente preciso. Além disso, você pode repetir este procedimento se tiver o cuidado de primeiro aplicar várias máscaras duras para formar mandris – duas vezes e quatro.

A fotolitografia SAQP de quatro passagens é reduzida a dois SADPs sucessivos – apenas com duas máscaras rígidas pré-aplicadas à amostra, duas camadas de etch stop e duas camadas de formação de mandril (fonte: SPIE)

Como resultado, se um SADP de duas passagens (múltiplo na abreviação é concretizado em duplo) permite alcançar um intervalo entre elementos (pitch) de cerca de 40 nm em vez de 82 em uma configuração básica de DUV, então um SAQP de quatro passagens (quádruplo ) já é quase 20 nm. Ao mesmo tempo, a espessura do cume semicondutor (um único detalhe mínimo na superfície do substrato) para a já mencionada tecnologia de processo TSMC “7 nm” é de 6 nm – a propósito, quase o mesmo que para o anterior ” 10 nm” padrão de produção. Portanto, em princípio, o nome de marketing “7 nm” ainda tem algum significado físico, embora não indique mais diretamente o tamanho do principal elemento semicondutor ativo do transistor MOS – o comprimento de seu canal.

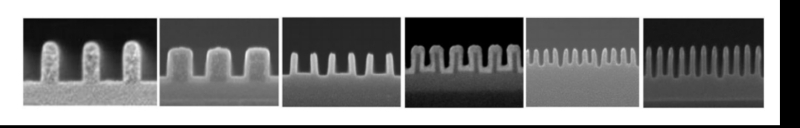

Micrografias sequenciais de seções transversais da peça, litografadas pelo método SAQP, da esquerda para a direita: a formação dos mandris – a aplicação de um separador – a remoção do material dos mandris da linha superior – a aplicação de um novo separador sobre os restos do primeiro, que agora funcionam como novos mandris, – a remoção de material entre os separadores – o ataque final da peça a substratos para obter estruturas com uma largura de 15 nm e uma distância (pitch) de 30 nm ( fonte: SPIE)

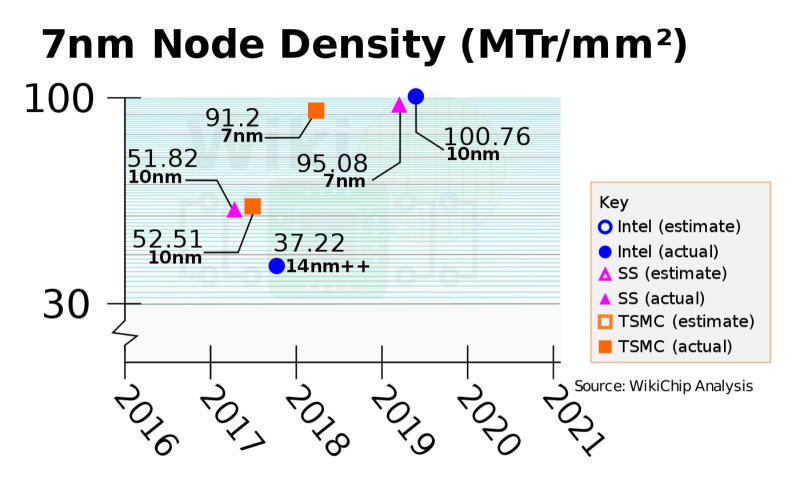

Mas, como foi enfatizado mais de uma vez, a “lei de Moore” é formulada não para o tamanho de um único transistor, mas para a densidade de transistores em um chip acabado. É por isso que as dimensões de um elemento semicondutor típico não são tão importantes: a própria distância entre as cristas adjacentes (fin pitch, FP) e, em menor grau, a lacuna entre as trilhas metálicas adjacentes que transportam corrente (passo mínimo do metal, MMP ) matéria. Assim, durante a transição da tecnologia de processo “10 nm” para “7 nm”, o FP diminuiu cerca de 17% (era 34-36 nm, tornou-se 27-30 nm), MMP – apenas 5% ( era 36-44 nm tornou-se 36-40 nm para várias implementações dos padrões de fabricação relevantes pela Intel e TSMC).

Tabela resumida de densidades de transistores em superfícies VLSI, feitas de acordo com processos técnicos realmente implementados de “14 nm” a “7 nm” em diferentes fábricas, milhões de peças. por metro quadrado mm: a meta de produção de 7 nm da Samsung é alcançada em máquinas EUV, o restante em máquinas DUV (Fonte: WikiChip)

A densidade de transistores em um chip para os padrões tecnológicos incorporados hoje em instalações DUV seriais é de 90 a 102 milhões por 1 mm2, e isso, aparentemente, já é o limite da fotolitografia a laser excimer. É agora que chega a vez da tecnologia EUV baseada em um esquema óptico fundamentalmente diferente, e com ele problemas físicos, descobertas e truques tecnológicos completamente diferentes. Mas essa é uma história completamente, completamente diferente.