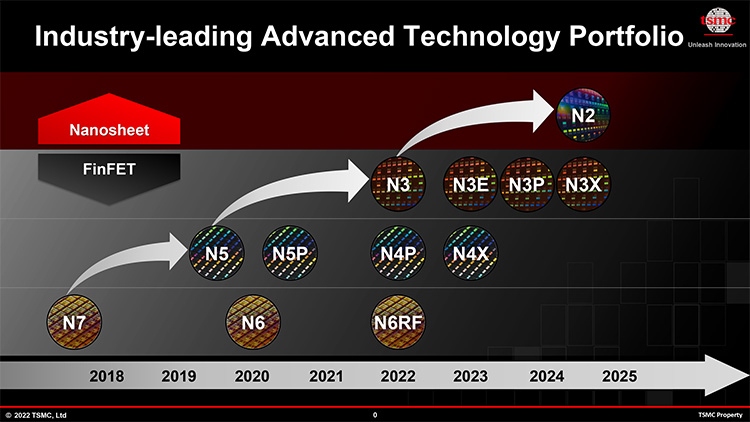

A TSMC divulgou detalhes sobre a família de tecnologia de processo N3 (classe de 3 nm) que substituirá as principais tecnologias da forja de semicondutores entre o início de 2023 e o final de 2025. A família N3 incluirá um total de cinco processos técnicos de diferentes especializações.

TSMC

A produção em massa de chips baseados no processo base N3 começará no segundo semestre deste ano. A fabricante taiwanesa estará pronta para fornecer chips de 3 nm acabados no início de 2023. Em comparação com a tecnologia N5, a tecnologia N3 aumentará as frequências em 10-15%, mantendo um consumo de energia constante ou reduzirá o consumo de energia dos cristais em 25-30% em uma frequência constante. Além disso, os novos padrões permitirão aumentar a densidade de transistores em um chip em cerca de 1,7 vezes.

Via de regra, processos técnicos piloto como o N3 atraem a atenção dos principais fabricantes de chips, que estão dispostos a pagar mais pela liderança tecnológica no mercado. Entre as empresas que estarão na vanguarda da colocação de encomendas para a produção de produtos por este processo, certamente estará a Apple. Ao mesmo tempo, para produtos de massa, a TSMC oferecerá posteriormente uma família de processos de fabricação relacionados com otimização de vários parâmetros. Esta família incluirá as tecnologias N3E, N3P, N3S e N3X.

O processo N3E será uma versão melhorada do N3 com maior rendimento cristalino. Isso será alcançado reduzindo ligeiramente a resolução da litografia, devido à qual a densidade dos transistores em um chip será revertida em cerca de 10% em comparação com o N3. Mas, por outro lado, o custo dos chips diminuirá e uma ampla gama de clientes terá acesso à tecnologia de 3 nm. Além disso, os indicadores alvo da tecnologia de processo N3E incluem uma melhoria nas características de frequência e energia em comparação com N3 em 3-4%. A produção piloto de chips usando a tecnologia N3E começará no terceiro trimestre deste ano e a produção em massa em meados do próximo ano. Assim, as entregas de produtos N3E acabados poderão começar no final de 2023.

Os processos N3P e N3S serão opções para otimizar o N3E para diferentes classes de aplicação. O N3P se concentra em chips de alto desempenho, enquanto o N3S se concentra em chips energeticamente eficientes com maior densidade de transistores. Ambos os processos técnicos estão previstos para 2024.

Outra tecnologia de processo, N3X, aparecerá nas ofertas da TSMC mais perto de 2025, quando a empresa começar a dominar o próximo estágio dos padrões de semicondutores. O objetivo desta tecnologia é a produção de processadores de alto desempenho, para os quais é importante o uso de altas correntes de operação e operação de longo prazo em frequências de clock aumentadas.

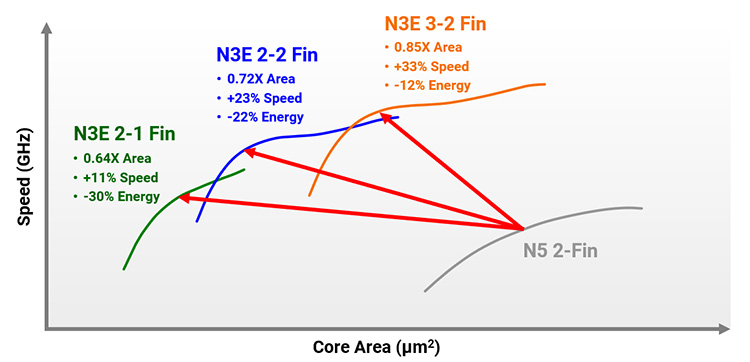

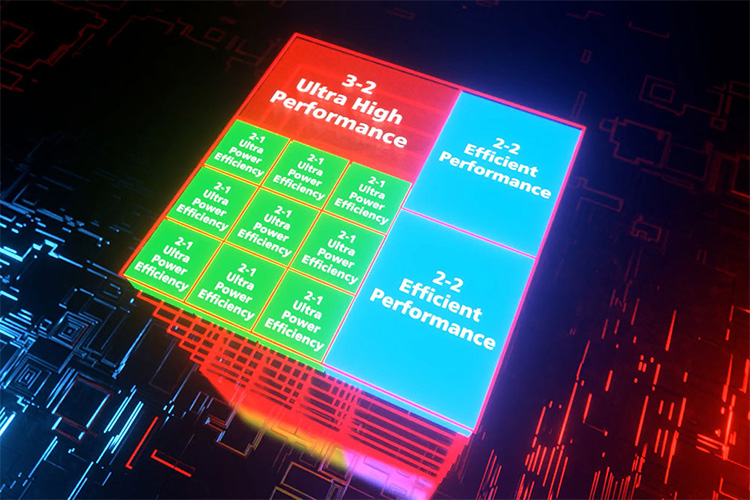

Falando da família de processos N3, a TSMC anunciou a tecnologia FinFlex, que deve aumentar a atratividade dos chips da empresa para os clientes. A essência da tecnologia é que o fabricante permitirá o uso de bibliotecas de diferentes transistores FinFET dentro de um único cristal semicondutor.

O conjunto de opções disponíveis inclui transistores com porta tripla e aletas de dois canais (3-2 Fin), duas portas e duas aletas (2-2 Fin) e duas portas e uma aleta (3-1 Fin). O primeiro tipo de transistor é bom para aplicações de alta frequência e alto desempenho, o segundo é bom para balancear desempenho e eficiência de energia, e o terceiro é bom para chips de alta densidade com eficiência de energia. Será possível combinar diferentes transistores dentro de um único chip, o que possibilitará fazer soluções híbridas em que blocos produtivos e energeticamente eficientes lado a lado. A tecnologia FinFlex estará disponível em toda a família de processos N3.

Mais fino que o N3, a tecnologia de processo da TSMC deve entrar em operação em 2025-2026. Na próxima tecnologia N2, a empresa passará para o uso de transistores GAAFET e litografia EUV de alto valor de abertura.