Após as normas de 5nm, 3nm se tornará o próximo processo tecnológico importante para a TSMC. De acordo com o fabricante taiwanês, a pesquisa e o desenvolvimento de sua tecnologia de processo de 3 nm estão progredindo dentro do cronograma. A empresa anunciou recentemente que lançará a produção experimental em 2021. No entanto, a impressão em massa em grande escala deve começar no segundo semestre de 2022.

Embora ainda demore quase dois anos para que o processo de 3nm da TSMC entre em produção em massa, muitos de seus clientes já estão interessados nesses padrões de ponta. É relatado que a TSMC está preparando quatro ondas de implantação de instalações de fabricação de 3nm. A maior parte da primeira onda será transferida para a Apple, o que é bastante esperado. Começando com o processador A10 na série 2016 do iPhone 7, os processadores da série A da Apple são fabricados exclusivamente pela TSMC e sempre têm prioridade.

A tecnologia de processo de 3 nm deve melhorar significativamente o desempenho e a eficiência energética dos chips. Em reuniões dedicadas às demonstrações financeiras da empresa no primeiro e segundo trimestres deste ano, o CEO da TSMC, Wei Zhejia, disse que em comparação com a tecnologia de processo de 5nm, as normas de 3nm irão aumentar a densidade dos transistores em 70%, bem como aumentar as frequências chips em 10-15% com o mesmo consumo de energia. Por sua vez, a eficiência energética nas mesmas frequências aumentará em 25-30%.

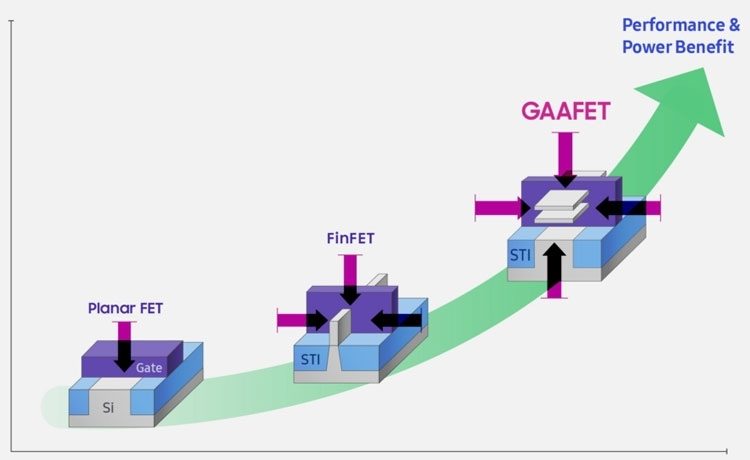

De acordo com o Taiwan Economic Daily, a TSMC já alcançou um grande avanço na adoção da tecnologia de processo 2nm. O processo de pesquisa e desenvolvimento encontra-se em estágio avançado. A empresa está otimista de que, no segundo semestre de 2023, o número de cristais adequados em sua produção experimental de 2 nm poderá chegar a 90%. As cadeias de suprimentos também mostram que, ao contrário dos processos de 3nm e 5nm que usam FinFETs, o processo de 2nm da TSMC usa uma nova arquitetura MBCFET (Multi Bridge Channel FET), que terá um canal de transistor que se parece com alguns canais dispostos um acima do outro na forma de nanopáginas, cercados em todos os lados por um portão (você pode ler sobre esses transistores fabricados pela Samsung em nosso material de 14 de março de 2019).

No ano passado, a TSMC montou uma equipe de P&D norma 2nm para encontrar o caminho de desenvolvimento ideal. O uso de MBCFET permitirá superar o limite físico de corrente de fuga para transistores em massa FinFET. A TSMC anunciou anteriormente que sua tecnologia de processo de 2nm será fabricada em Baoshan e Hsinchu. Ela também planeja construir quatro enormes fábricas de wafer de silício P1-P4 (450 mm de diâmetro) em 90 hectares. Dado o atual progresso em pesquisa e desenvolvimento para os regulamentos de 2nm da TSMC, a empresa deve entrar em produção em massa em 2024.