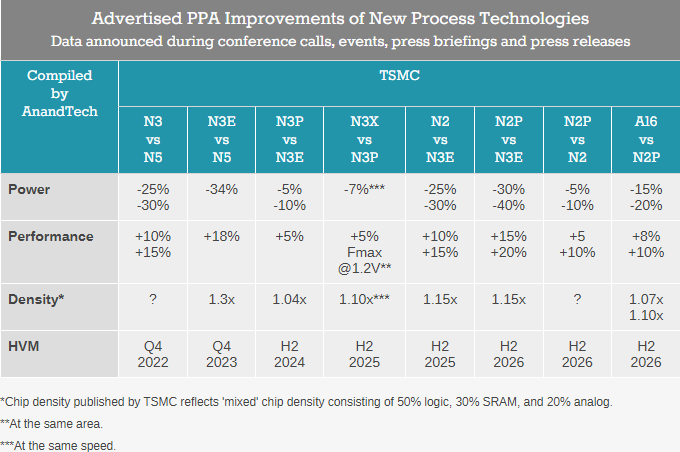

Na semana passada, representantes da TSMC anunciaram que até o final deste ano a empresa iniciaria a produção em massa de chips usando a tecnologia N3P, e isso levou a equipe de recursos da AnandTech a resumir todas as informações disponíveis sobre os planos imediatos da empresa em uma tabela. Em 2025 e 2026, a TSMC pretende introduzir quatro novos processos tecnológicos.

Fonte da imagem: TSMC

O desenvolvimento dos processos técnicos N3X e N2 está previsto para já no próximo ano, com estes eventos concentrados no segundo semestre de 2025 se tudo correr conforme o previsto. Até certo ponto, as tecnologias N3X e N2 competirão entre si pelas preferências dos clientes da TSMC. O primeiro deverá reduzir o consumo de energia em 7% em relação ao N3P, que será dominado no segundo semestre deste ano. A velocidade de comutação dos transistores aumentará 5% a uma tensão de 1,2 V com a mesma densidade de transistor, e o último valor aumentará 1,1 vezes a uma frequência de clock constante.

Fonte da imagem: AnandTech

A tecnologia de processo N2 promete reduzir o consumo de energia em 25–30% em relação ao N3E, que está em produção desde o quarto trimestre do ano passado. Ao mesmo tempo, a velocidade de comutação dos transistores aumentará em 10–15% e sua densidade de posicionamento aumentará em 1,15 vezes. O mesmo aumento de densidade será proporcionado pelo processo técnico N2P em relação ao N3E, que será dominado no segundo semestre de 2026, mas o ganho no consumo de energia aumentará para 30–40%, enquanto a velocidade de comutação dos transistores aumentará em 15–20%. Em outras palavras, uma comparação direta de N2 e N2P proporcionará um benefício não tão perceptível no consumo de energia (5–10%) e no desempenho (5–10%), e a densidade do transistor permanecerá inalterada.

Como parte da tecnologia de processo N2, a TSMC apresentará pela primeira vez a estrutura do transistor nanosheet gate-surround (GAA). Isto deve melhorar significativamente o desempenho, reduzir o consumo de energia e aumentar a densidade do transistor. A tecnologia de processo concorrente N3X pode superar o N2, especialmente em tensões mais altas. Qual dos clientes da TSMC pode gostar mais da tecnologia N3X devido à falta de alterações na estrutura dos transistores (FinFET), o que deve ter um efeito benéfico na taxa de defeitos.

A TSMC planeja desenvolver os processos tecnológicos N2P e A16 até 2026. Este último será uma versão orientada para o desempenho do N2, enquanto o último oferecerá características de desempenho de 1,6 nm combinadas com fonte de alimentação reversa. O N2P pode oferecer uma redução de 5 a 10% no consumo de energia, mantendo o mesmo desempenho, ou um desempenho proporcionalmente aumentado, mantendo o mesmo consumo de energia em comparação com o N2 básico.

A tecnologia de processo A16 está pronta para oferecer uma redução de 20% no consumo de energia em relação ao N2P, ou um aumento de 10% no desempenho nos mesmos níveis de consumo de energia. A densidade de colocação dos transistores A16 aumentará em 10% em relação ao N2P. Em chips orientados para alto desempenho, a tecnologia de processo A16 mostrará seu melhor lado, mas a fonte de alimentação do lado reverso do wafer de silício tornará sua produção bastante cara.