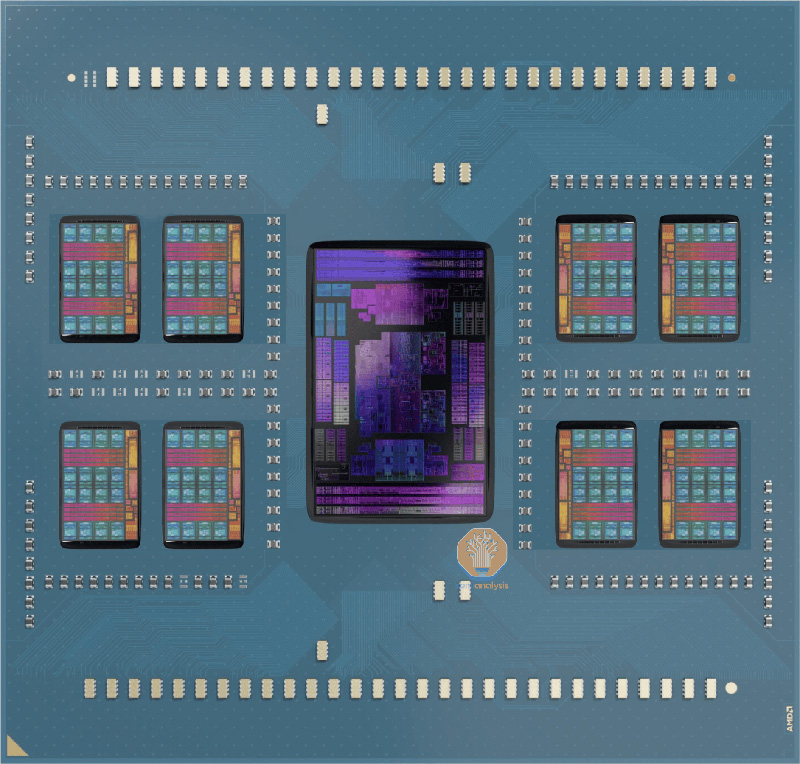

Na próxima semana, a AMD planeja apresentar a família de processadores AMD Epyc com um aumento no número de núcleos para 128. Antecipando o anúncio, os detalhes de sua estrutura se tornaram conhecidos. Esses processadores, de codinome Bergamo, usarão núcleos Zen 4c e são muito diferentes do Zen 4 comum.

Fonte da imagem: SemiAnalysis

Inicialmente, assumiu-se que o Zen 4c seria diferente do Zen 4 com um tamanho de cache reduzido. No entanto, isso acabou sendo apenas uma consequência da nova solução de layout. Por meio da cooperação com a TSMC, a AMD conseguiu projetar e lançar um novo chiplet CCD que pode acomodar 8 em vez de 16 núcleos. Além disso, este chiplet tem aproximadamente a mesma área de matriz que um chiplet de oito núcleos com núcleos Zen 4 convencionais.

Ao mesmo tempo, o tamanho do cache L3 por cristal CCD permaneceu inalterado – 32 MB, o que significa que a quantidade de memória cache por núcleo realmente diminuiu. Mas, por outro lado, a AMD teve a oportunidade de criar processadores com 128 núcleos, enquanto o Epyc Genoa existente em núcleos Zen 4 regulares tem no máximo 96 núcleos. Por fim, a modificação máxima de 128 núcleos do Bergamo receberá 256 MB de cache L3, e o cache L3 da geração Epyc de 96 núcleos do Genoa atinge 384 MB.

O CCD de 16 núcleos nos núcleos Zen 4c tem uma área de matriz de apenas 72,7 mm², que é apenas um pouco maior que a área do CCD de 8 núcleos com núcleos Zen 4 (66,3 mm²). Ambos usam a tecnologia de processo de 5 nm da TSMC. A densificação do cristal é conseguida por vários métodos. Em primeiro lugar, o backlog para conexões de cache 3D foi removido do Zen 4c – certamente não estará disponível em processadores baseados em tais núcleos. Em segundo lugar, os núcleos Zen 4c terão velocidades de clock mais baixas, o que significa que você pode remover as peças de silício necessárias para estabilizar as condições térmicas e reduzir as correntes de fuga. Em terceiro lugar, a AMD mudou o design do núcleo – seus componentes são distribuídos de acordo com um novo esquema e o cache de segundo nível usa células SRAM 6T mais compactas em vez das antigas 8T.

O die CCD Zen 4c de 16 núcleos consiste em dois CCXs de oito núcleos, o que significa que o cache L3 do Bergamo é dividido em blocos de 16 MB. Também no processador, que combina até oito CCDs de 16 núcleos, existe um chiplet de E/S, exatamente igual ao Genoa. Graças a isso, os núcleos Epyc no Zen 4 e Zen 4c são totalmente compatíveis com pinos e podem ser usados nas mesmas plataformas com soquete SP5.