No outro ano, a próxima conferência anual da International Electron Devices Meeting 2019 começou em San Francisco. Entre os muitos tópicos interessantes levantados no IEDM 2019, destaca-se o tópico da produção piloto de memória magnorresistiva STT-MRAM no efeito de transferência de spin de elétrons. Samsung, GlobalFoundries, TSMC e Intel apresentaram suas conquistas no desenvolvimento da próxima geração de memória não volátil. À medida que novas informações estiverem disponíveis, divulgaremos detalhes dos discursos dos representantes da empresa. Enquanto isso, anunciaremos brevemente uma nova conquista da Intel – a empresa introduziu o array STT-MRAM para cache L4.

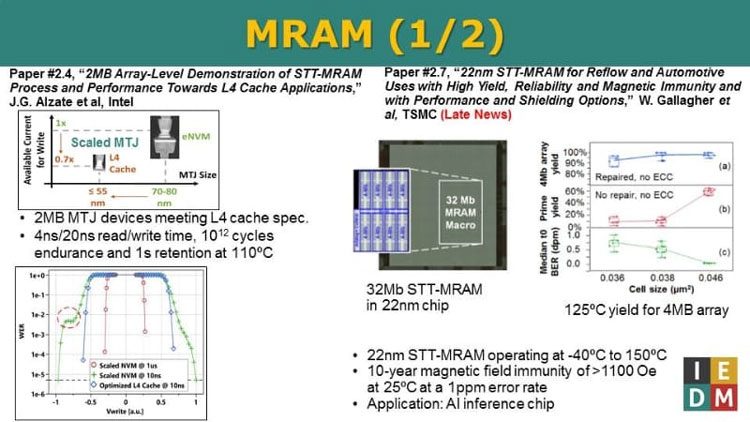

Um ano atrás, no IEDM 2018, a Intel anunciou o lançamento de matrizes STT-MRAM de 7 Mbit usando uma tecnologia de processo de 22 nm (22FFL). O novo chip protótipo contém uma matriz STT-MRAM de 2 MB. Essa é a memória para aplicativos incorporados, que promete substituir o NAND flash incorporado tradicional e a SRAM, se estivermos falando sobre o uso do STT-MRAM como memória cache para processadores e aceleradores. No entanto, enquanto não estamos falando de processadores. A Intel sugere o uso do STT-MRAM incorporado como cache para aceleradores de tarefas de IA e aprendizado de máquina.

O bloco STT-MRAM de 22 nm e 2 MB apresentado permite ler dados a uma velocidade de 4 ns e gravá-los a uma velocidade de 20 ns. A resistência das células ao desgaste chega a 1012. O tempo de retenção de dados é de apenas 1 segundo a uma temperatura de 110 graus Celsius. Isso não é adequado para memória de longo prazo, mas será suficiente para a memória cache. A economia no consumo ainda será significativa.

Exemplo de estrutura celular STT-MRAM

A peculiaridade da produção de memória STT-MRAM da Intel é que não mais do que três Máscaras fotográficas são suficientes para liberá-la. As células de memória baseadas nas junções do túnel magnético são feitas na camada de contato e não ocupam espaço no chip. Apenas os transistores que controlam as células estão localizados no chip – um transistor por célula. Tais matrizes escalam bem e são muito mais densas que a SRAM clássica de 6 transistores por célula.

.