O boato mais insistente dos últimos meses relacionado aos futuros processadores AMD pode ser considerado a transição dentro da estrutura da arquitetura Zen 3 de dois threads para o núcleo para quatro. Supunha-se que essa metamorfose seria benéfica no segmento de servidores, onde o desempenho é bem dimensionado com o aumento do número de núcleos. Enquanto isso, nesta semana no Reino Unido, a AMD Hart Martin Martin Hilgeman falou sobre os atuais e futuros processadores de servidores da empresa, expondo inconscientemente esse mito persistente.

Fonte da imagem: AMD, YouTube

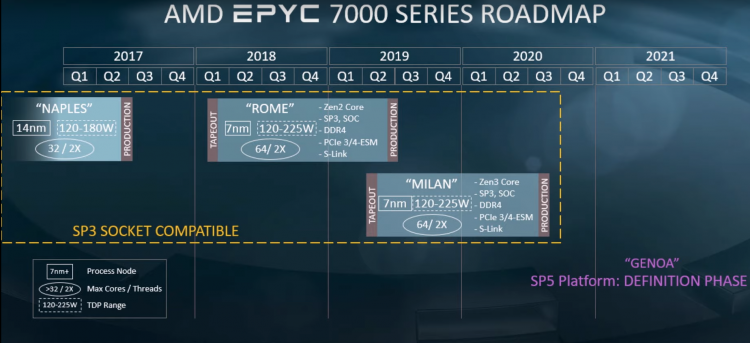

Para começar, a AMD descreve uma sequência de liberação clara para novos processadores de servidor. Projetos digitais de processadores com arquitetura Zen 3 já estão prontos, o que corresponde totalmente às declarações feitas recentemente sobre a conclusão do desenvolvimento de processadores da geração Milan. Eles serão produzidos no próximo ano, de acordo com a segunda geração da tecnologia de 7 nm nas instalações da TSMC, já usando a chamada litografia EUV. A julgar pelo slide da apresentação da AMD, a produção em massa dos processadores EPYC de Milão será lançada no terceiro trimestre de 2020.

Rastreado e continuidade no nível da plataforma. Os processadores Milan manterão a compatibilidade com o soquete SP3, fornecerão suporte para PCI Express 4.0 e DDR4. Em uma palavra, já vimos tudo isso enquanto estudamos as características dos processadores Rome que agora são oferecidos aos clientes da empresa. O valor limite do TDP permanecerá o mesmo – 225 watts, o número de núcleos (64 peças) não será alterado. O principal é que, para cada núcleo físico, ainda haverá mais de dois threads. Só podemos supor que a tecnologia de processo aprimorada permitirá à AMD aumentar as frequências dos processadores Milan em relação aos seus antecessores, e isso afetará favoravelmente o nível de desempenho.

Os processadores Genoa com arquitetura Zen 4 neste slide estão na fase de determinar as características e a funcionalidade, mas pelos comentários de Martin Hilgeman, fica claro que eles oferecerão suporte a um novo tipo de memória, além de receberem um novo soquete de processador Socket SP5. Tudo isso se encaixa na velha idéia de que em 2021 a AMD implementa suporte para DDR5 e PCI Express 5.0, mas para isso é necessário alterar o design dos processadores.

Fonte da imagem: AMD, YouTube

Revelações não menos importantes do representante da AMD tocaram os processadores de dispositivos com a arquitetura do Zen 3. Embora eles mantenham o layout com oito núcleos de processamento em um chip, eles se recusarão a dividir a memória cache do terceiro nível em dois segmentos de 16 MB. O cache de terceiro nível para os processadores Milan será unificado e todos os oito núcleos de processamento localizados no mesmo chip terão acesso igual a ele. A propósito, o volume do cache de terceiro nível é indicado na forma de um intervalo aberto – a partir de 32 MB ou mais; portanto, essa característica ainda não está limitada por quadros rígidos. O palestrante confirmou a intenção da AMD de apresentar os processadores de Milão no próximo ano com suas declarações, por isso resta apenas ter paciência na expectativa de seu anúncio. .