Antes da liberação das especificações finais do PCI Express 6.0, vários meses restantes, mas a versão final do rascunho, lançada há cerca de 5 meses, permite que os desenvolvedores de microcircuitos e outras empresas comecem a implementar a tecnologia avançada em seus produtos: novas funções não ser adicionado ou alterado. O Synopsys, por exemplo, já apresentou a primeira solução PCIe 6.0 IP no setor, que permite que os microcircuitos integrem a interface avançada em suas fichas de 5 nm.

O pacote IP do Syspy Designware IP para PCIe 6.0 inclui um controlador (com interface synepsys ou AXI AMM EMBA 5/4/3), interface física (phy) e blocos de verificação. A solução proposta por Synopsys permite que os microcircuitos adicionem o controlador e a interface física ao seu design de 5 nm e, em seguida, verifique se tudo funciona corretamente.

A mais recente interface interessada os desenvolvedores da AI e HPC, processadores gráficos, controladores SSD e outros produtos sensíveis à largura de banda e recebe retornos desses indicadores de largura de banda que podem fornecer a interface PCIE 6.0. Estamos falando de velocidade até 128 GB / s através da interface X16 em cada direção. Isso significa que na teoria, um dispositivo com suporte para PCIe 6.0 pode trocar 256 GB de dados em um segundo.

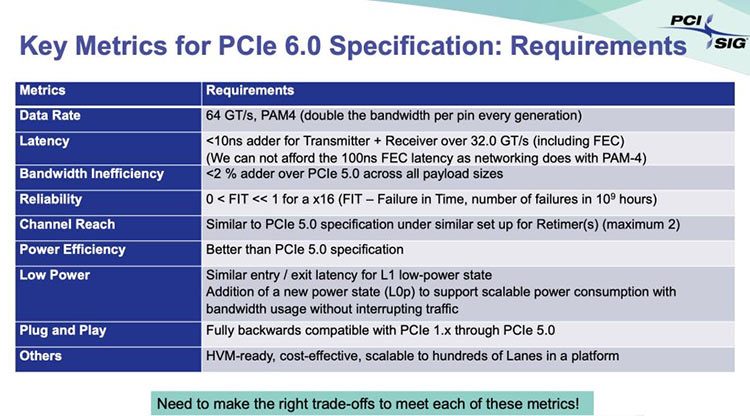

O controlador Synopsys PCIE 6.0 em total conformidade com o padrão aumenta a taxa de transferência de dados com até 64 gigatransacas por segundo versus 32 GT / C para PCIE 5.0 e 16 GT / C – para PCIE 4.0. A estrutura do sinal de interface em vez de transmitir a sequência de pulso sem retornar a zero (NRZ, no-retorno-a-zero) usa um circuito de transmissão com modulação de pulso de amplitude (PAM4). Para transmissão, a graduação do sinal com quatro níveis será usada, o que aumentará a densidade de dados e a capacidade do canal. Ao mesmo tempo, Synopsys argumenta que usa um canal de dados otimizado para fornecer atrasos ultra-baixos.

Outras características do PCIe 6.0 também são suportadas. Parece corrigir diretamente erros com um pequeno atraso (FEC), modo de flit e baixo modo de energia L0P são todos importantes inovações da função PCIE 6.0. Além disso, o controlador PCIE 6.0 do Sinopse Designware também suporta seus próprios algoritmos adaptativos DSP que otimizam a estabilização analógica e digital para reduzir o consumo de energia em 20% em interfaces entre chips, um riser e placa-mãe.

Nos últimos 1,5 anos, placas de vídeo, processadores e drives de estado sólido M.2 adquiriram suporte PCIE 4.0. Levará algum tempo antes de suportar o PCIe 5.0 em produtos avançados, mas é bom perceber que o PCI-Sig quase completou o desenvolvimento da próxima versão da interface. Hoje, no PCIe 6.0, é improvável que faça sentido no mercado consumidor, mas nos centros de data center, a largura de banda nunca é desnecessária. No entanto, anos depois, a PCIe 6.0 certamente chegará a usuários comuns.