Há muito se sabe que uma das razões para a atual escassez de aceleradores de computação avançados é a capacidade limitada da TSMC de testar e empacotar chips para eles usando a tecnologia CoWoS. Todas as instalações principais da empresa estão concentradas em Taiwan, mas agora a Reuters informa que a TSMC tem intenções de construir uma empresa semelhante no Japão.

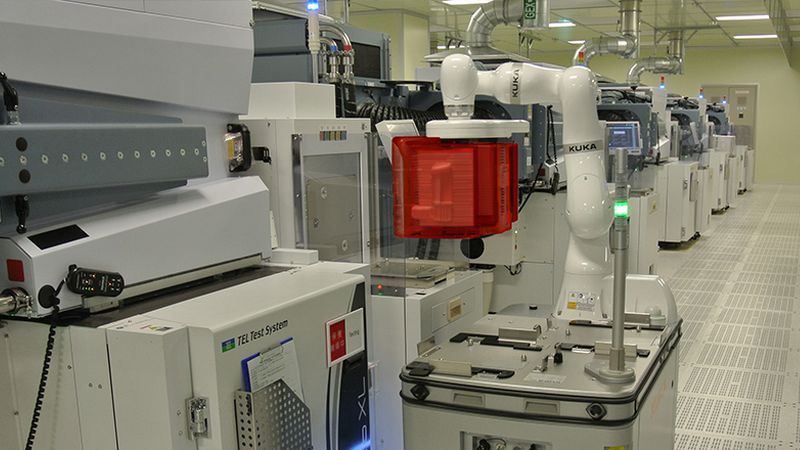

Fonte da imagem: TSMC

Lembremos que no Japão a TSMC já está implementando projetos para construir duas empresas que processam wafers de silício usando litografia, que é relativamente madura para os padrões de Taiwan, e seu centro de pesquisa para o uso de vários materiais promissores e métodos de empacotamento de chips está mais focado no interesses da própria TSMC, e não de parceiros japoneses entre fornecedores de materiais e equipamentos tecnológicos.

Uma instalação de embalagem de chips usando a técnica CoWoS provavelmente seria útil para um fabricante de chips no Japão que usa litografia avançada. Neste contexto, o principal beneficiário desta iniciativa parece ser o consórcio japonês Rapidus, que espera começar a produzir chips avançados de 2nm no Japão já em 2027. No entanto, ainda não há informações precisas sobre o cronograma de construção da discutida instalação de embalagem de chips da TSMC, nem sobre o orçamento para tal projeto. No momento, a maioria dos clientes da TSMC que necessitam de serviços de embalagem de chips usando o método CoWoS são empresas americanas, como explicam os especialistas da TrendForce.

A propósito, a Intel e a Samsung também vão usar as competências dos fabricantes japoneses de equipamentos e fornecedores de consumíveis em seu benefício. O primeiro estuda a possibilidade de construir um centro de investigação especializado no Japão e o segundo já chegou a um acordo adequado com parceiros locais. Lembramos que a TSMC já possui um centro de pesquisa desse tipo no Japão.