A Intel Foundry divulgou um relatório técnico detalhando as soluções avançadas de design e implementação de hardware da empresa para aplicações de IA e computação de alto desempenho. A Intel também apresentou uma “plataforma de teste de chips de IA” demonstrando as atuais capacidades de encapsulamento da empresa.

Fonte da imagem: Intel

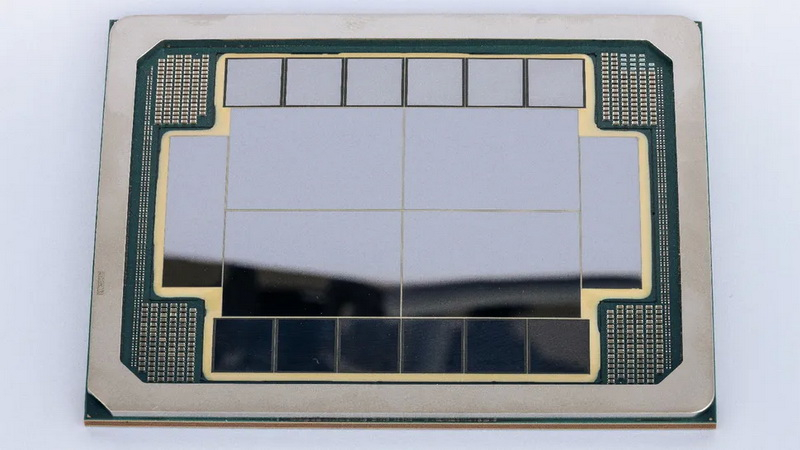

A Intel demonstrou um sistema em pacote (SiP) do tamanho de oito máscaras de chip padrão, composto por quatro blocos lógicos, 12 módulos HBM4 e dois blocos de E/S. Ao contrário do conceito em larga escala com 16 blocos lógicos e 24 módulos HBM5 apresentado pela empresa no mês passado, este sistema já está pronto para produção.

É importante notar que a Intel Foundry não demonstrou um acelerador de IA funcional, mas sim um “chip de teste de IA”, demonstrando como os futuros processadores de IA e computação de alto desempenho podem ser fisicamente criados (ou melhor, montados). A Intel está demonstrando um método de design completo que combina grandes blocos de computação, módulos de memória de alta velocidade, interconexões ultrarrápidas entre chips e novas tecnologias de energia em um único pacote de alto desempenho. Este pacote é significativamente diferente do que empresas como a TSMC oferecem atualmente. A Intel quer demonstrar que os processadores de próxima geração para IA de alto desempenho podem apresentar designs multichip, e a Intel Foundry já é capaz de produzi-los.

A plataforma apresentada é baseada em quatro grandes blocos lógicos, presumivelmente construídos no processo 18A da Intel (e, portanto, com transistores RibbonFET com estrutura gate-orbit e fonte de alimentação PowerVia para o backplane), circundados por stacks de memória HBM4 e blocos de E/S. Todos os elementos principais são presumivelmente conectados por pontes EMIB-T 2.5D integradas diretamente no substrato do encapsulamento. A Intel utiliza a tecnologia de interface interchip EMIB-T, que adiciona vias através do silício.As vias dentro das pontes permitem que a energia e os sinais fluam tanto vertical quanto horizontalmente, maximizando a densidade de interconexão e a entrega de energia. A plataforma foi projetada para interfaces chip-a-chip UCIe operando a 32 GT/s e superiores, que também são presumivelmente usadas para conectar stacks C-HBM4E.

A amostra de teste do chip também demonstra a mudança da Intel para a embalagem vertical. O roteiro de processos da empresa inclui a tecnologia Intel 18A-PT, projetada especificamente para chiplets que exigem que outros chips lógicos ou memória sejam empilhados sobre eles. Consequentemente, os chiplets devem ter fornecimento de energia pela parte traseira e utilizar interconexões híbridas e de furo passante. No caso da “amostra de teste do processador de IA”, os chips base 18A-PT são posicionados abaixo dos chips de computação 18A/18A-P e atuam como grandes chips de memória cache ou executam outras funções de suporte. Para conectar os chiplets verticalmente, a Intel utiliza a família de tecnologias de embalagem Foveros — Foveros 2.5D, Foveros-R e Foveros Direct 3D. Essas tecnologias permitem interconexões de cobre de passo fino entre os chips ativos para garantir o máximo desempenho e eficiência energética nos chips superiores. Juntamente com as pontes EMIB, essas técnicas permitem que a Intel crie uma montagem híbrida lateral-vertical, que a empresa posiciona como uma alternativa aos grandes interposers de silício, com maior utilização e rendimento do wafer.

Para aceleradores de IA e HPC com múltiplos chips, a potência é a principal restrição de projeto. Para atingir esse objetivo, a plataforma Intel deve integrar todas as inovações mais recentes da Intel em economia de energia, incluindo PowerVia, capacitores integrados Omni MIM, desacoplamento em nível de ponte em EMIB-T, capacitores eDTC e eMIM-T no chip base e indutores CoaxMIL integrados para suportar reguladores de tensão semi-integrados (IVRs) localizados no chip.Sob cada pilha e sob o próprio pacote (diferentemente do IVR no caso do CoWoS-L da TSMC, que faz parte do interposer). Essa rede multicamadas foi projetada para manter uma corrente estável em cargas de trabalho de IA generativa sem limitação de desempenho.

Com essa demonstração, a Intel está claramente tentando atrair clientes. Atualmente, não se sabe se o acelerador de IA de próxima geração, codinome Jaguar Shores, com lançamento previsto para 2027, utilizará a arquitetura que a Intel está demonstrando hoje.