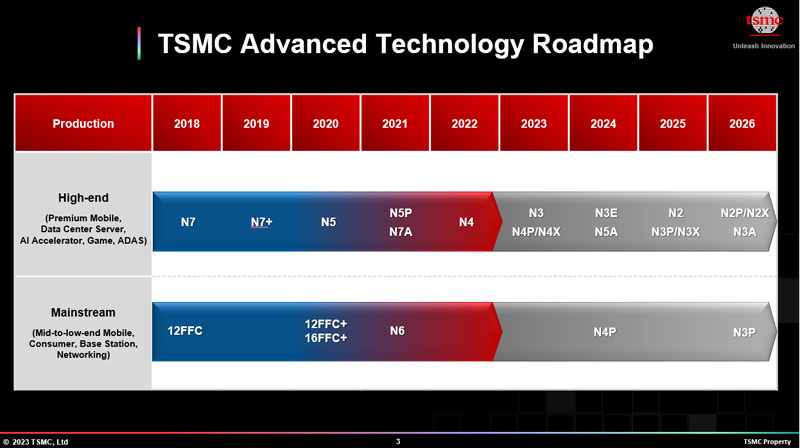

A TSMC revelou planos para melhorar a tecnologia de processo de 2 nm N2, que deve iniciar a produção em massa em 2025. Um ano depois, o processo N2P otimizado para power rail será introduzido e, algum tempo depois, a empresa lançará o processo N2X para soluções de alto desempenho. O desenvolvimento do processo de 2 nm da TSMC será rápido, o que pode ser devido aos temores da TSMC de ficar para trás da Intel e da Samsung.

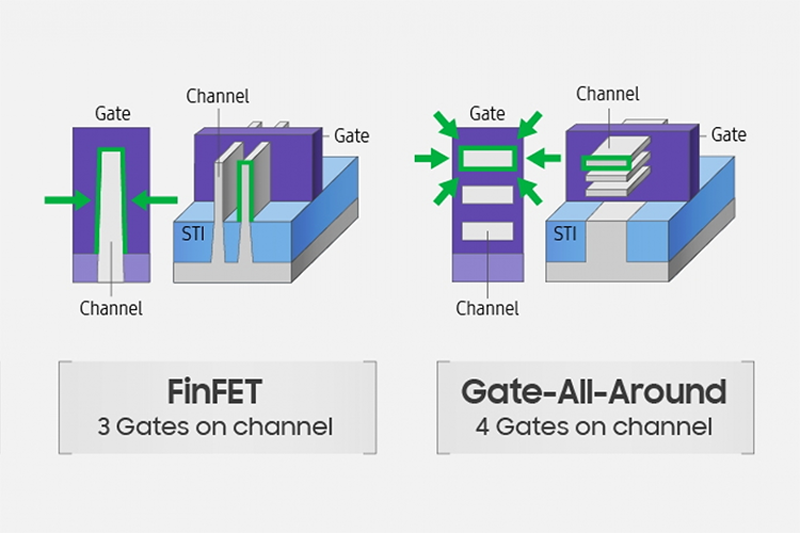

Um exemplo de transistores com nervuras verticais e uma porta circular (à direita). Fonte da imagem: Samsung

A fabricante de chips taiwanesa apresentou oficialmente o processo técnico com padrões de 2 nm no verão passado. A produção de semicondutores com esses padrões tecnológicos começará em 2025. A principal característica da tecnologia de processo N2 será a transição de FinFET para transistores de porta circular (GAAFET). Isso reduzirá as correntes de fuga, permitirá um ajuste flexível do desempenho e otimizará o consumo. Outra característica importante da tecnologia de processo N2 era mover as linhas de energia do chip para o outro lado do chip, o que significaria desacoplar o barramento de dados e controle da energia.

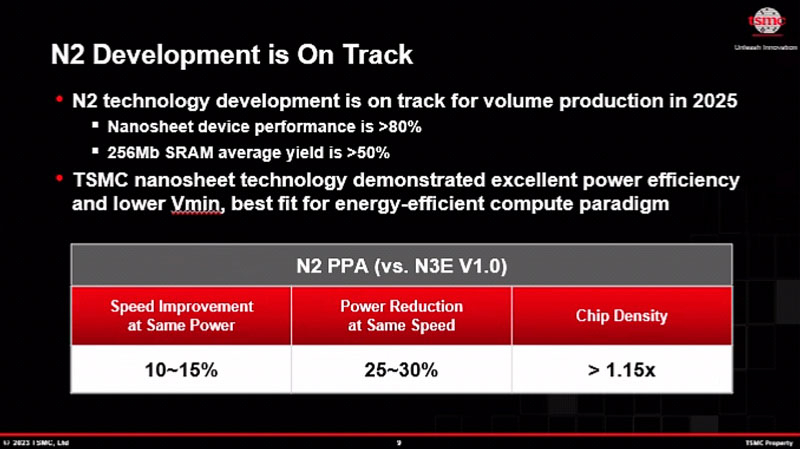

Fonte da imagem: TSMC

Como já está ficando claro, a transferência de linhas de energia é esperada durante a implementação do processo N2P, que ocorrerá em 2026. Pelas declarações anteriores da empresa, a primeira implementação da ideia poderia ser esperada em 2025. O espaçamento das interfaces de energia e dados em lados diferentes da matriz resolve muitos problemas. Assim, as linhas de alimentação dos transistores ficarão mais curtas, o que reduzirá sua resistência. O espaçamento da fiação reduzirá a área dos cristais, cuja maior parte foi consumida por linhas de transmissão e contatos intermediários. Finalmente, embora isso não seja tudo, a interferência mútua diminuirá, o que afetará a estabilidade das características do sinal dos chips.

A redução da área do cristal ocupada pelos contatos e fiação levará a um aumento significativo na densidade dos transistores. A TSMC afirmou anteriormente que a mudança de um processo de 3 nm para um processo de 2 nm aumentará a densidade do transistor em 10%. Até o momento, a previsão foi aprimorada para 15% e, no caso da implementação da tecnologia de processo N2P, a densidade pode aumentar em um valor de dois dígitos, o que a empresa ainda não especificou. A Lei de Moore respirará mais uma vez antes de morrer.

A empresa não disse nada sobre a tecnologia de processo N2X, que será implementada em 2026 ou posteriormente. Podemos supor que essa não será uma proposta muito comum, enquanto o processo N2P promete ser o carro-chefe da empresa na fase de produção de chips de 2nm.

A empresa também anunciou o progresso na preparação da tecnologia básica de processo de 2 nm. O desempenho dos transistores GAAFET na composição do silício experimental atinge 80% dos valores alvo. E isso é dois anos antes do início da implementação, o que é muito, muito bom. Ao mesmo tempo, o nível de refugo na produção de células SRAM de 2 nm com volume de 256 Mb diminuiu para 50% ou menos.

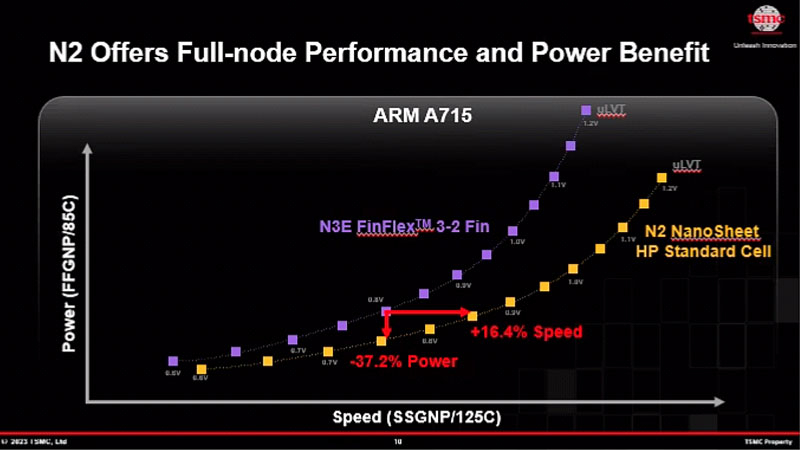

Fonte da imagem: Anandtech See More

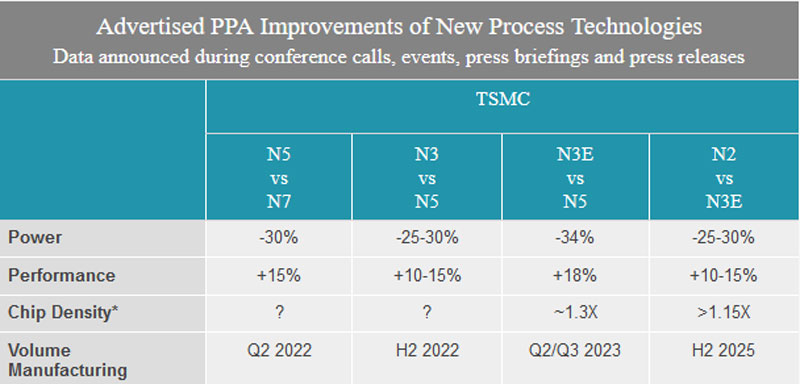

Em geral, o processo de 2 nm permitirá que o TSMC melhore o desempenho do transistor em 10-15% para a mesma potência e complexidade ou reduza o consumo de energia em 25-30% para as mesmas velocidades de clock e número de transistores. No papel, a TSMC está um ou dois anos atrás da Intel, e o sucesso de uma empresa assombra a outra. Se cada um deles cumprir suas promessas, os chips TSMC com transistores GAAFET aparecerão dois anos depois dos chips Intel semelhantes (20A), o que também diz respeito aos planos de mover as linhas de energia para a parte traseira do chip.