A TSMC confirmou planos de transição para novas tecnologias de processo, transistores e tecnologias. Em um documento distribuído pela empresa, ela começará a produzir chips com tecnologia de processo de 2 nm em 2025 e, ao mesmo tempo, abandonará os canais de transistor FinFET dispostos verticalmente em favor de canais dispostos horizontalmente na forma de nanopáginas. A lei de Moore terá que ser esquecida por um tempo, mas a eficiência energética dos chips aumentará significativamente.

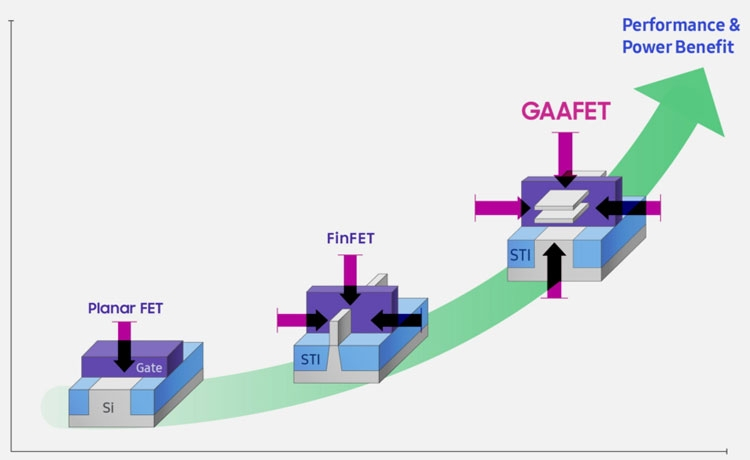

A evolução dos transistores. Fonte da imagem: Samsung

A TSMC de Taiwan está atrasada em relação à Samsung em termos de transição para os novos transistores de porta circular GAAFET (Gate All Around) (nanopage). Em si, este é um evento arriscado – a transição para uma nova estrutura de transistor. A Samsung planeja começar a fabricar chips com canais de transistor nanopage no final deste ano como parte da tecnologia de processo de 3nm. É interessante notar que com a nova liderança da Intel na pessoa de Patrick Gelsinger, a gigante dos microprocessadores também prometeu forçar a transição para novos transistores GAAFET (na empresa essa tecnologia é chamada de RibbonFET) e espera fazer isso por volta de 2024 ou um ano à frente da TSMC.

Canais de transistor na forma de nanofolhas (nanofolha) são quase as mesmas “bordas” FinFET, apenas localizadas paralelamente ao substrato de cristal, enquanto os FinFETs são criados perpendicularmente ao substrato. Também resulta do arranjo das nanopáginas que as portas, o material pelo qual as páginas penetram desde a fonte até o dreno do transistor, cercam os canais de nanopágina de todos os quatro lados. Uma maior área de contato e um maior número de canais nanopage permitem aumentar as correntes através do canal do transistor GAAFET e melhorar sua controlabilidade.

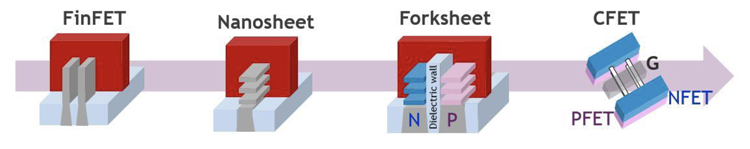

Fonte da imagem: TSMC

Além disso, uma propriedade importante das nanopáginas é o ajuste mais fino dos transistores às tarefas do chip, o que leva a um aumento acentuado da eficiência energética das soluções. Você pode alterar o número de páginas (canais) e sua largura: faça transistores com nanopáginas mais largas para chips de alto desempenho e mais estreitos para os de eficiência energética.

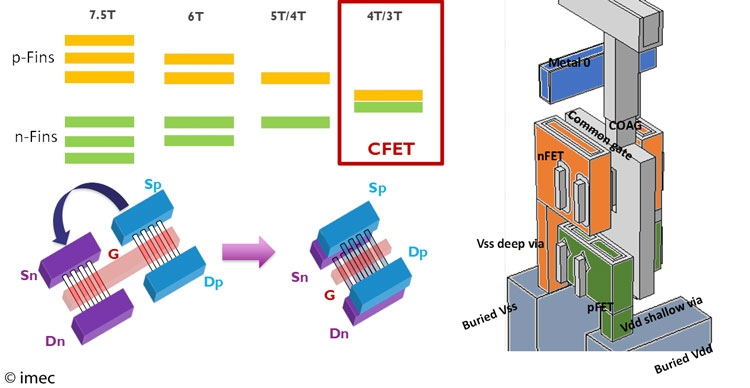

É interessante notar que a TSMC também decidiu, embora não seja a escolha final, com o próximo design de transistor após os transistores de nanopágina de 2 nm. Após as nanopáginas, a empresa espera começar a fabricar chips com transistores CFET (veja a figura abaixo). Ao mesmo tempo, também falamos sobre isso. Um dos desenvolvedores de transistores CFET ou FETs complementares é o centro belga Imec. Os transistores CFET consistem em um par de transistores de efeito de campo complementares do tipo n e p, mas estão localizados um acima do outro, o que permite, grosso modo, dobrar a densidade de transistores em um chip.

Fonte da imagem: Imec

«Este [CFET] ainda está em fase de pesquisa”, disse o chefe do TSMC em entrevista ao EE Times. – Esta é apenas uma das opções para o transistor. Eu não acho que posso dar uma linha do tempo para quando essa tecnologia de transistor entrará em produção.”

Voltando ao processo de 2 nm, a TSMC espera que o processo de 3 nm tenha uma longa vida com transistores FinFET convencionais antes de ser introduzido. Haverá pelo menos três anos entre esses processos técnicos, mas mesmo após o início da produção de chips de 2nm, a empresa espera continuar produzindo soluções de 3nm por um longo tempo – elas serão confiáveis e testadas ao longo do tempo.