A Samsung anunciou um protótipo de matriz SRAM de 256 Mbit usando tecnologia de processo 3nm e novos transistores MBCFET avançados. A amostra permitiu comprovar as características do futuro processo técnico. Assim, a Samsung passou da teoria à prática e pode-se esperar que lance a produção de semicondutores de 3 nm já no próximo ano.

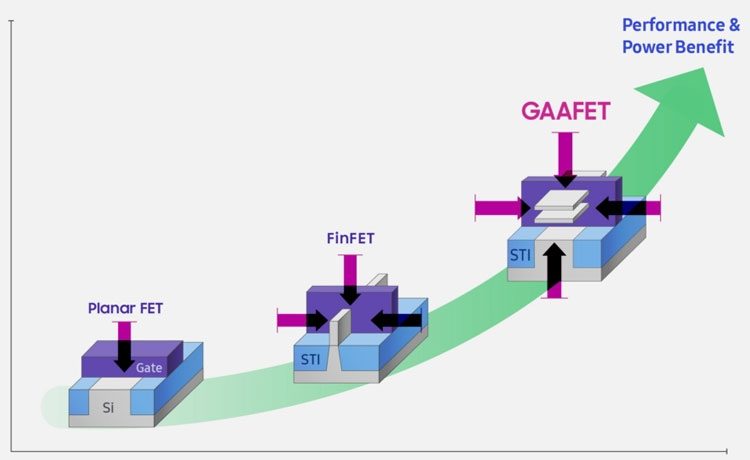

Evolução dos transistores. Fonte da imagem: Samsung

Deve-se dizer que a abreviatura MBCFET (multi-bridge channel FET) em nome de um novo tipo de transistor é uma marca registrada da Samsung. Em um sentido amplo, esses são os chamados transistores GAAFET com um anel ou porta que abrange tudo, quando um canal ou vários canais de um transistor são cercados por uma porta em todos os quatro lados.

Este conceito foi apresentado em 1988 e tem sido bem estudado teoricamente, mas o motivo para mudar para esta estrutura apareceu apenas agora, uma vez que os transistores FinFET clássicos com aletas verticais deixaram de funcionar normalmente com padrões tecnológicos inferiores a 5 nm. No caso de um novo aumento na produtividade e uma diminuição no consumo com uma diminuição simultânea no tamanho físico dos transistores (no processo de redução dos padrões tecnológicos), torna-se mais difícil controlar os canais dos transistores. Portanto, aumentar a área de contato entre o gate e o canal devido à cobertura total do canal é uma saída simples desta situação, que, o que é muito importante, permite a produção de novos transistores no mesmo equipamento.

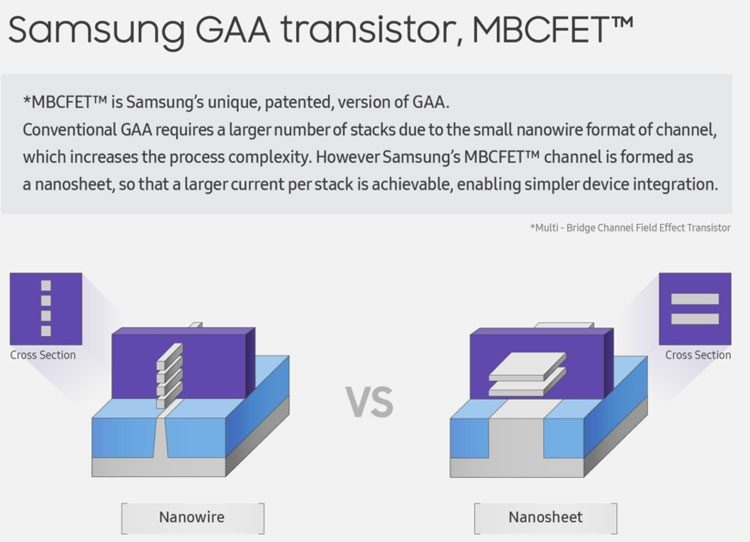

Fonte da imagem: Samsung

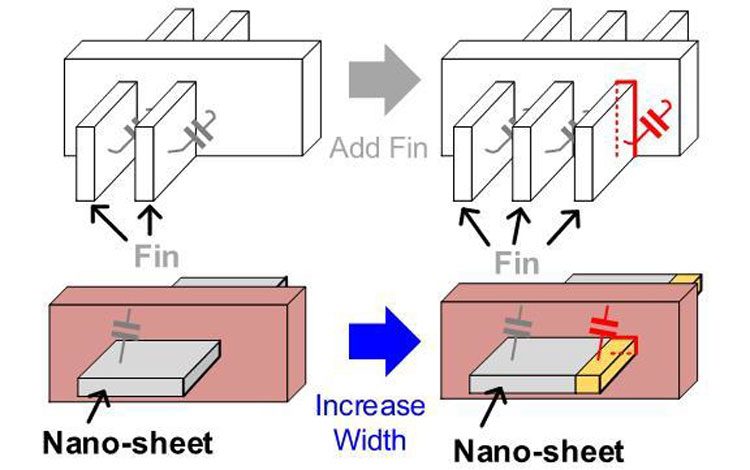

Acrescentemos que uma inovação importante na produção de chips em transistores MBCFET (GAAFET) será a capacidade de definir a largura dos canais nano-página, bem como seu número em cada transistor, para cada caso individual. Por exemplo, para uma lógica mais eficiente, a largura das nano páginas pode ser aumentada, e para blocos com baixo consumo, ela pode ser reduzida.

Além disso, é possível projetar com tanta flexibilidade que mesmo em uma única célula de unidade SRAM de seis transistores, parte dos transistores pode ser criada com canais nano-canais largos e alguns com canais estreitos. Isso é exatamente o que a Samsung demonstrou com seu protótipo de matriz SRAM 256Mbit 3nm. As medições mostraram que mudar para uma célula com transistores mistos do nada reduziu a tensão de gravação em 256 mV.

Controlar a largura dos canais de nanopágina é mais fácil do que adicionar novas bordas em FinFETs. Fonte da imagem: Samsung

Por fim, a empresa provou sua capacidade de atingir novos níveis de produtividade e eficiência. Assim, em comparação com a tecnologia de processo 7nm 7LPP, a velocidade de operação dos transistores MBCFET de 3nm cresceu para 30% (com o mesmo nível de consumo e complexidade), e quando operando nas mesmas frequências e mesma complexidade, o consumo diminuiu a 50%. O aumento na densidade dos transistores no circuito misto (SRAM mais lógica) foi de até 80%.