A Taiwan Semiconductor Manufacturing (TSMC), maior fabricante terceirizada de chips do mundo, está explorando o uso de wafers de silício retangulares em vez dos tradicionais redondos na produção de chips. Isto aumentará o número de chips colocados em um wafer. Anteriormente, a TSMC considerava esta uma tarefa muito difícil, mas as crescentes demandas quase horárias dos clientes por chips de IA estão forçando-os a otimizar a produção.

Fonte da imagem: Cheng Ting-Fang/Nikkei Ásia

O wafer retangular de 510 x 515 mm atualmente em teste tem mais de 3 vezes a área útil dos wafers redondos de 300 mm. O formato retangular também significa menos área desperdiçada nas bordas. No entanto, a comercialização da nova abordagem poderá levar vários anos, e a TSMC e os seus fornecedores terão de atualizar ou mesmo substituir muitos equipamentos e materiais de produção, relata o Nikkei Asia.

A necessidade de mudar para um novo formato de wafer é ditada pelo fato de que os chips modernos de alto desempenho exigem cada vez mais cristais. Devido ao arranjo espacial, é possível colocar muitos cristais sob uma tampa. Por exemplo, de um wafer de 300 mm você pode obter apenas 16 conjuntos de cristais para o acelerador do carro-chefe Nvidia B200, e isso está sujeito à completa ausência de defeitos.

A transição para um novo formato exigirá esforços e investimentos significativos. Em particular, é necessário modificar sistemas de deposição fotorresistente, manipuladores robóticos e outros equipamentos para trabalhar com substratos de diferentes formatos. A comercialização total da tecnologia levará pelo menos 5 a 10 anos.

Observe que a TSMC não é a única empresa que estuda tecnologia para produção de chips em painéis retangulares. Desenvolvimentos semelhantes estão em andamento na Intel, Samsung e em diversas outras empresas do setor. No entanto, a TSMC é o maior fabricante de chips avançados para inteligência artificial e por isso os seus passos nesta direção são de particular importância.

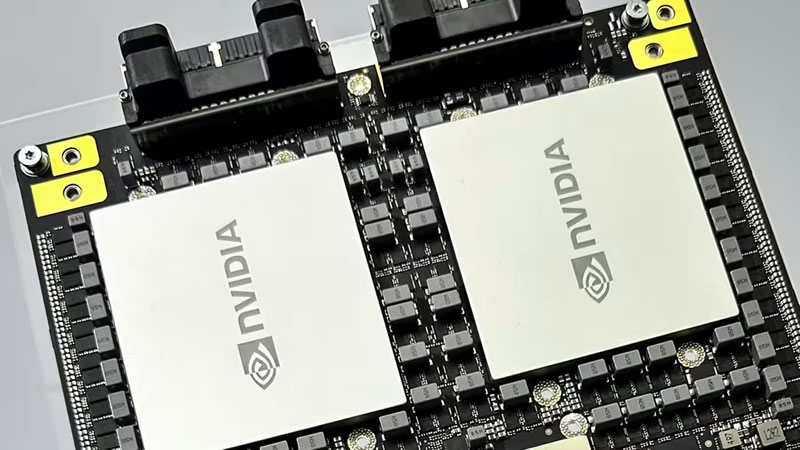

As tecnologias de empacotamento de chips também são muito importantes para o desenvolvimento da indústria de semicondutores. Em particular, chips AI como Nvidia H200 e B200 não requerem tecnologia de processo avançada e também exigem a tecnologia de empacotamento CoWoS da TSMC para combinar múltiplas matrizes, bem como memória HBM. Por exemplo, na Nvidia B200, a tecnologia CoWoS permite que duas GPUs Blackwell sejam combinadas e emparelhadas com oito pilhas de memória HBM, proporcionando melhor desempenho computacional.

«