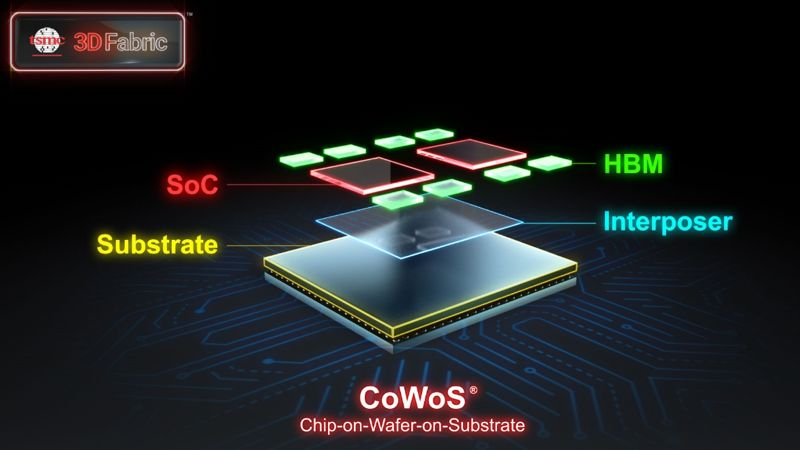

Para o segmento de aceleradores computacionais utilizados como parte de sistemas de inteligência artificial, a capacidade da TSMC de empacotar um número suficiente de chips utilizando o método CoWoS é de grande importância, já que no caso da produção de soluções a Nvidia continua sendo um gargalo. O fabricante taiwanês pretende expandir ativamente a sua capacidade principal não apenas no próximo ano, mas também em 2026.

Fonte da imagem: TSMC

No mínimo, o CEO e presidente da TSMC, C.C. Wei, explicou que as capacidades de empacotamento de chips CoWoS da empresa mais que duplicarão este ano em comparação com o ano passado, e também poderão duplicar no próximo ano. É possível, segundo o responsável da empresa, que mesmo este ritmo de expansão não seja suficiente para satisfazer a procura pelos serviços essenciais da TSMC.

Se falarmos sobre a economia do processo, a TSMC agora não recebe mais do que 10% de sua receita no fornecimento de serviços de embalagem de chips e, nos próximos cinco anos, esse segmento crescerá mais rápido do que outras áreas de atividade da empresa. Até o momento não conseguiu atingir os indicadores médios de todos os segmentos em termos de margens de lucro, mas a diferença já não é tão grande. A TSMC estima que sua participação no mercado global de serviços de embalagem de chips seja de aproximadamente 30%.

De acordo com Money DJ, a TSMC já fez pedidos dos equipamentos necessários para embalar os chips até 2026 inclusive. Se até o final deste ano a TSMC puder processar 40.000 wafers de silício por mês em termos equivalentes na direção de embalagem de chips usando o método CoWoS, no próximo ano o volume dobrará para 80.000 peças por mês. Até 2026, o ritmo de expansão poderá desacelerar, variando de 100 a 120 mil wafers por mês. Porém, se houver demanda, esses números podem facilmente aumentar para 140 ou 150 mil wafers por mês.