No evento Elbrus Tech Day, MSCT falou sobre as conquistas e planos atuais para o desenvolvimento de uma série de processadores Elbrus russos. Agora, a CPU mais moderna desta linha é o Elbrus-8SV baseado na arquitetura E2K de quinta geração (Elbrus 2000), mas nos próximos anos, três SoCs de sexta geração aparecerão de uma vez: Elbrus-16S, Elbrus-2S3 e Elbrus -12S.

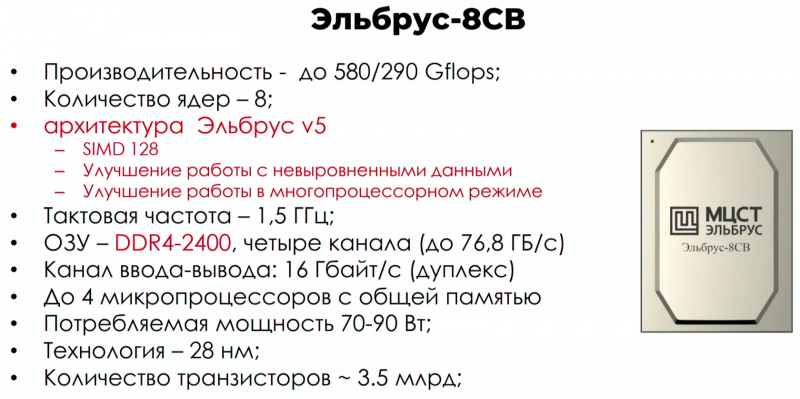

Elbrus-8SV é um desenvolvimento evolutivo do Elbrus-8. Ambos os chips usam uma tecnologia de processo de 28nm, mas devido às otimizações em 8CB, eles conseguiram aumentar a frequência, o que, junto com o suporte para instruções de vetor amplo e um padrão de memória mais moderno, deu um aumento de duas vezes no desempenho de pico teórico. Porém, para programas que não usam SIMD, o ganho é proporcional ao aumento da frequência do clock + eles ainda se beneficiam do aumento da velocidade da memória.

Com base nesses e em outros processadores, a MCST desenvolve designs de referência de placas-mãe de vários formatos que podem ser licenciados para personalização posterior. Alguns dos parceiros da empresa desenvolvem suas próprias placas-mãe e produtos baseados nelas. Em breve, a TSMC fará um pedido para a produção do próximo lote do Elbrus-8SV com volume de 10 mil peças. Em geral, um ecossistema bastante perceptível de produtos e soluções de hardware e software foi desenvolvido em torno das CPUs existentes.

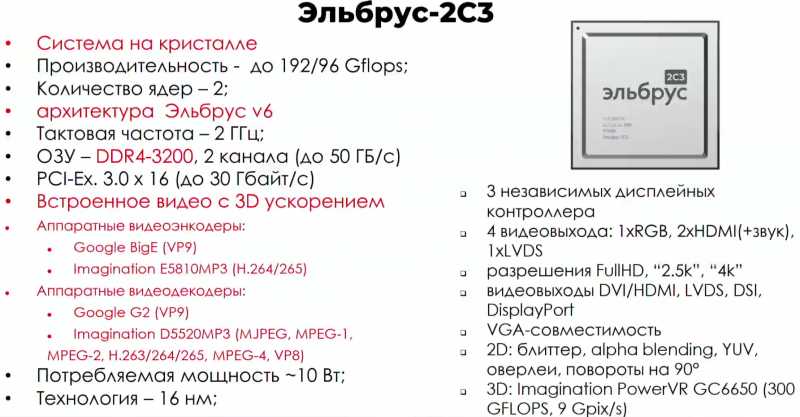

A próxima geração de processadores será mais diversificada. Além do Elbrus-16S de 16 núcleos, voltado para sistemas de servidores de alto desempenho, haverá um modelo mais simples que aparecerá depois dos demais – o Elbrus-12S. Esta CPU de 12 núcleos foi projetada para servidores de nível básico e também para estações de trabalho. E a principal diferença do 16C está no preço. Por fim, outro chip, o Elbrus-2S3 dual-core, é voltado para sistemas móveis, incluindo tablets.

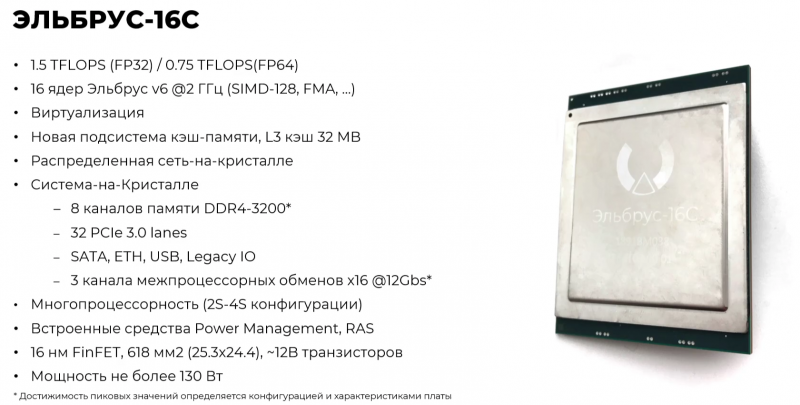

Elbrus-16S

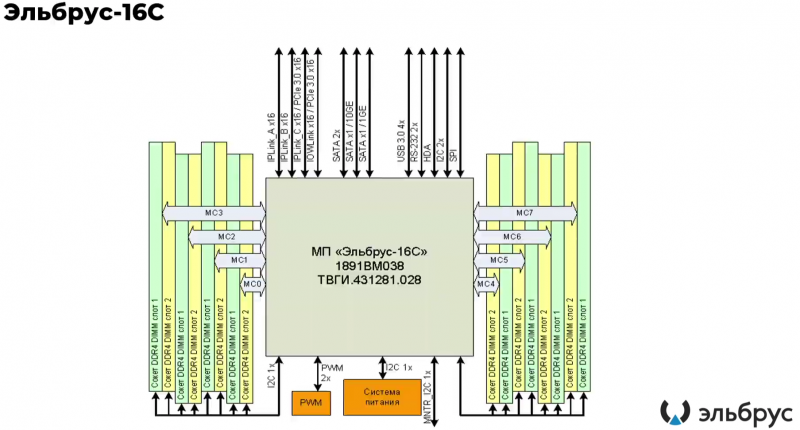

Todos os chips serão fabricados pela TSMC usando a tecnologia FinFET de 16 nm e serão baseados na sexta geração da arquitetura E2K. A rigor, esses não são mais processadores, mas SoCs completos com controladores integrados para vários periféricos e não precisam de um chip ponte sul externo para funcionar, como antes. No caso do Elbrus-16S, a área cristalina é de 618 mm2 (25,3 × 24,4 mm), é embalado em embalagem HFCBGA4804 com dimensões de 63 × 78 mm. O cristal contém 12 bilhões de transistores e sua potência não excede 130 W.

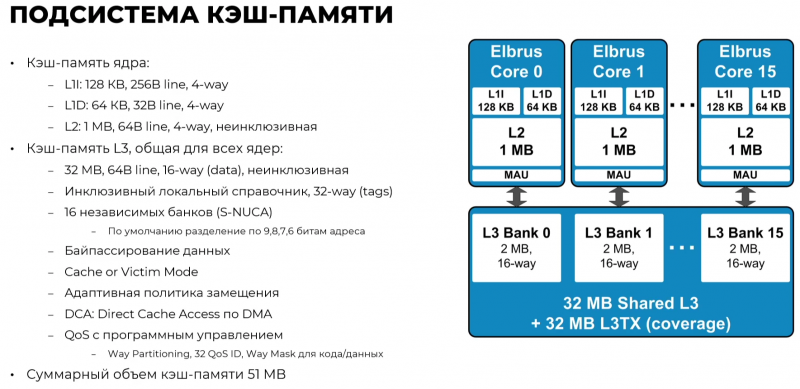

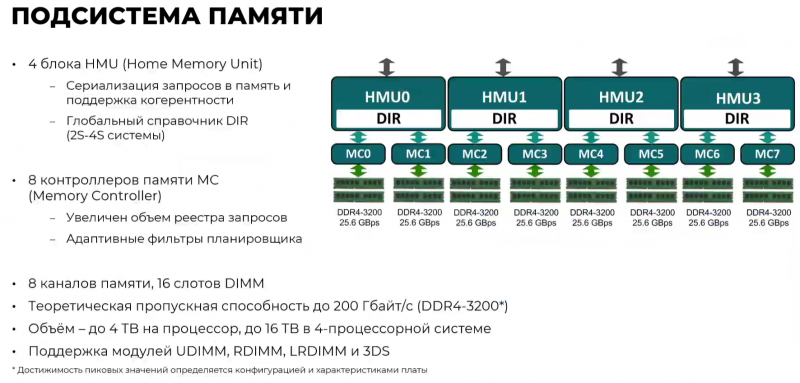

Uma parte significativa das mudanças na arquitetura afetou o subsistema de memória. Em particular, os tamanhos dos caches foram aumentados, o volume total dos quais atingiu 51 MB: o cache L3 total para todos os 32 MB, o cache L2 aumentou para 1 MB, o cache L1 para instruções em 128 KB + cache de dados L1 por 64 KB. O controlador de memória passou a ser de oito canais, recebeu suporte para módulos DDR4-3200 e 2DPC, o que dá até 4 TB de RAM por soquete com uma largura de banda total de até 200 GB / s.

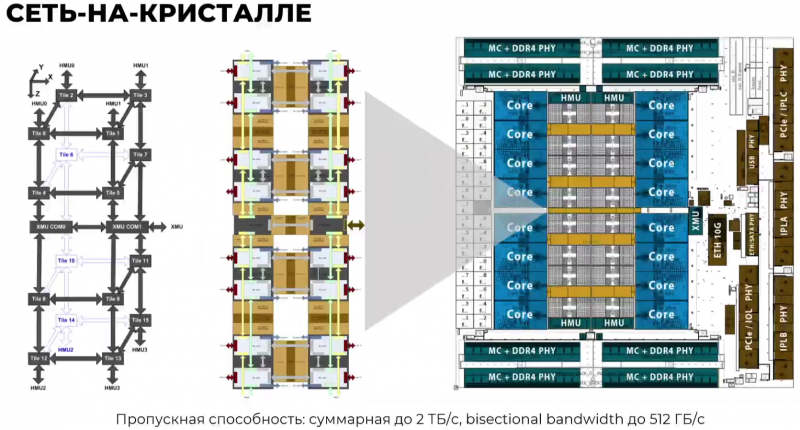

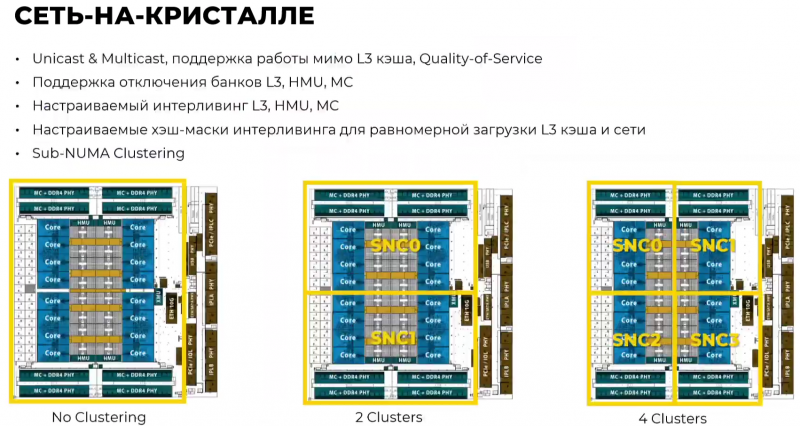

As primeiras amostras de engenharia do Elbrus-16S, obtidas no final do ano passado, já mostram uma velocidade de cerca de 70-80% do máximo possível no benchmark do fluxo. Os controladores são conectados em pares a quatro agentes (HMU), “conectados” a um barramento mesh interno com largura de banda de 2 TB / s, que combina memória e núcleos. O chip pode ser dividido em dois ou quatro domínios NUMA, o que é útil para várias tarefas.

Uma dessas tarefas é a virtualização, e no Elbrus-16C ela finalmente se tornou completa – os novos processadores suportam a virtualização de hardware de quase todos os recursos importantes, incluindo o modo de tradução x86, que também não chegou a lugar nenhum. Para CPUs de gerações anteriores, a conteinerização ainda pode ser usada, mas o MCST também está preparando um kernel paravirtualizado e componentes relacionados, incluindo KVM, QEMU, libvirt e virt-manager.

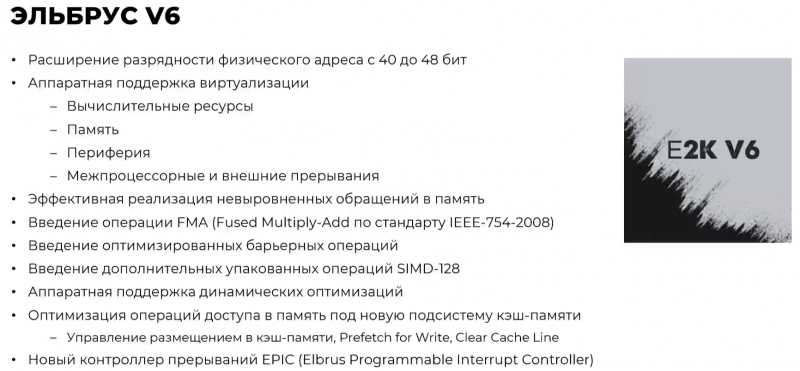

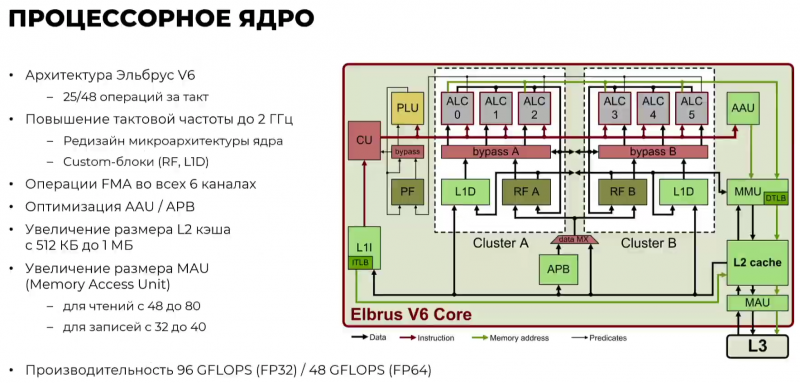

Para os próprios núcleos, a microarquitetura foi redesenhada, o que deu um aumento na velocidade de trabalho e novas oportunidades. Em particular, novas instruções SIMD surgiram além das existentes, suporte para FMA de acordo com o padrão IEEE 754-2008 (exigido nos padrões C modernos), otimização dinâmica (referente ao agendamento, que é importante para VLIW), um novo controlador de interrupção (necessário para virtualização) e etc.

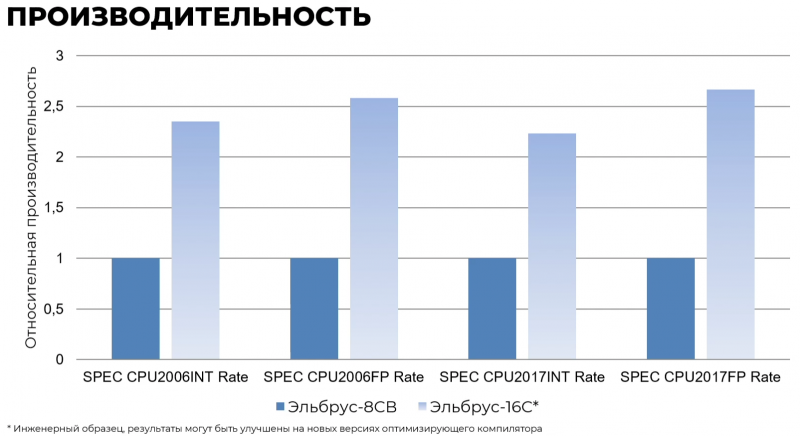

O desempenho teórico de pico do núcleo é 96 Gflops para cálculos de precisão simples e 48 Gflops para cálculos de precisão dupla. Para a CPU inteira, isso é 1,5 teraflops e 768 Gflops, respectivamente. Os testes preliminares mostram um aumento de desempenho de 2 a 2,5 vezes em comparação com o Elbrus-8SV, mas devemos lembrar que depende muito das otimizações do compilador. O kernel em si, embora tenha se tornado mais complexo, ainda é mais simples do que os kernels dos processadores x86-64 modernos.

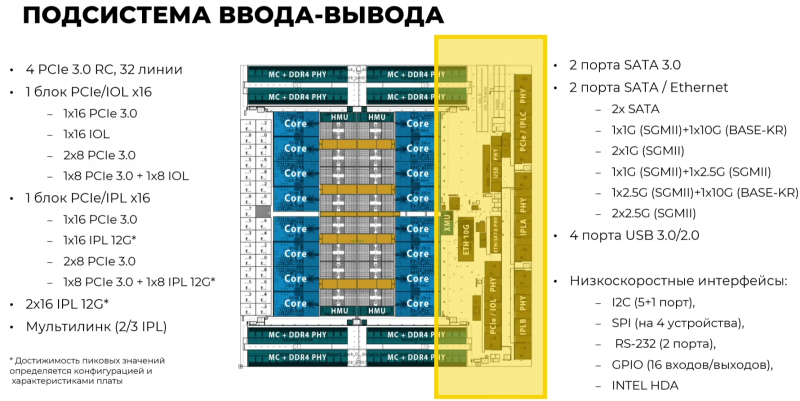

O ponto fraco dos novos chips, em nossa opinião, é o bloco IO. O SoC inclui quatro complexos de raiz PCIe 3.0 para um total de 32 pistas. Destes, 8 ou 16 linhas podem ser alocadas para conectar uma ponte sul externa, se não houver o suficiente do que está embutido no próprio chip. Ele oferece 2 portas SATA 3.0, 4 portas USB 3.0 / 2.0 e duas portas múltiplas fornecendo um par SATA ou par Ethernet com uma configuração máxima de 10GbE + 2,5GbE.

Outras 8 pistas PCIe podem ser fornecidas por canal de comunicação interprocessador (IPL), além das duas sempre presentes. Em um sistema de dois soquetes, é possível conectar as CPUs com dois ou três IPLs. É verdade que a velocidade de um desses canais é de apenas 12 Gb / s (nas amostras de engenharia, eles chegaram até agora a 10 Gb / s), o que é muito menor do que o UPI ou o Infinity Fabric. No total, até quatro processadores podem ser combinados em um sistema.

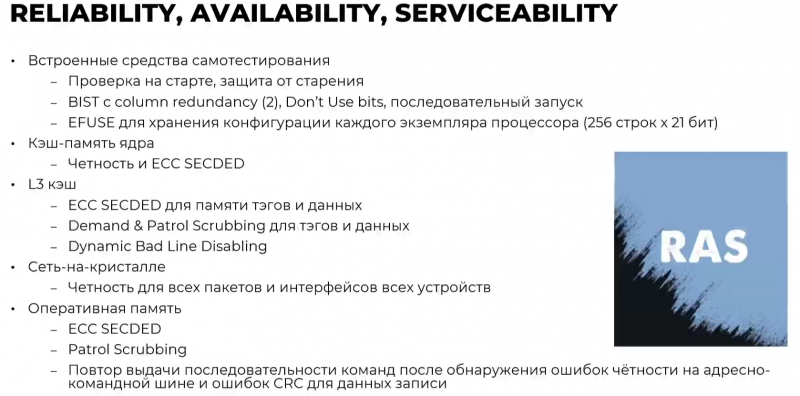

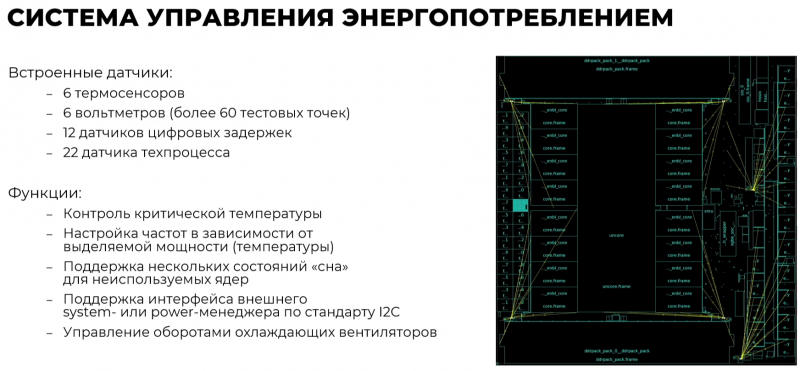

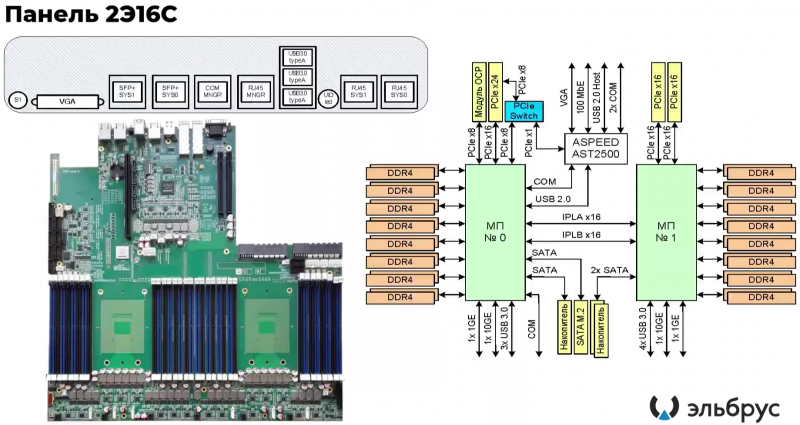

Entre outras coisas, os chips são equipados com várias funções RAS para melhorar a confiabilidade operacional. Também melhorou o monitoramento do processador e seu gerenciamento de energia e refrigeração. Provavelmente, agora todos os sistemas baseados em novas CPUs serão equipados com um controlador BMC – ASPEED AST2500 e, no futuro, AST2600 – com firmware próprio baseado em OpenBMC e com micro-OS embutido que simplifica a inicialização e o trabalho com os equipamentos. O design de referência da placa 2E16C-SPRC de dois soquetes aparecerá no meio deste ano, e a placa Micro-ATX de processador único – no final.

Em 2022, outras variantes de sistemas de dois e quatro soquetes com Elbrus-16S aparecerão, bem como placas de um e dois soquetes para Elbrus-12S. Presumivelmente, os parceiros do MCST também não ficarão ociosos. Lembre-se de que a conclusão formal do desenvolvimento do Elbrus-16S está programada para o final deste ano. Para Elbrus-2S3 e Elbrus-12S, as datas exatas não foram anunciadas. E se o modelo de 12 núcleos é provavelmente muito semelhante ao de 16 núcleos, então o chip júnior da série difere visivelmente deles.

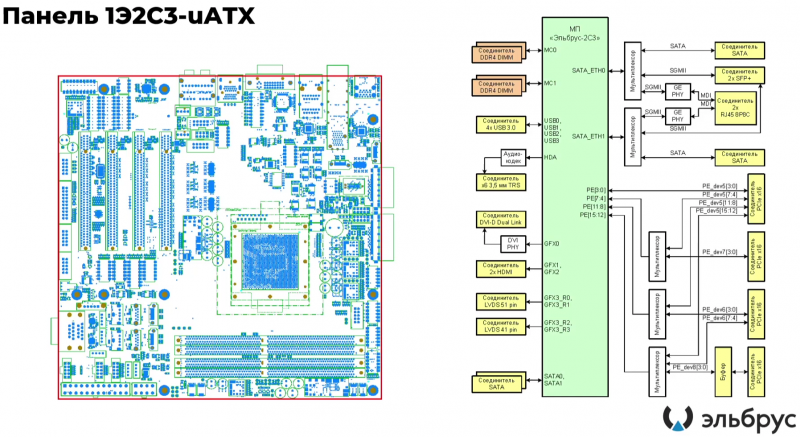

O Elbrus-2S3 possui apenas dois núcleos de sexta geração com freqüência de clock de 2 GHz, dois canais de memória DDR4-3200 e desempenho de até 192/96 Gflops FP32 / FP64. Possui 16 pistas PCIe 3.0. Inclui um núcleo 3D Imagination PowerVR GX6650 (300 Gflops), vários (des) codificadores de vídeo, bem como um núcleo 2D de seu próprio projeto. Existem quatro saídas de vídeo (das quais 2 são HDMI) e suporte para saída 4K. Para este SoC, a empresa irá preparar as primeiras placas Micro-ATX e Mini-ITX durante 2021.

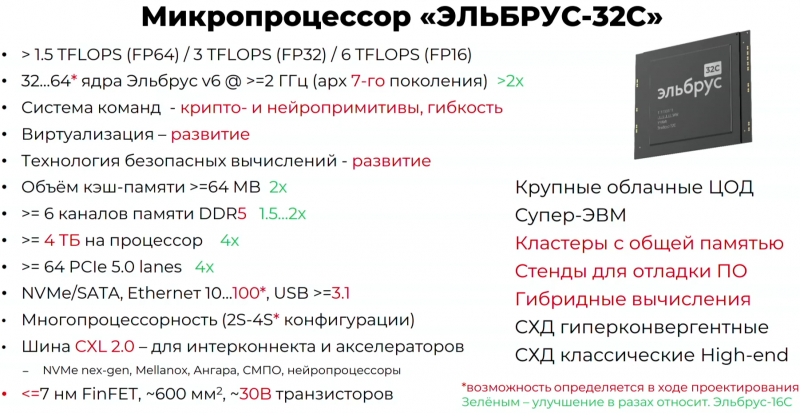

As características dos futuros processadores Elbrus-32C ainda não foram totalmente determinadas, mas os contornos aproximados do futuro produto já estão lá. A CPU deve ter um desempenho de pelo menos 1,5 / 3/6 Teraflops para computação FP64 / FP32 / FP16 e conter pelo menos 32 núcleos com uma frequência de mais de 2 GHz. Talvez haja 64 núcleos do E2K de sétima geração. A quantidade de cache L3 deve pelo menos dobrar e o controlador de memória pode receber suporte para DDR5 de pelo menos 4 TB / soquete. Presume-se que pelo menos configurações de dois soquetes podem funcionar.

A virtualização e a tecnologia de computação segura proprietária podem ser mais desenvolvidas com a adição de novas instruções. Os desenvolvedores já desejam fornecer 64 pistas PCIe 5.0, o que abre caminho para o uso do CXL 2.0. Para os controladores integrados, além do NVMe, que é definitivamente indispensável, podem ser adicionados 100GbE e USB 3.1 ou mais recente. Os cristais futuros mudarão para um processo técnico de espessura não superior a 7 nm, e sua área crescerá para 600 mm2.