A União Europeia continua a desenvolver activamente a sua própria visão de supercomputadores num futuro próximo, que se baseará na arquitectura RISC-V. Ao longo de três anos e meio de trabalho, o projeto Marenostrum Experimental Exascale Platform (MEEP) criou uma nova plataforma que descreve detalhadamente os vários blocos e propriedades de tais sistemas HPC.

A escolha da microarquitetura RISC-V como base do MEEP é bastante justificada – ela é aberta e permite que os desenvolvedores não dependam de conjuntos de instruções proprietários e soluções de hardware. Assim, a UE pretende alcançar autonomia no domínio da supercomputação através da aquisição da sua própria plataforma.

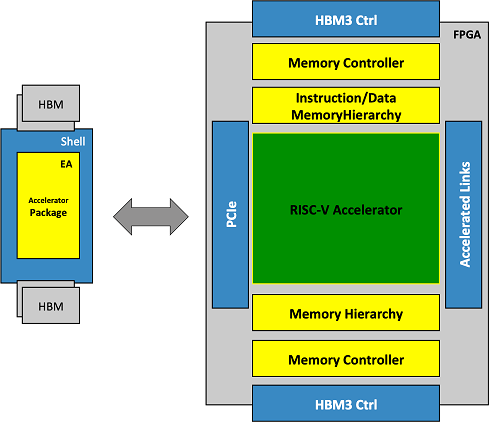

Descrição de alto nível do acelerador emulado

No centro do projeto MEEP está o Accelerated Memory and Compute Engine (ACME), que foi originalmente projetado para usar memória HBM3 de alta velocidade e consiste em Memory Tile e blocos de computação VAS conectados por uma interconexão de malha. A implementação do design ACME em silício real ainda é uma questão de futuro, mas já está claro que os processadores desenvolvidos no projeto MEEP terão um layout de chiplet.

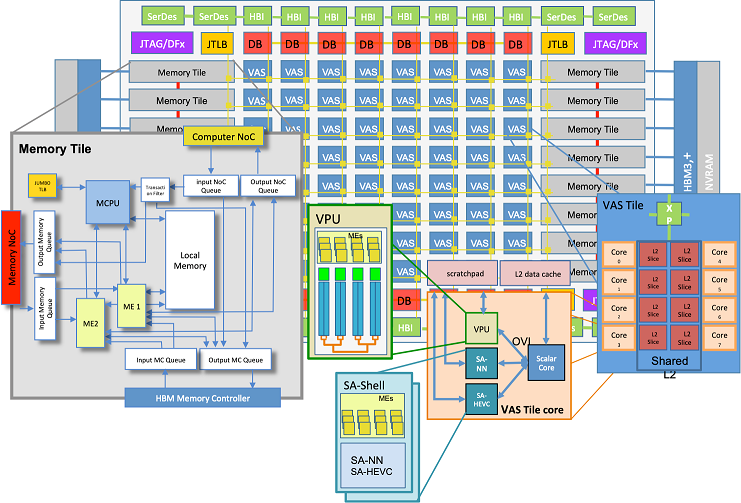

Arquitetura ACME e seus blocos de construção

No projeto ACME, o Memory Tile lida com todas as operações com subsistemas de memória, incluindo a construção de arrays hierárquicos usando diferentes tipos de memória, incluindo MRAM e HBM3. Os módulos VAS incluem 8 núcleos de processador, cada um com suas próprias seções de cache L2. Cada núcleo consiste em vários blocos separados: um RISC-V escalar, um bloco de operações vetoriais, bem como blocos aceleradores de dois tipos – SA-HEVC para processamento de vídeo e SA-NN para tarefas de rede neural, em particular, inferência.

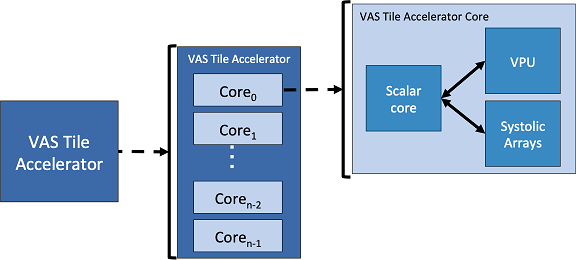

Esquema de operação de aceleradores como parte de blocos VAS

Na verdade, cada módulo VAS é um processador RISC-V multi-core totalmente completo, capaz de trabalhar com todos os formatos de dados modernos, reconhecendo automaticamente instruções avançadas e executando-as utilizando os aceleradores apropriados em sua composição.

A plataforma criada como parte do projeto MEEP já funciona como um protótipo completo emulado usando um FPGA Xilinx. Permite não só desenvolver e depurar software para o novo ecossistema europeu de supercomputação, mas também validar componentes de hardware para futuros aceleradores/processadores com arquitetura ACME.