Mais recentemente, a Samsung Electronics anunciou triunfantemente o início da produção em série de microchips usando padrões de fabricação de 3 nanômetros. A TSMC taiwanesa, cuja participação no fornecimento mundial de semicondutores é muito maior, está melhorando sua própria produção de 3 nm e em breve também estará pronta para enviar aos clientes (incluindo, a propósito, Apple e Intel) as primeiras pastilhas de silício litografadas usando esta tecnologia de processo. Em poucos anos, promete-se ao mundo uma transição para os padrões tecnológicos de 2 nm e sua miniaturização adicional – já para unidades de angstroms (10 Å = 1 nm). Parece realmente inspirador, mas de alguma forma… não físico, ou o quê?

Estruturas de semicondutores em chips modernos são microscópicas, mas ainda não são medidas em unidades de nanômetros (fonte: Unsplash)

⇡#Técnica à beira da fantasia

Agora, se o próximo processo técnico fosse nomeado de acordo com o valor característico do menor elemento semicondutor em termos de dimensões, que pode ser criado usando essa tecnologia, tudo seria simples e óbvio: “22 nm” significa que o tamanho do menor transistor em um microcircuito obtido de acordo com este padrão de produção é igual a 22 nm, “3 nm” significa 3 nm. Simples, conciso, fácil de lembrar.

Infelizmente, mesmo um curso escolar de física dá motivos para duvidar que unidades, e ainda mais décimos de nanômetros – como designações para padrões tecnológicos – tenham um significado físico direto e óbvio. O fato é que hoje os microprocessadores são produzidos em massa usando fotolitografia: grosso modo, eles iluminam um wafer de silício com uma camada sensível à luz por meio de uma máscara de modelo (e um sistema de lentes redutoras). E isso, por sua vez, significa que o tamanho mínimo alcançável de um único elemento em um microcircuito acabado é determinado pelas leis da óptica.

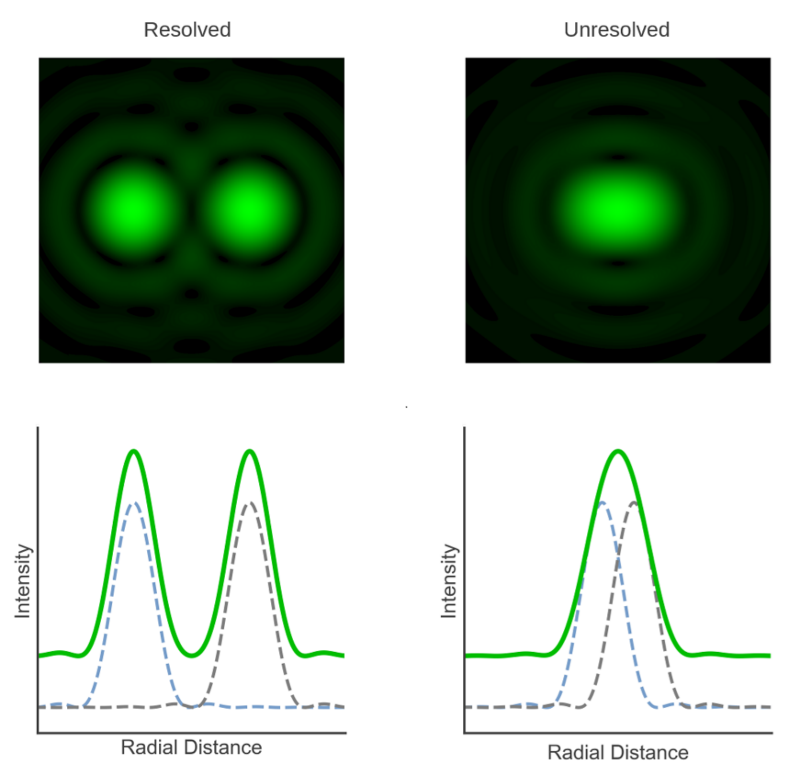

Opticamente resolvidos (resolvidos) em microscopia são dois objetos luminosos pontuais, cuja distância radial (distância radial) entre os picos da intensidade de radiação (intensidade) é grande o suficiente para distingui-los com confiança (fonte: Edinburgh Instruments)

Essas mesmas leis da ótica postulam diretamente a impossibilidade de resolver, ou seja, distinguir com confiança através de um microscópio, detalhes com um tamanho característico inferior a cerca da metade (mais precisamente, do que um coeficiente adimensional na faixa de 0,50 a 0,61) do comprimento de onda usado para iluminar a radiação. Por exemplo, alguns dos melhores microscópios ópticos Nikon do mundo, ao usar luz com comprimento de onda de 650 nm, fornecem uma resolução de 340 nm e, para radiação de 360 nm, o tamanho mínimo de detalhes distinguíveis com confiança não pode ser inferior a 190 nm.

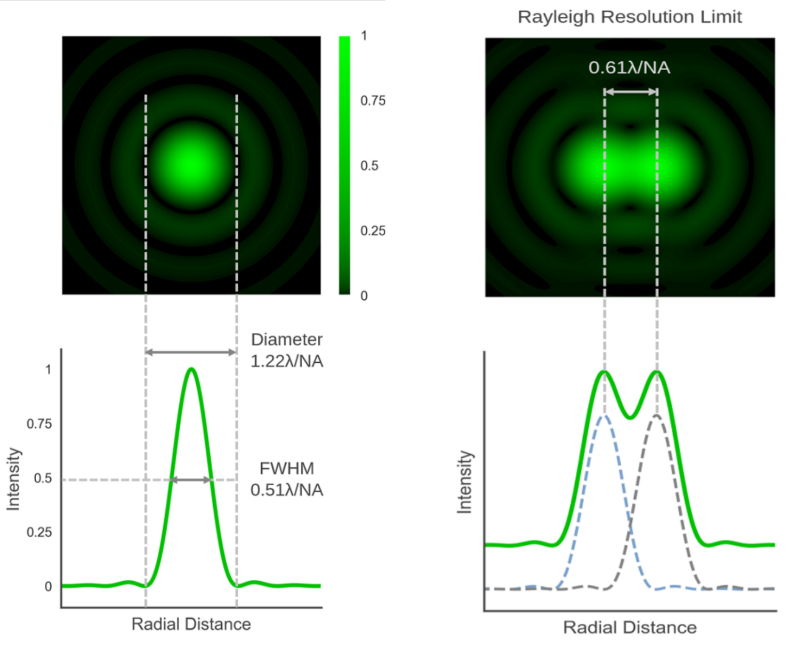

O tamanho mínimo de uma fonte de luz de ponto único é finito devido à difração e depende tanto do comprimento de onda da radiação (λ) quanto da abertura numérica do instrumento óptico (NA). Para duas dessas fontes adjacentes, o critério de Rayleigh é aplicado: a distância entre os centros de fontes de luz resolvidas com confiança não deve ser inferior a 0,61*(λ/NA) (fonte: Edinburgh Instruments)

Os lasers DUV (deep ultraviolet range – deep ultravioleta) com comprimento de onda de 193 nm são amplamente utilizados hoje pelos fabricantes de chips – de 22 a 7 nm. Isso significa que os transistores produzidos usando esses lasers e óptica complexa na superfície de uma pastilha de silício devem ter um tamanho característico de cerca de 100 nm. Se pegarmos o equipamento fabricante de chips mais avançado hoje, operando na faixa do ultravioleta extremo (EUV – ultravioleta extremo) e focado em processos técnicos sob os nomes “5 nm”, “4 nm” e “3 nm”, então ele litografa estruturas semicondutoras usando radiação com comprimento de onda de 13,5 nm – ou seja, as leis da óptica ditam a resolução máxima para ela no nível de 7-8 nm.

Surge uma situação paradoxal, como se um cutelo pesado e sem corte servisse como a principal ferramenta para realizar a mais fina escultura em marfim. Algo claramente não converge aqui: é difícil supor que a designação “x nm” corresponda diretamente ao menor tamanho de algum elemento físico de um microcircuito semicondutor.

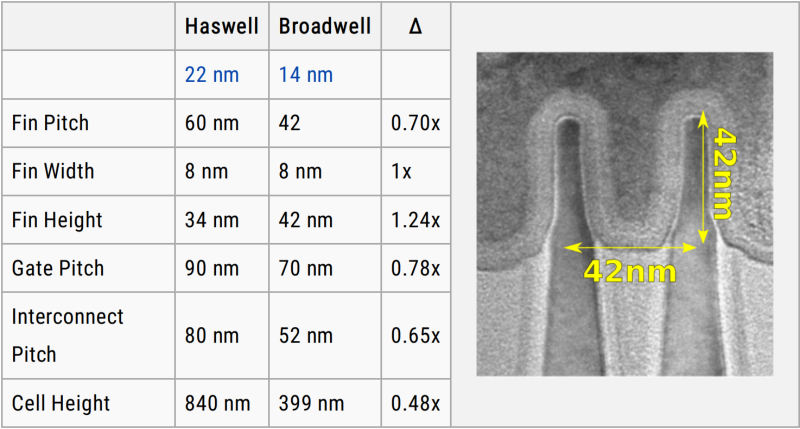

Nos transistores de 14 nm do chip Intel Broadwell, não há um único elemento com um tamanho característico de 14 nm: a largura das cristas (largura da aleta) é de 8 nm, a distância entre as cristas (altura da aleta) é de 42 nm, a altura das cristas (altura da aleta) é a mesma 42 nm, distância entre portas de transistores adjacentes (passo do portão) – 70 nm, distância entre barramentos de conexão (passo de interconexão) – 52 nm, altura da célula do transistor (altura da célula) – 399 nm (fonte: Wikichip)

Para ser justo, notamos que no ano passado a Intel abandonou o uso do termo “nanômetro” para se referir aos seus processos técnicos, mudando “10 nm” para “Intel 7”, “7 nm” para “Intel 4” e assim por diante. E a TSMC está falando cada vez mais sobre as próximas normas de fabricação de 3nm como “processo N3”, evitando também mencionar unidades de medida. E, no entanto, isso não elimina a confusão com nanômetros – em vez disso, até obscurece as fronteiras já difusas entre diferentes normas tecnológicas.

⇡#Carbono e nanômetros

A dúvida de uma interpretação direta de termos de marketing como “3 nm” é claramente ilustrada pelo exemplo a seguir. Em meados de 2022, uma equipe de pesquisadores do Centro Internacional de Nanoarquitetura de Materiais (WPI-MANA) anunciou a criação do primeiro transistor do mundo com um tamanho físico característico (o comprimento do canal pelo qual a corrente flui quando o portão está aberto ) de 2,8 nm. Além disso, este anúncio foi feito quase um mês depois que a Samsung Electronics anunciou o início da produção em série de chips de acordo com os padrões tecnológicos de 3 nm.

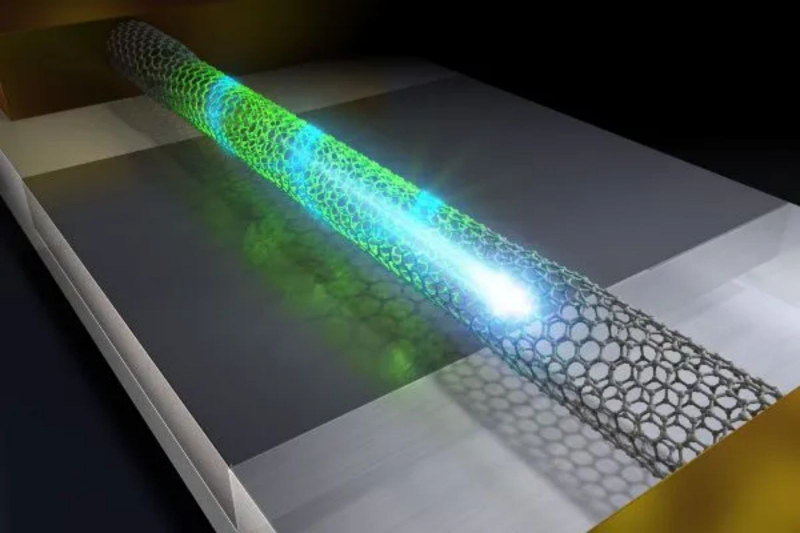

Renderização artística de um transistor de nanotubo de carbono de canal de 2 nm (fonte: WPI-MANA)

A questão é: qual é a essência da inovação de um determinado laboratório de engenharia, se um processo técnico de aproximadamente a mesma classe de miniatura parece já ter sido implementado em uma grande empresa? O fato é que os nanômetros dos pesquisadores do WPI-MANA não são marketing, mas reais. É verdade que esse nível de miniaturização foi alcançado virtualmente à mão, usando os chamados nanotubos de carbono metálico e um microscópio eletrônico de transmissão (TEM).

Essas estruturas de treliça de átomos de carbono são chamadas metálicas porque conduzem eletricidade a baixas temperaturas, como metais comuns. Os nanotubos de carbono semicondutores, por outro lado, perdem suas propriedades condutoras ao serem resfriados. Como exatamente um nanotubo se comportará é determinado pela geometria de suas paredes: desde que seja um cilindro reto e uniforme, a estrutura dos átomos de carbono se comporta como um metal (no sentido de condutividade elétrica), e se o tubo for dobrado , torcido ou comprimido, ele já se comporta como um semicondutor.

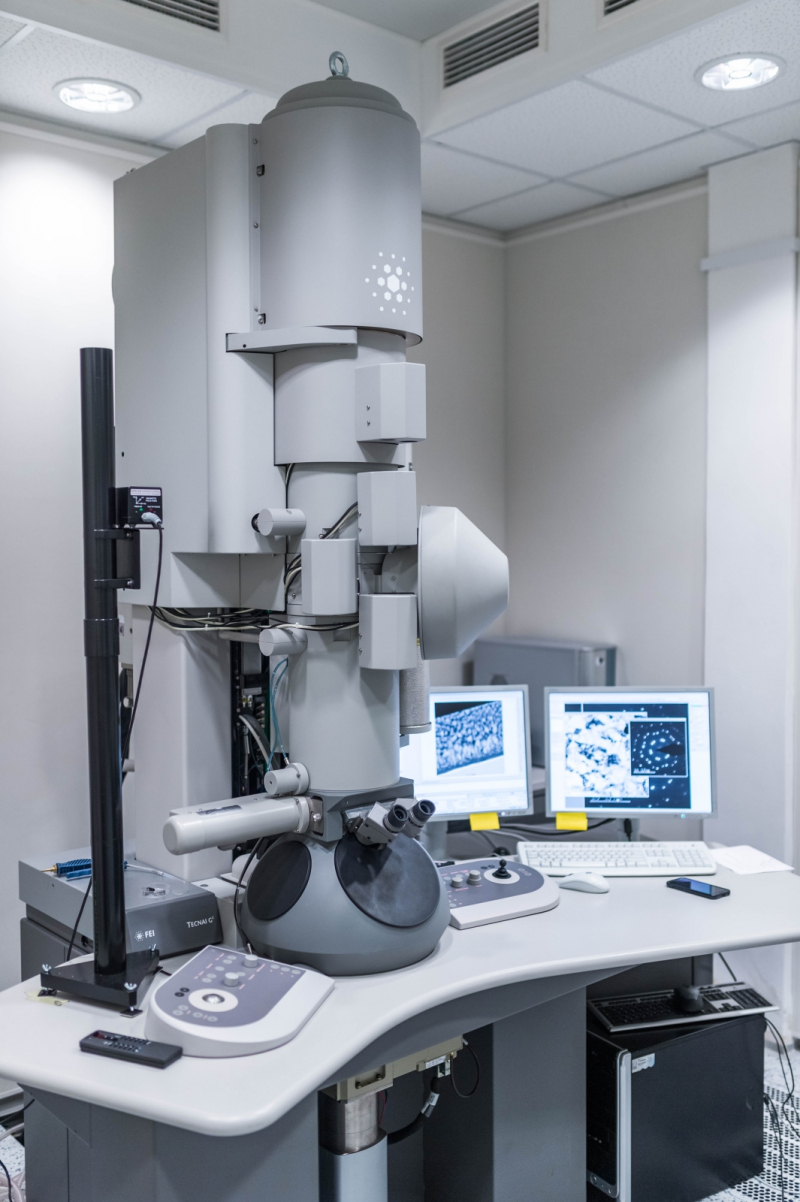

FEI Tecnai TF20 X-Twin TEM no laboratório (fonte: Instituto de Física da Academia Tcheca de Ciências)

Agora está claro por que os engenheiros do WPI-MANA precisavam de um TEM: o princípio de sua operação é passar um feixe de elétrons através de uma amostra fina com sua subsequente focagem e registro. Nesse caso, um feixe de alta energia, é claro, pode afetar diretamente as estruturas irradiadas: em particular, pode deformar as paredes dos nanotubos, que, lembramos, têm exatamente um átomo de carbono de espessura. Como resultado, uma parte do nanotubo inicialmente metálico torna-se semicondutor sob a influência do TEM.

O resto é uma questão de técnica: para obter um transistor de efeito de campo, você precisa de um semicondutor incluído no circuito elétrico e uma porta que controle o estado desse transistor. Apenas um fragmento de um nanotubo de carbono metálico exposto a um feixe de elétrons se torna um canal semicondutor – este é seu comprimento característico, 2,8 nm, indicado no relatório WPI-MANA como o tamanho físico do transistor resultante.

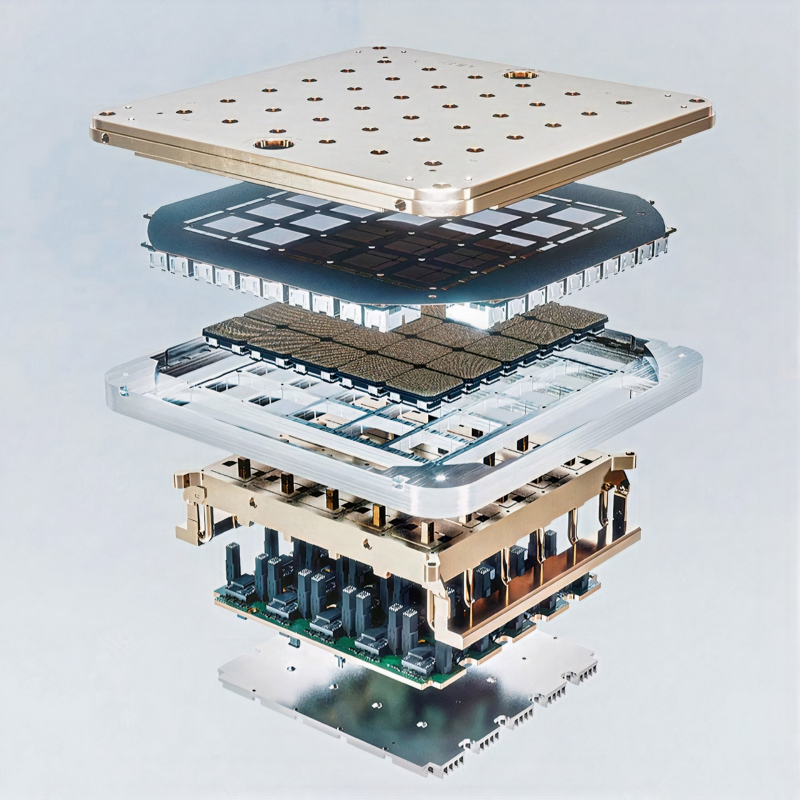

O chip Tesla D1 Dojo contém 50 bilhões de transistores, escala até 10TB/s através do barramento de interconexão e consome até 400W – não é à toa que é tão complexo (fonte: Tesla)

E tudo seria ótimo – aqui está, o cobiçado elemento básico verdadeiramente em nanoescala de um circuito integrado! – mas não esqueça que estamos falando de um experimento de laboratório, e não do desenvolvimento de uma nova tecnologia serial. Como o número de transistores em um processador moderno típico pode chegar a 50 bilhões (por exemplo, muitos deles no chip Tesla D1 lançado em 2021, projetado para resolver problemas de aprendizado de máquina), fabricá-los separadamente usando TEM claramente não é a melhor opção em termos de produção em massa.

Sim, o procedimento pode ser automatizado confiando o comando do microscópio a alguma máquina com controle numérico, mas em princípio isso não aumentará a velocidade. As tecnologias utilizadas pela TSMC, Samsung Electronics, SMIC e outras empresas baseiam-se num princípio diferente, essencialmente análogo: a fotolitografia. E o que neste caso significa a designação da norma de produção “22 nm” ou “7 nm” – segundo este último, aliás, o mencionado processador Tesla D1 foi fabricado – ainda permanece uma questão.

⇡#Brilhe aqui

Como já mencionado, o processo fotolitográfico é muito parecido com a fotografia analógica clássica – daqueles tempos em que as fotografias eram tiradas em placas de vidro. O principal elemento semicondutor na indústria de TI hoje em termos de preço, disponibilidade e desempenho é o silício, razão pela qual o wafer de silício se torna a base da fotolitografia.

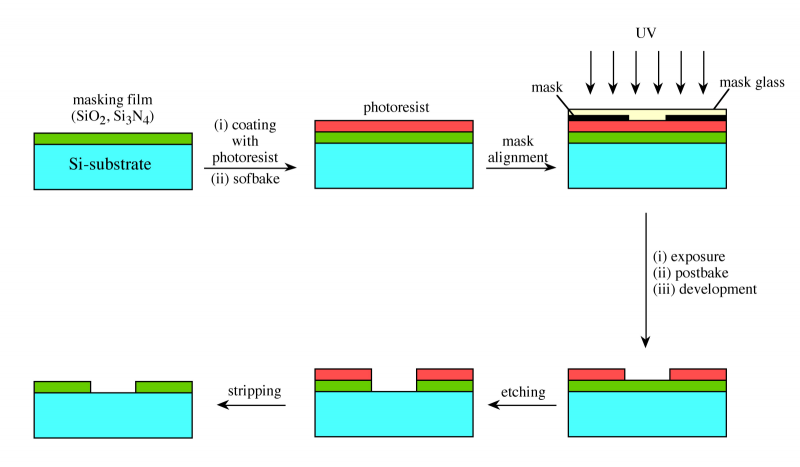

As principais etapas da fotolitografia de semicondutores de contato: preparação de um substrato (filme) sobre um substrato de silício, deposição de um fotorresistente, exposição UV diretamente através de uma máscara, revelação, gravação (gravação) e decapagem do resiste (fonte: OpenStax)

Uma camada de material sensível à luz (fotorresistente) é aplicada em sua superfície, então essa camada é exposta a um fluxo de luz que passa por uma máscara (fotomáscara) – desenhando a estrutura de um futuro circuito eletrônico. As máscaras de hoje são muito maiores (em escala) do que as estruturas semicondutoras de silício finais – então a iluminação é produzida através de um sistema de lentes redutoras.

O complicado, complexo e caro sistema de lentes das modernas máquinas litográficas combate com sucesso a luz de fundo e a difração e, graças a incríveis truques técnicos, permite alcançar uma resolução física não da metade, mas de cerca de um quarto do comprimento de onda da radiação usada. As áreas iluminadas do revestimento alteram suas propriedades físicas e são lavadas com produtos químicos especiais. Assim, a primeira camada do futuro circuito integrado ultra grande (VLSI) é formada.

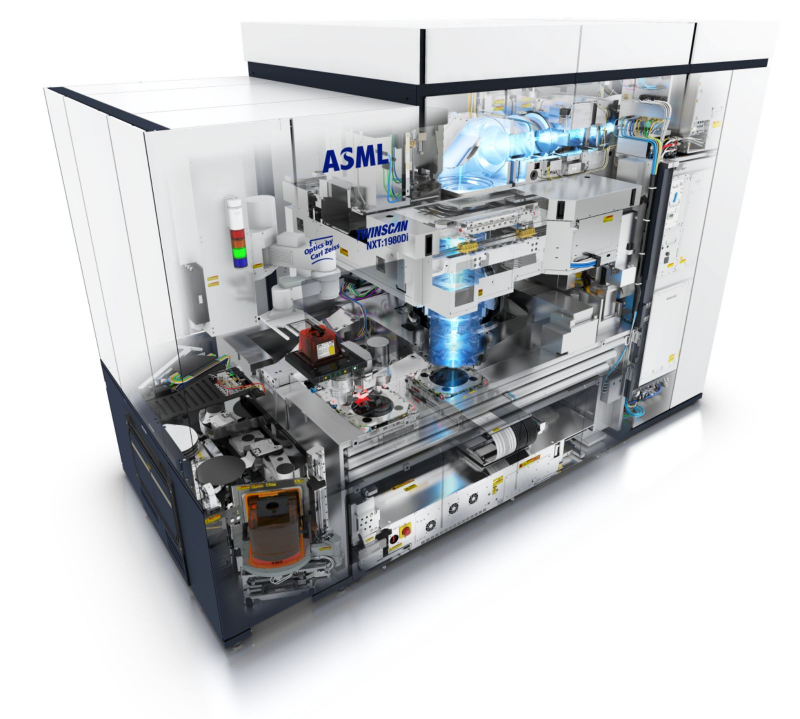

Fotolitografia TWINSCAN NXT 1980Di: um diagrama da passagem da luz através de um complexo sistema de lentes. A máscara aqui está abaixo do espelho, que muda a direção do fluxo de luz para horizontal, e a pastilha de silício exposta é colocada abaixo (fonte: ASML)

O assunto não se limita a uma exposição: para formar até mesmo um transistor de efeito de campo separado, é necessária uma camada de substrato dielétrico, uma camada com uma porta de controle, o próprio canal semicondutor, interconexões metálicas … ciclo próprio de aplicação de fotorresistente, iluminação e lavagem; bem, e sua fotomáscara, ou até mais de uma. E isso é apenas para microcircuitos clássicos de nível único, enquanto o VLSI essencialmente multicamada, como os atuais chips de memória flash 3D NAND, pode conter menos de 200 ou até mais níveis de células de transistor totalmente funcionais.

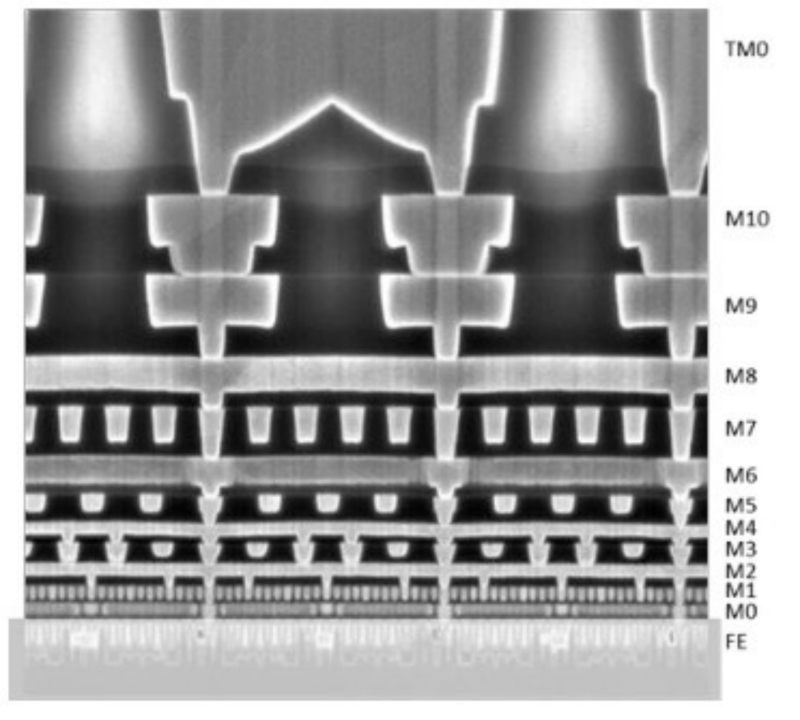

«O processo de 10nm da Intel, agora chamado de “Intel 7”, prevê a formação de 11 camadas de metal no substrato (de M0 a M10). As interconexões de transistores através dessas camadas formam elementos funcionais (por exemplo, o circuito NAND), e a partir deles, por sua vez, são formadas estruturas maiores (por exemplo, um somador aritmético). Mais duas camadas de metal, TM0 e TM1 (a última não mostrada na foto) fornecem acesso aos pinos do processador e comunicação entre a CPU e a lógica do sistema (fonte: Intel)

Aqui vale a pena desviar um pouco da busca de significado físico nas designações de marketing de nanômetros para processos tecnológicos e fazer uma pergunta igualmente importante: por que os fabricantes de chips vêm investindo dezenas e centenas de bilhões de dólares na contínua miniaturização de normas tecnológicas para décadas? De fato, por si só, a transição de uma tecnologia de processo para outra não garante um aumento imediato no desempenho absoluto da CPU.

Ao mesmo tempo, a redução progressiva dos padrões tecnológicos não é um prazer barato. Uma fotolitografia EUV moderna da empresa holandesa ASML custou aos clientes no início de 2022 cerca de 200 milhões de dólares (hoje, presumivelmente, ainda mais caro). Por que cercar um jardim tão caro?

⇡#O ensino de Moore é onipotente, mas há uma nuance

O ponto principal, é claro, é a viabilidade econômica: quanto menor o tamanho de um único transistor, maior a densidade de estruturas semicondutoras na superfície do futuro chip. Quando, em 1965, Gordon Moore, então diretor de pesquisa e desenvolvimento da Fairchild Semiconductor, formulou sua famosa regra prática, agora conhecida como “Lei de Moore”, ele declarou diretamente: “O custo de um elemento semicondutor com precisão considerável é inversamente proporcional ao número de componentes no VLSI “.

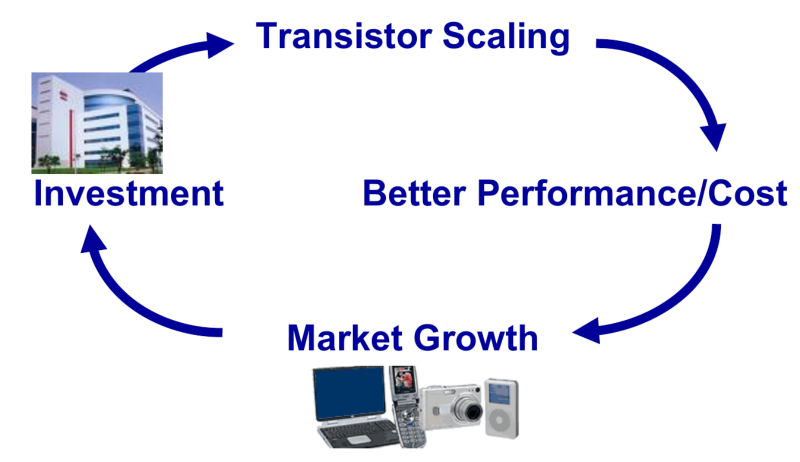

Um gráfico incrivelmente simples do relatório regular do ITRS que demonstra claramente como a profecia de Gordon Moore está se tornando realidade: novos investimentos permitem novas maneiras de miniaturizar processadores, novas CPUs fornecem ganhos de desempenho para cada dólar gasto nelas, o mercado de dispositivos baseados nessas CPUs está em expansão, o que proporciona um fluxo adicional de investimentos – e tudo se repete novamente (fonte: ITRS)

Em outras palavras, se o número de transistores em um microcircuito serial dobrar aproximadamente a cada dois anos, o custo desse chip para o fabricante permanecerá aproximadamente no mesmo nível – enquanto vendê-lo por motivos bastante objetivos pode ser muito mais caro. E sem clientes trapaceiros: mais transistores no VLSI – mais operações por segundo (para CPU e GPU), maior densidade de armazenamento (para memória flash) e até a eficiência energética é muito melhor do que antes, pois elementos semicondutores menores não precisam de alta tensão.

Situação incrível: todos ganham! Projetistas de chips, fabricantes de chips, fornecedores de hardware para a indústria, programadores de todas as faixas, distribuidores e fornecedores – e, finalmente, usuários finais que obtêm todo esse esplendor (incluindo novos softwares que não seriam práticos para serem executados no hardware antigo).

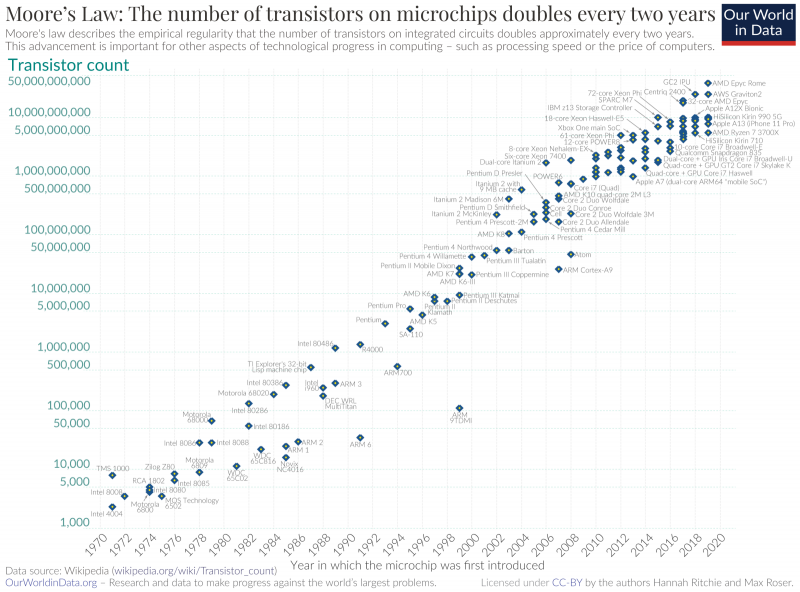

Uma representação visual da “lei de Moore”: horizontalmente – anos, verticalmente – o número de transistores em um chip de CPU (escala logarítmica), cada ponto – um ou outro processador (fonte: OurWorldInData)

Cada novo estágio de progresso tecnológico em microeletrônica enriquece alguns, oferece oportunidades ainda mais amplas para outros e simplesmente permite que outros façam o que amam por uma taxa decente. Não é de surpreender que ao longo do último meio século ou mais, a digitalização de tudo e de todos tenha se desenvolvido tão rapidamente: quanto mais áreas potenciais de aplicação da tecnologia da computação, mais amplo o mercado de microcircuitos – e mais lucrativo é para todos os envolvidos no seu desenvolvimento, produção, venda e utilização, para que a lei de Moore continue a ser respeitada.

Na verdade, havia todos os pré-requisitos para transformar o padrão empírico observado por Gordon Moore em uma profecia auto-realizável: em meados da década de 1960, uma vez por ano, e cerca de dez anos depois, uma vez a cada dois anos, o número de transistores em os microcircuitos mais avançados do momento estavam destinados a dobrar. Acabou sendo tão economicamente justificado que, sob a “Lei de Moore”, foram feitos planos para expandir a produção e equipamentos de semicondutores para eles, o momento do lançamento de novos chips foi planejado e as metas foram estabelecidas para os departamentos de vendas.

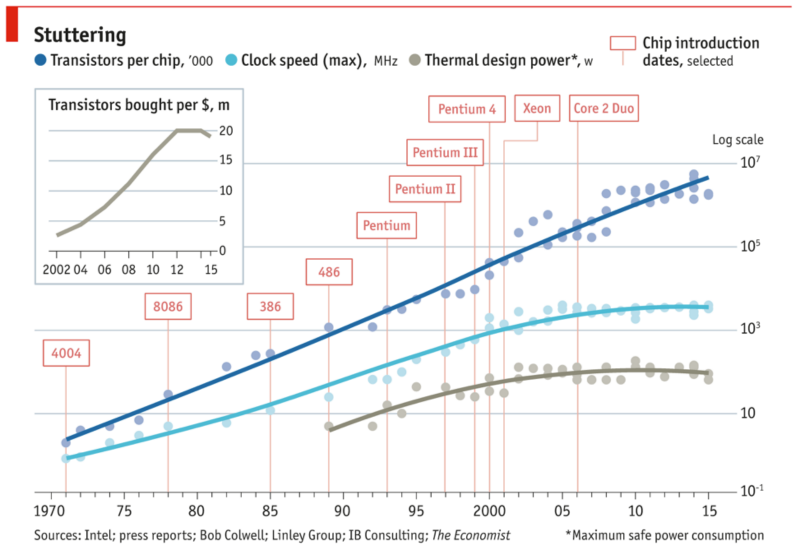

Outro olhar para a lei de Moore: é especialmente claro como, no contexto do número ainda bastante crescente de transistores, desde meados da primeira década dos anos 2000, tanto a frequência do clock operacional quanto o consumo de energia da CPU, e o número de transistores comprados por dólar (ver gráfico inserido) e começou a cair desde 2014 (fonte: ARTIS Ventures)

Infelizmente, a partir de tempos relativamente recentes, a física começou a se destacar: as dimensões dos transistores individuais se aproximaram muito perigosamente do limite que separa o macrocosmo familiar do campo dos efeitos quânticos, que obedece a leis completamente diferentes. Por volta de 2012, o indicador econômico mais importante para toda a indústria de TI parou de crescer – o número de transistores (como parte do chip atual) que podem ser comprados por um dólar e, no início dos anos 2000, as frequências máximas de clock dos processadores realmente atingiram um platô e seus pacotes de calor sob carga regular.

⇡#Adeus ao sentido físico

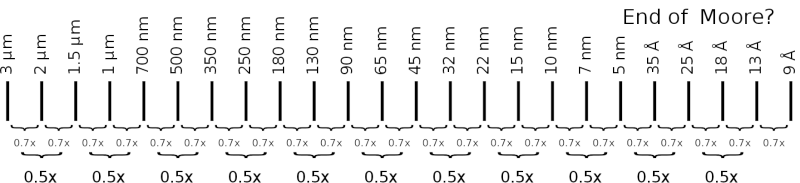

No entanto, a “lei de Moore” na formulação de 1975 mais ou menos continuou a ser cumprida pelo menos até 2019 (quando, em particular, o chefe da NVIDIA anunciou sua iminente desactualização). Se tomarmos o tamanho da CPU mais avançada em cada geração como um valor constante, dobrar o número de transistores neste chip – por exemplo, há um número igual deles horizontal e verticalmente – corresponderá a uma diminuição na característica dimensões de cada um deles em cerca de 0,7 vezes (o inverso da raiz quadrada de dois).

Profecia auto-realizável em ação: o passo inexorável da “lei de Moore” obedece à regra 0,7 – pelo menos deve obedecer para garantir que o ciclo de investimento seja retomado repetidamente (Fonte: WikiChip)

Na verdade, é por isso que a série numérica de nomes de padrões tecnológicos nas últimas décadas tem exatamente esta forma: 90 nm – 65 nm – 45 nm – 32 nm – 22 nm – 15 nm … , os processos de produção em microeletrônica foram, de fato, nomeados de acordo com as dimensões físicas do menor elemento semicondutor que esse processo poderia produzir. Ou seja, ao longo do comprimento da porta (porta) do transistor de efeito de campo.

Curiosamente, em 1997, a Intel deliberadamente buscou um aumento formal na classificação declarada da tecnologia de processo em comparação com as dimensões reais dos dispositivos semicondutores obtidos com seu uso. O processo, que recebeu o nome de marketing “0,25 mícron” ou “250 nm”, possibilitou a fabricação de transistores com comprimento de porta de 0,20 mícron – quase 20% menor que o alegado. O próximo padrão de produção, “180 nm”, também possibilitou a obtenção de transistores com um comprimento de porta menor – 0,13 mícron.

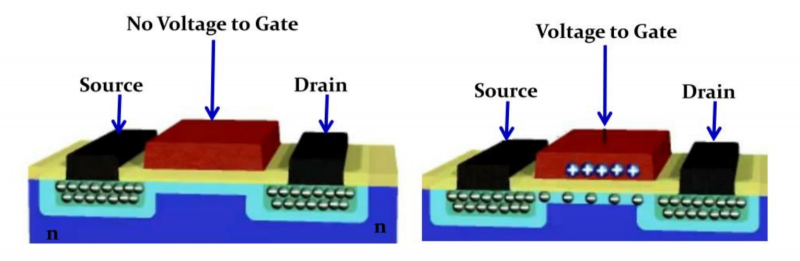

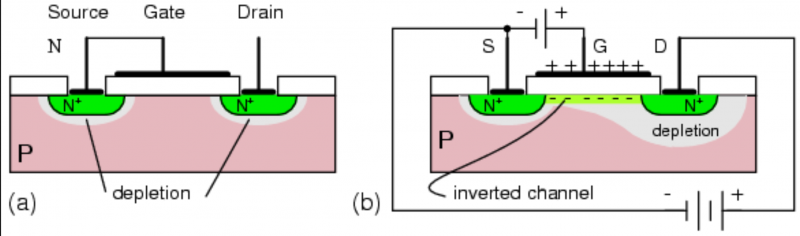

O esquema do transistor de efeito de campo. Esquerda: nenhuma tensão é aplicada à porta (fonte), então a fonte (fonte) e o dreno (dreno) são isolados; não há corrente. Direita: A aplicação de uma tensão a um semicondutor cria um canal condutor da fonte ao dreno. (Fonte: Georgia Institute of Technology)

Isso foi feito, é claro, não por modéstia, mas para garantir que a “lei de Moore” ainda seja respeitada sem problemas, sem desvios – até mesmo em excesso – o que mais uma vez enfatiza o caráter autorrealizável dessa tecnologia “profecia”. Aliás, é por isso que a recente renomeação da tecnologia de processo formalmente “10nm” da Intel para “Intel 7”, “7nm” para “Intel 4” e assim por diante, que mencionamos acima, tem uma justificativa completamente lógica: a empresa simplesmente compensa a vantagem dada antes aos seus rivais, retornando ao ritmo geralmente aceito de mudança nos padrões de produção.

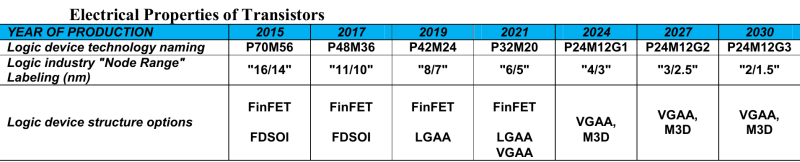

O Conselho Representativo de Especialistas VLSI (que incluiu representantes das associações regionais da indústria de semicondutores – japonês, americano, europeu, taiwanês, sul-coreano e chinês continental) até 2015 atualizou regularmente uma espécie de guia – mais precisamente, um conjunto de recomendações – sobre o desenvolvimento de tecnologia de semicondutores, The International Technology Roadmap for Semiconductors (ITRS). A última edição deste código indica claramente a natureza puramente mercadológica do nome dos padrões tecnológicos: na tabela com previsões para o desenvolvimento de VLSI lógico até 2030, há uma linha “Marcando o“ padrão de produção ”de dispositivos semicondutores” – isso é certo, entre aspas. E entre aspas estão os nomes tanto da norma atual “16/14 nm” na época, quanto das futuras: “11/10”, “8/7” e assim por diante.

Trecho da tabela com as previsões das características elétricas dos próximos processadores, publicada no relatório regular do ITRS de 2015 (fonte: ITRS)

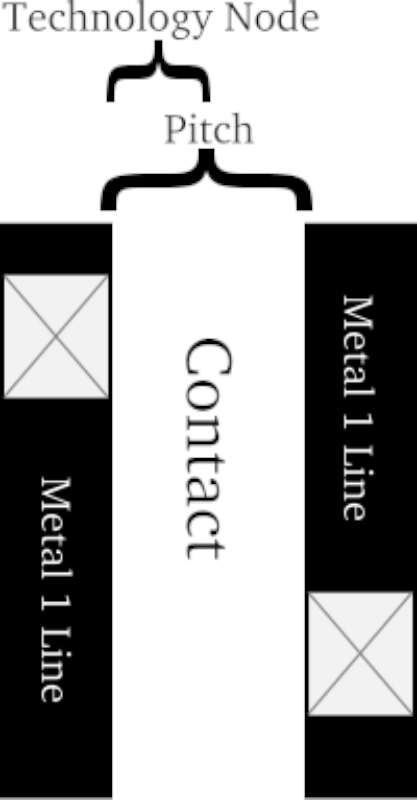

Inicialmente, em termos de ITRS, a norma de produção (nó de processo) foi definida como o menor half-gap (meio passo) entre pistas metálicas de contato no nível mais baixo de um chip semicondutor fabricado pelo método de fotolitografia. O significado físico nesta definição pode ser rastreado: para o VLSI como um todo, não são as dimensões de seus elementos individuais que são importantes em si mesmos, mas a capacidade de separar com confiança condutores (pistas) e semicondutores (transistores) para que ambos funcionem corretamente corretamente.

O significado inicial de definir a escala de taxa de produção como metade da largura do espaço entre trilhos de metal adjacentes no nível mais baixo do chip (os retângulos riscados indicam os contatos que conectam essa camada com os sobrejacentes) é simples e óbvio (fonte: WikiChip)

No entanto, já começando com a tecnologia de processo de 45 nm introduzida em 2007, tivemos que dizer adeus ao significado físico. Foi então que os engenheiros da Intel criaram um transistor planar tradicional com um comprimento de porta de 25 nm – e, além disso, como se viu, não é possível reduzir esse tamanho. Se você não mudar do silício para outros semicondutores, é claro, mas isso significa uma reestruturação radical de toda a indústria de microprocessadores, para a qual os principais players definitivamente ainda não têm determinação nem dinheiro.

⇡#Precisa de menos angstroms

Vamos deixar de lado por enquanto a questão de como exatamente obter um elemento semicondutor de 25 nm em uma pastilha de silício usando um laser de 193 nm (isso não é fácil, mas fisicamente alcançável) e explicar por que 25 nm é um limite intransponível para o tamanho de uma porta de transistor.

É tudo uma questão de física: para que um dispositivo semicondutor funcione como deveria, é necessário evitar a quebra elétrica de seu portão no estado fechado. Por uma série de razões, é impossível para um semicondutor à base de silício (mesmo com vários aditivos que melhoram suas propriedades) reduzir a tensão de operação, encurtar o comprimento da porta e aumentar a concentração de impurezas que impedem a passagem espontânea de carga através do canal (avaria).

Os efeitos quânticos geram uma corrente de tunelamento nos limites entre a base semicondutora do transistor (com condutividade p) por um lado e sua fonte/dreno (com condutividade tipo n) por outro. Como resultado, o comprimento do canal ativo (o transistor funciona – imagem à direita) torna-se menor que a distância física entre os limites da fonte e do dreno devido à formação de zonas ao redor deles esgotadas de cargas negativas, uma vez que a tensão para o portão é aplicado positivo. Se a distância da fonte ao dreno for muito pequena, as zonas de esgotamento se fecham – ocorre uma quebra da base (fonte: LearningChips)

Se você não entrar em detalhes elétricos, então para transistores de efeito de campo, nos quais todos os microeletrônicos de silício modernos são baseados, o comprimento efetivo do canal é menor que a distância física entre a fonte e o dreno de carga. Ou seja, embora o canal de um transistor feito em uma fotolitografia realmente se estenda a uns honestos 25 nm, de fato, quando a porta é ativada, os elétrons percorrem uma distância muito menor – principalmente devido à difusão de impurezas que formam a fonte e drenar na superfície do wafer de silício, na espessura deste último.

Em outras palavras, depois que o comprimento do canal realmente atingiu 25 nm no estágio de tecnologia de processo de 45 nm, a nomenclatura de tecnologia de processo ITRS não correspondia mais à metade da largura do intervalo entre as trilhas de contato – e o nome de marketing do padrão tecnológico subsequente , começando com “32 nm”, foi obtido simplesmente multiplicando o anterior por 0 ,7 com arredondamento.

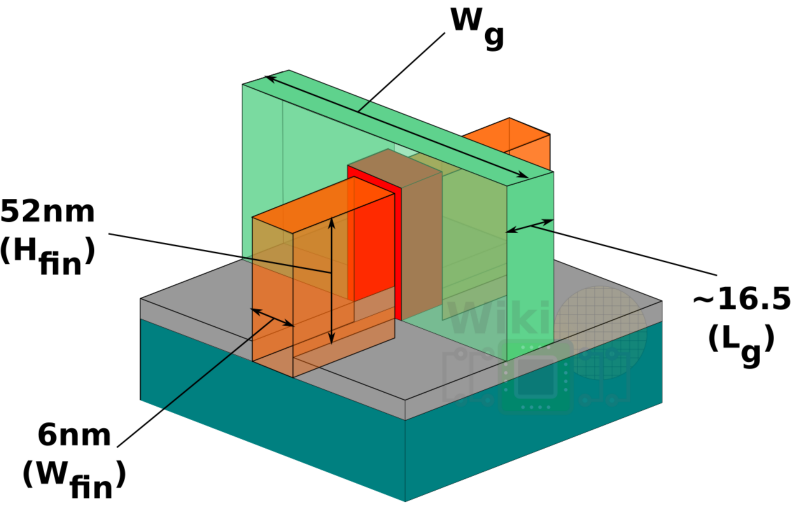

As principais dimensões do transistor “7-nm” TSMC: altura do pente (Hfin) – 52 nm, largura do pente (Wfin), comprimento do portão (Lg) – 16,5 nm (Fonte: WikiChip)

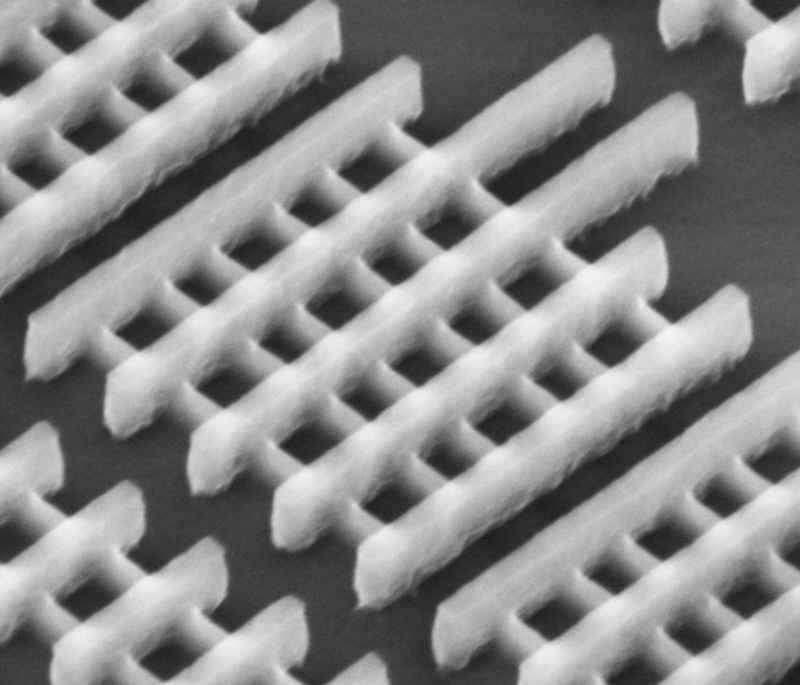

No estágio de 22 nm, as coisas ficaram ainda mais interessantes: então, em 2012, a Intel usou pela primeira vez transistores FinFET tridimensionais com canais em pente, ou aletas. A área de contato entre a porta e o canal com esta configuração é significativamente aumentada em comparação com a configuração planar, o que permite tornar os transistores muito mais estreitos – enquanto o comprimento físico da porta continua sendo um pouco menor que 20 nm, mesmo para a fabricação processo com o nome de marketing “7 nm”.

É por isso que, depois de 2012, o nome da norma de produção em microeletrônica, de fato, não tem mais uma conexão real com nenhuma dimensão física de elementos individuais na superfície de um cristal semicondutor. A taxa de introdução de novos processos técnicos é mais ou menos mantida – no entanto, nos últimos anos, por razões objetivas, ficou um pouco atrás da única mudança em dois anos declarada na lei de Moore. O curso para dobrar o número de transistores nos microcircuitos mais recentes é aproximadamente mantido, e o nome de marketing do próximo novo padrão é obtido multiplicando sem artifício o nome do anterior por 0,7.

Estruturas de transistores FinFET com sulcos característicos (o comprimento mínimo do canal – onde os sulcos se cruzam com as portas – é, de acordo com a especificação oficial, 25 nm) na superfície da matriz “22-nm” Intel Sandy Bridge (fonte: Intel )

«Antigamente era a designação de um estágio tecnológico, tinha algum significado, tinha a ver com algo realmente existente na superfície da placa. Hoje os números são apenas números. Como, você sabe, marcas de carros: há um BMW da quinta série ou um Mazda 6 – qual é o sentido desses cinco e seis? Não importa a que nome da norma de produção corresponda agora, é apenas mais um marco no desenvolvimento da tecnologia, seu nome, se preferir. Portanto, não nos enganemos e tentemos comparar diretamente os nomes dos processos técnicos com as características físicas dos dispositivos semicondutores que eles permitem receber.

Tal conselho foi dado em 2019 por Philip Wong, vice-presidente de Pesquisa Corporativa da TSMC, para o público da 31st Hot Chips Conference, uma das plataformas mais representativas para discussões entre representantes da indústria global de microprocessadores. Então a empresa taiwanesa estava apresentando seus processos técnicos promissores N7, N5, N3.

Agora a IBM já criou o primeiro chip semicondutor do mundo de acordo com a norma de produção de “2 nm” (embora não muito diferente na densidade do transistor do processo TSMC N3 – 333 milhões de unidades por polegada quadrada para o primeiro versus 292 milhões para o último) . A Intel programou o lançamento de seu próprio processo 20A (“A” indica o comprimento de marketing em angstroms) para 2024. A TSMC está trabalhando com força e força nos padrões de produção não apenas para N2, mas também para N1.

Assim, mesmo tendo em conta a atual situação extremamente difícil com o fornecimento de máquinas litográficas e outros equipamentos para a produção de chips, não há dúvida de que a “Lei de Moore”, ainda que de forma ligeiramente corrigida, continuará a ser uma estrela guia para toda a indústria de microprocessadores por muito tempo. Mesmo que os marcos que marcam seu desenvolvimento não tenham mais um significado físico.