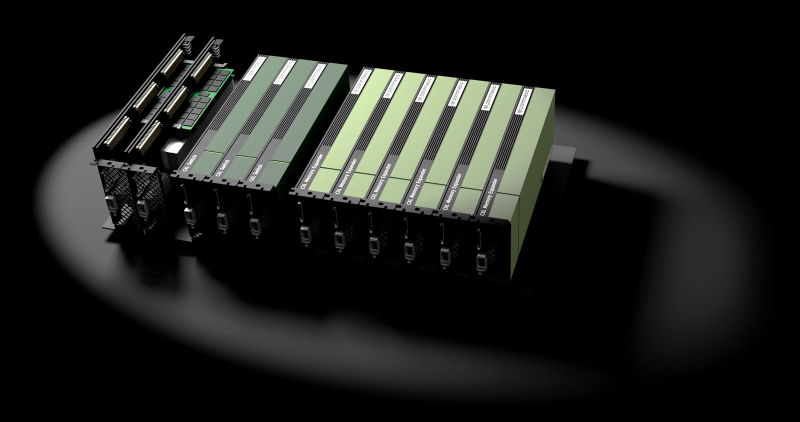

A Panmnesia vem projetando pools CXL DRAM há algum tempo: em 2023, ela demonstrou um sistema que deixa para trás todas as soluções baseadas em RDMA e fornece acesso a 6 TB de RAM. Mas grandes quantidades de memória hoje, numa era de modelos de IA cada vez mais complexos, são necessárias não apenas e nem tanto pelos processadores, mas pelos aceleradores, que são a priori privados da capacidade de atualizar a RAM integrada. Na CES 2025, a empresa demonstrou uma solução para este problema.

De acordo com os desenvolvedores da Panmnésia, o desempenho no treinamento de modelos de IA em grande escala depende precisamente do volume de memória on-board dos aceleradores: em vez de dezenas de gigabytes, são necessários terabytes, e a instalação de aceleradores adicionais pode ser muito cara, visto que a computação a energia será redundante.

Fonte aqui e abaixo: Panmnésia

O sistema CXL demonstrado na exposição é construído no mais recente controlador Panmnesia com suporte para CXL 3.1. No modo bidirecional, a latência de acesso foi inferior a 100 ns e é de aproximadamente 80 ns.

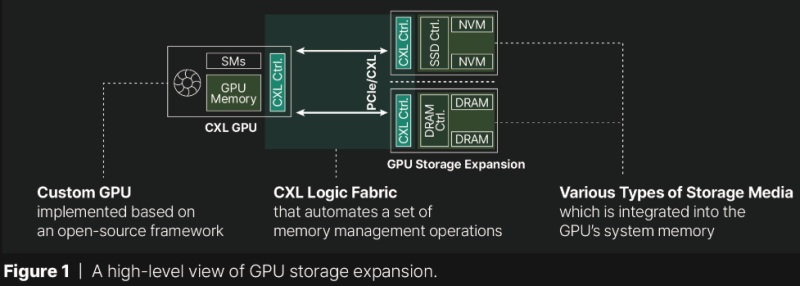

A chave para o sucesso aqui está na implementação proprietária do CXL 3.1, incluindo a parte de software, graças à qual as GPUs podem acessar um pool de memória compartilhada usando as mesmas instruções de carregamento/armazenamento como ao acessar HBM ou GDDR integrado.

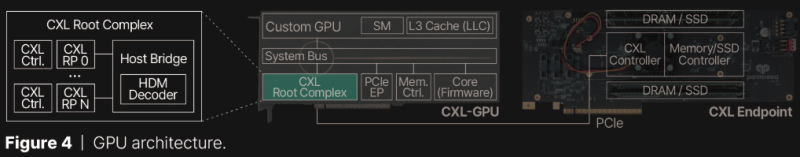

No entanto, a tecnologia requer um controlador CXL Root Complex proprietário a bordo da GPU, uma das partes mais importantes do qual é o decodificador HDM, responsável por gerenciar o espaço de endereço da memória (endereço físico do host, HPA), portanto, aceleradores já lançados não poderá trabalhar diretamente com o sistema da Panmnésia.

No entanto, a tecnologia parece promissora. Já atraiu a atenção de empresas de IA como uma forma potencial de reduzir o custo da infraestrutura de data centers.